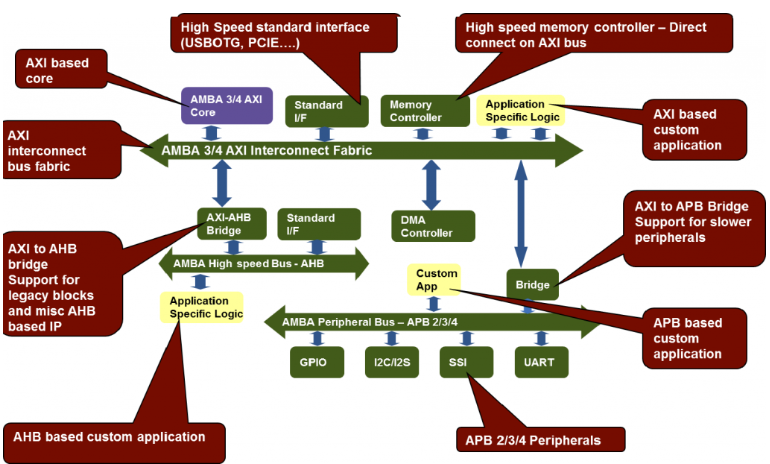

用于片上系統(tǒng) (SoC) 中功能塊連接和管理的 ARM? AMBA4? 規(guī)范現(xiàn)在具有支持多核計(jì)算的高級可擴(kuò)展接口 (AXI) ? 一致性擴(kuò)展 (ACE ?)。ACE 規(guī)范支持跨多核處理器群集的系統(tǒng)級緩存一致性。在規(guī)劃此類系統(tǒng)的功能驗(yàn)證時(shí),這些一致性擴(kuò)展帶來了自己的復(fù)雜挑戰(zhàn),例如系統(tǒng)級緩存一致性驗(yàn)證和緩存狀態(tài)轉(zhuǎn)換驗(yàn)證。在任何給定時(shí)間,驗(yàn)證 ACE 互連是否可以在系統(tǒng)中的不同 ACE 主節(jié)點(diǎn)之間保持緩存一致性非常重要。隨著硬件中的一致性支持以及相關(guān)的支持協(xié)議,系統(tǒng)和底層組件的復(fù)雜性大大增加。因此,這種系統(tǒng)的核查面臨若干挑戰(zhàn)。讓我們掌握對激勵(lì)生成基礎(chǔ)設(shè)施的要求,以驗(yàn)證緩存一致性系統(tǒng)。

基于 AMBA ACE 互連的系統(tǒng)可以通過相干互連連接各種主站和從站。每個(gè)主組件和從組件都可以單獨(dú)支持完整的 ACE、ACE-Lite?、AXI4? 或 AXI3? 協(xié)議,并且可以使用不同的總線寬度或時(shí)鐘頻率。不同的排列涉及以下參數(shù):緩存狀態(tài)、事務(wù)類型、突發(fā)長度和大小、偵聽機(jī)制、偵聽緩存狀態(tài)、偵聽響應(yīng)、對推理獲取的支持、對偵聽過濾的支持以及用戶指定的互連調(diào)度。

所有這些交叉組合導(dǎo)致了非常大的驗(yàn)證空間,從而產(chǎn)生了四個(gè)關(guān)鍵挑戰(zhàn):

生成映射到所有這些的激勵(lì)包括,確保每個(gè)單獨(dú)的主、從或互連與其支持的協(xié)議完全兼容;

確保啟動主存儲器、偵聽主存儲器和從主存儲器之間所有可能的并發(fā)訪問組合都經(jīng)過驗(yàn)證,并符合ACE規(guī)范;

確保涵蓋所有用戶特定的功能并按預(yù)期工作;和

確保核查的完整性

您如何創(chuàng)建一個(gè)可以處理所有這些的刺激發(fā)電基礎(chǔ)設(shè)施?

在這里,我們嘗試向您展示如何做到這一點(diǎn)?這個(gè)想法是確保您擁有所有正確的構(gòu)建塊,并逐步組織它們并將它們拼接在一起以獲得您需要的東西。

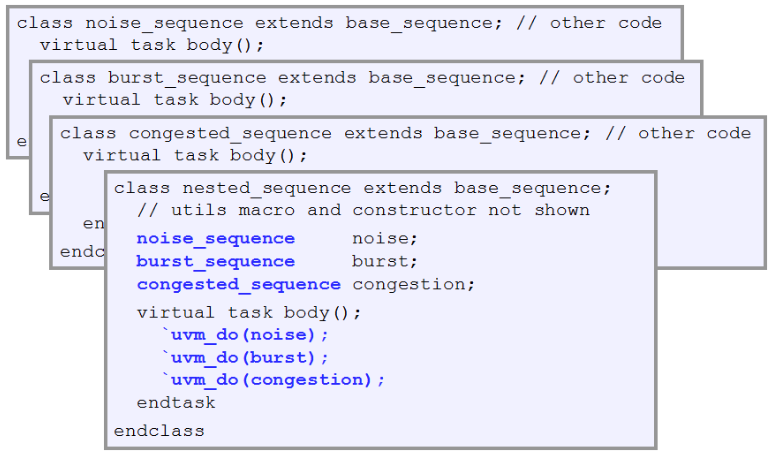

我們在VC驗(yàn)證IP(VIP)中所做的非常相似:我們從一些久經(jīng)考驗(yàn)的原生SystemVerilog UVM原子序列開始,并逐步轉(zhuǎn)向創(chuàng)建復(fù)雜的序列。鑒于 UVM 提供的功能,將低級、經(jīng)過驗(yàn)證或驗(yàn)證的方案拼接在一起以創(chuàng)建更復(fù)雜的方案要方便得多。無需在序列主體中創(chuàng)建扁平化實(shí)現(xiàn),可以創(chuàng)建分層或嵌套序列以利用之前創(chuàng)建的基本序列。這可以上升到多個(gè)層次結(jié)構(gòu)級別,因此可以收斂以滿足最復(fù)雜方案的要求。

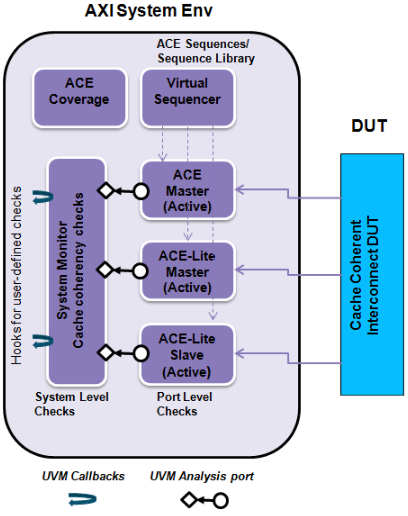

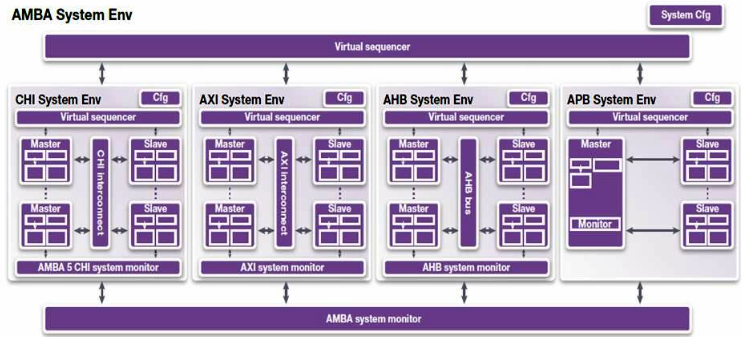

隨著多個(gè) ACE 組件的復(fù)雜性增加,可能需要跨多個(gè)序列器和驅(qū)動程序協(xié)調(diào)序列。這些都是通過虛擬序列和序列器實(shí)現(xiàn)的。從刺激生成的角度來看,另一個(gè)重要功能是序列的分組和分層序列的創(chuàng)建。在UVM中,相似的序列可以組合到一個(gè)序列庫中。使用 UVM 基類,您可以創(chuàng)建庫基礎(chǔ)結(jié)構(gòu),該基礎(chǔ)結(jié)構(gòu)允許通過庫 API 將任何序列注冊到序列庫。在仿真中選取庫后,默認(rèn)功能會導(dǎo)致選取并執(zhí)行隨機(jī)數(shù)量的序列。因此,AXI VIP附帶的序列庫可以用作滿足用戶要求的起點(diǎn)。

可以通過更改關(guān)聯(lián)配置類的參數(shù)來修改序列庫的默認(rèn)模式。因此,可以拾取特定數(shù)量的序列,啟用隨機(jī)循環(huán)序列,以及編程用戶定義的序列執(zhí)行。

為序列庫創(chuàng)建自定義規(guī)則不僅有助于簡化不同仿真中的多個(gè)序列,還有助于避免冗余,并逐步實(shí)現(xiàn)所有有趣的系統(tǒng)級場景的融合。因此,無需編寫多個(gè)測試,我就可以通過虛擬序列器跨多個(gè)序列庫、跨不同接口創(chuàng)建自定義序列執(zhí)行,從而生成激勵(lì)管理設(shè)置,有助于更快地滿足所有激勵(lì)生成要求。在某些情況下,序列必須知道功能配置,以便根據(jù)系統(tǒng)級要求進(jìn)行重新配置。VC VIP 利用 UVM 資源機(jī)制提供的大部分功能,在 ACE 環(huán)境中提供可配置性和復(fù)雜的激勵(lì)生成要求。通過資源機(jī)制啟用的可配置性本身就是一個(gè)非常有趣的話題,我可以在后續(xù)文章中討論它。

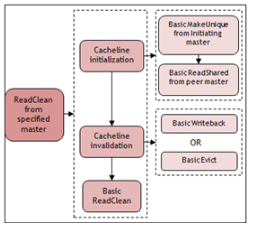

在這里,我有一個(gè)示例,展示了如何使用序列集合創(chuàng)建自定義序列生成要求。讓我們以需要驗(yàn)證與 Readclean 事務(wù)關(guān)聯(lián)的所有緩存行狀態(tài)的情況為例。(“ReadClean 是一個(gè)讀取事務(wù),用于可與其他主節(jié)點(diǎn)共享的內(nèi)存區(qū)域。保證 ReadClean 事務(wù)不會將更新主內(nèi)存的責(zé)任傳遞給啟動主服務(wù)器。通常,ReadClean 事務(wù)由想要獲取緩存行的干凈副本的主節(jié)點(diǎn)使用,例如具有直寫緩存的主節(jié)點(diǎn)。那么,您如何發(fā)起此類交易?

ReadClean 事務(wù)需要緩存行初始化,然后是緩存行失效,然后是基本的 Readclean。讓我們看看你有什么作為構(gòu)建塊。首先,采用“緩存行初始化”序列,該序列將主緩存及其對等方緩存的緩存行狀態(tài)初始化為一組隨機(jī)但有效的狀態(tài)。這可確保驗(yàn)證由主服務(wù)器啟動的一致事務(wù)的所有不同緩存行狀態(tài)轉(zhuǎn)換。這將需要一個(gè)序列,該序列將寫入啟動主服務(wù)器本地緩存。數(shù)據(jù)現(xiàn)在在本地緩存中是臟的。隨后,另一個(gè)主節(jié)點(diǎn)啟動“寫入”內(nèi)存。現(xiàn)在,本地緩存中的數(shù)據(jù)是干凈的,緩存中的數(shù)據(jù)與內(nèi)存中的數(shù)據(jù)匹配。接下來是“BasicReadShared”,它將通過從啟動主服務(wù)器獲取干凈的數(shù)據(jù)將數(shù)據(jù)讀入每個(gè)主服務(wù)器的本地緩存中。然后,您將需要一個(gè)使主節(jié)點(diǎn)的緩存行無效的序列。這將是緩存行失效序列。 對于非推理負(fù)載事務(wù),可能需要這樣做。最后,你需要有一個(gè)基本的 Readclean 序列:

可以使用嵌套序列和虛擬序列模擬完整的驗(yàn)證場景。使用分層方法,無論任何場景生成需求有多復(fù)雜,對任何場景生成需求進(jìn)行建模都變得相對容易。這種方法與虛擬序列結(jié)合使用時(shí)有助于跨多個(gè)接口利用此功能,并且在系統(tǒng)上下文中高度相關(guān),如上所示。因此,作為庫一部分的多個(gè)虛擬序列可以執(zhí)行從不同主站到同一從站或不同從站的不同順序相干事務(wù)的組合。

隨著協(xié)議復(fù)雜性的不斷增加和發(fā)展,驗(yàn)證協(xié)議所需的基礎(chǔ)設(shè)施也需要在復(fù)雜性上擴(kuò)大規(guī)模。UVM等高級方法一直在不斷發(fā)展,以滿足許多復(fù)雜的要求。驗(yàn)證基本緩存一致性系統(tǒng)本身就具有挑戰(zhàn)性。ACE 協(xié)議帶來的額外復(fù)雜性對所使用的驗(yàn)證方法提出了很高的要求。UVM 庫提供的序列生成、分布式相位和配置管理以及最新更新(可通過 UVM-1.2 庫獲得)的功能可以使 VIP 實(shí)施利用這些功能來滿足不同系統(tǒng)中的驗(yàn)證要求。

審核編輯:郭婷

-

服務(wù)器

+關(guān)注

關(guān)注

12文章

9308瀏覽量

86072 -

總線

+關(guān)注

關(guān)注

10文章

2903瀏覽量

88402 -

AMBA

+關(guān)注

關(guān)注

0文章

69瀏覽量

15047

發(fā)布評論請先 登錄

相關(guān)推薦

ARM系列之ACE協(xié)議資料匯總

AMBA CHI協(xié)議介紹

AMBA-PV TLM擴(kuò)展用戶指南

AMBA 3 AXI協(xié)議檢查器用戶指南

AMBA 4 ACE和ACE Lite協(xié)議校驗(yàn)器用戶指南

PCIe AMBA集成指南

AMBA靜態(tài)內(nèi)存接口數(shù)據(jù)表

AMBA測試接口驅(qū)動程序數(shù)據(jù)表

未來的物聯(lián)網(wǎng)將物理世界中的所有內(nèi)容都連接到互聯(lián)網(wǎng)

基于AMBA總線介紹?

將您的Magicbit(ESP32)連接到thingsboard

Arm AMBA ACE5-Lite協(xié)議規(guī)范更新

如何驗(yàn)證AMBA系統(tǒng)級環(huán)境

基于AMBA的子系統(tǒng):驗(yàn)證它們需要什么

AMBA:將所有內(nèi)容拼接到ACE您的測試

AMBA:將所有內(nèi)容拼接到ACE您的測試

評論