除通過外部多功能IO來選擇之外,易靈思通過內部重配置實現遠程更新操作也非常簡單。

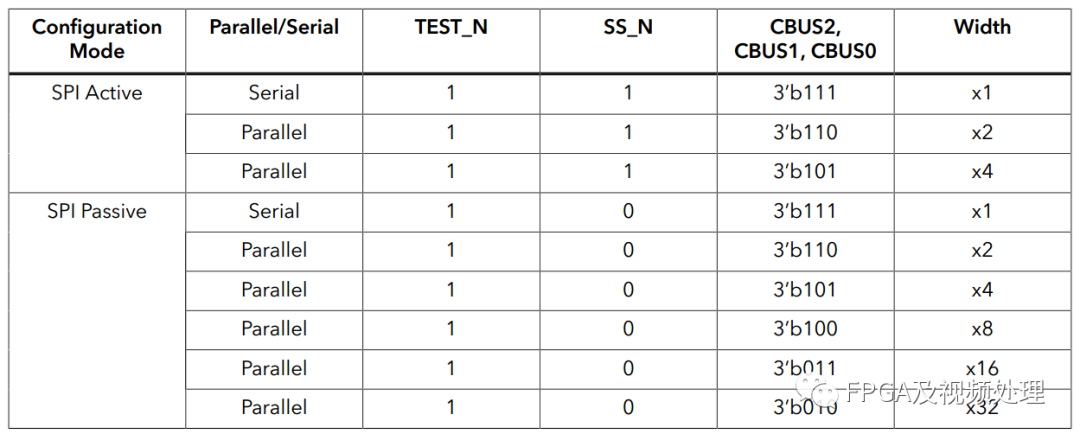

(1)使能內部重配置接口

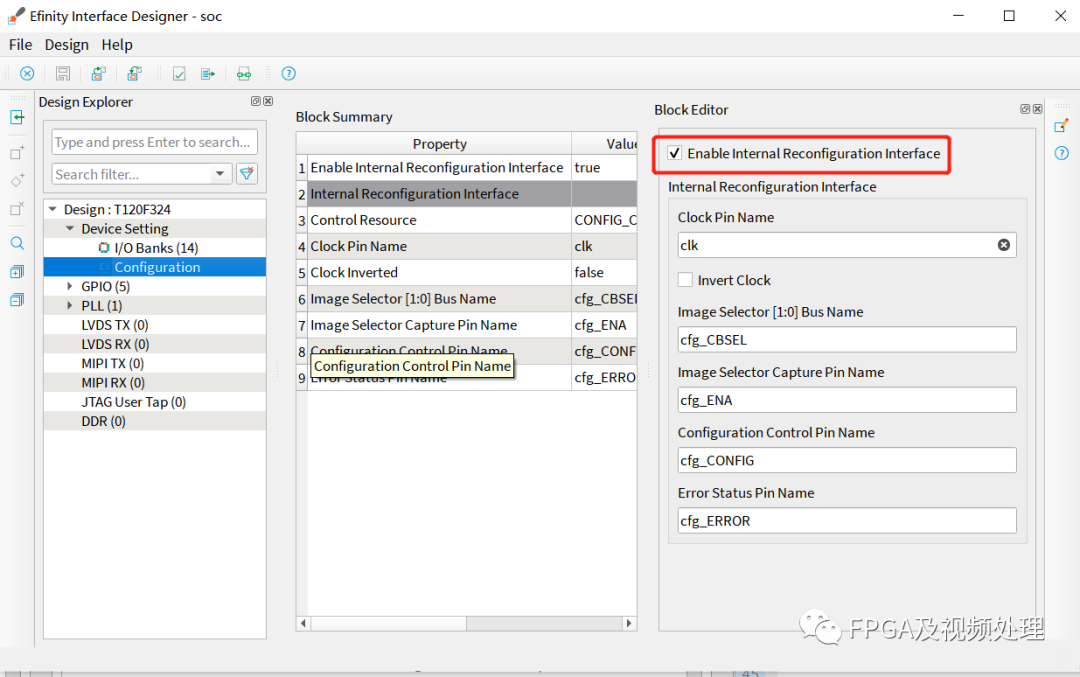

1、在interface Designer中選擇Device Setting ->Configuration

2、打開EnableInternalReconfigurationInterface

3、生成例化接口添加到top文件。

關于重配置接口就以下幾個信號

inputcfg_ERROR, output[1:0]cfg_CBSEL, outputcfg_CONFIG, outputcfg_ENA

其中_CBSEL就是選擇那個image的。ENA拉高就可以啟動相應image加載。

(2)重配置過程操作

1、通過_CBSEL選擇相應的image;

2、拉高_ENA;

3、使能_CONFIG為高;

4、如果_ERROR為0重配置成功。

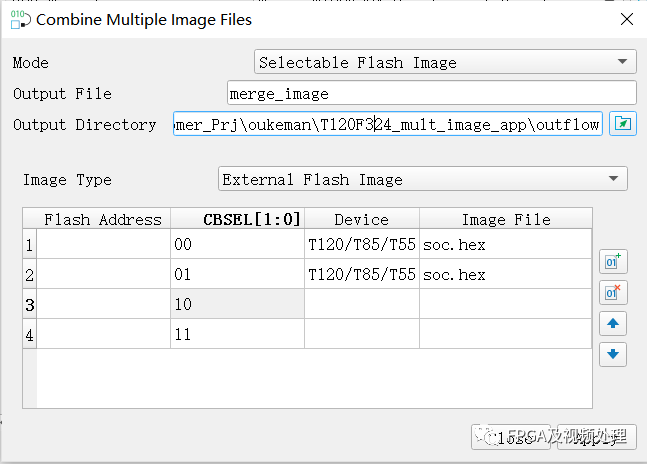

(3)組合image文件的生成

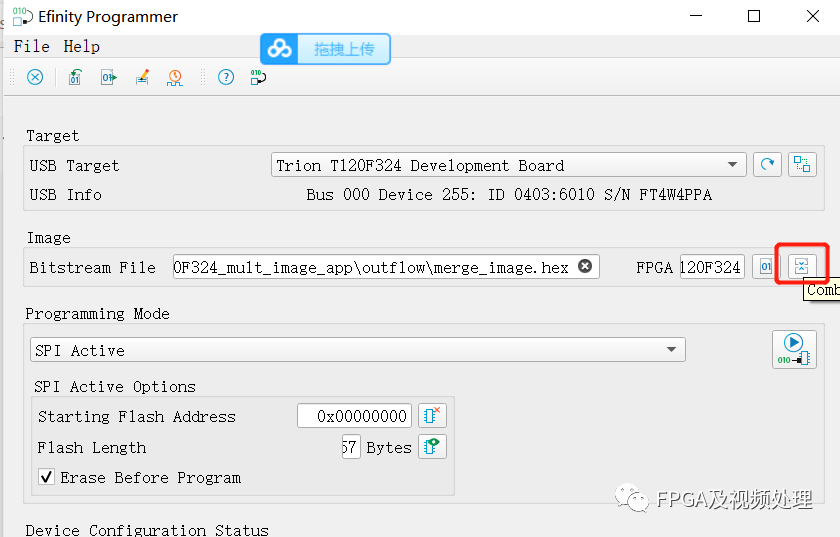

1、在Efinity Programmer中,點擊combine multiple Image Files項。

(2)在CBSEL為00的地方添加golden image,其余添加APP_image即可以,地址如果不給定,會自動分配。填寫輸出文件,點擊apply生成即可。

更詳細的信號請參考易靈思AN010.

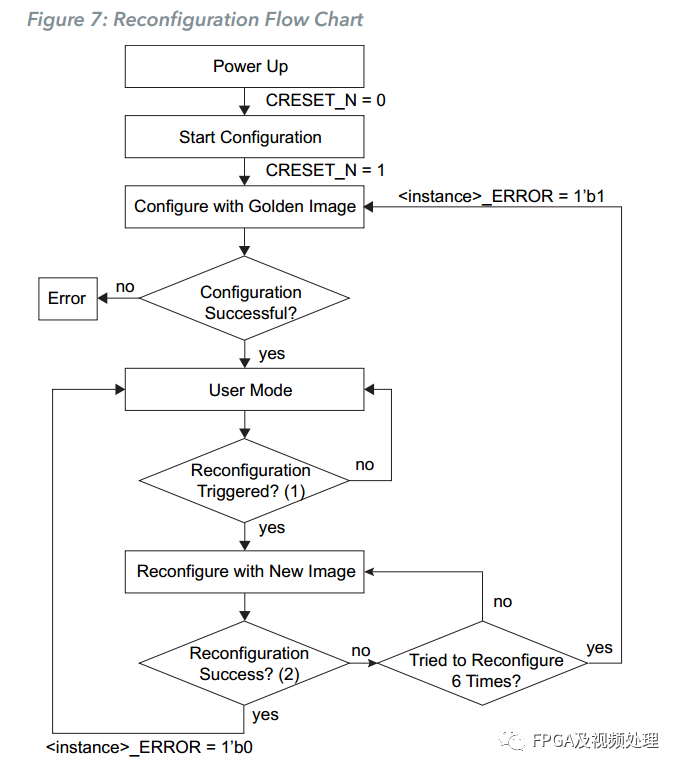

1、通過內部重配置遠程更新也要注意在上電時外部CSEL管腳的狀態,如果沒有指向goden image或者app image,那么會要等待一段時間,文檔說應該會加載6次,大概41s。

2、下面是重配置流程圖。

(1)上電之后,CRESET_N上升沿觸發配置過程。

(2)golden image加載完成之后進入user mode;

(3)用戶啟動重配置觸發,配置新image;

(4)如果配置成功則進入user mode,如果沒有配置成功則會加載6次;

(5)6次之后_ERROR拉高,并再次加載golden image;

(6)如果不想反復以上操作可以通過檢測_ERROR來禁止下次的New image配置觸發。

下面提供一個demo,CONFIG只需要拉高一個時鐘周期即可

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8691瀏覽量

151913 -

流程圖

+關注

關注

2文章

63瀏覽量

18792 -

觸發

+關注

關注

1文章

89瀏覽量

22679 -

遠程更新

+關注

關注

0文章

8瀏覽量

7625 -

易靈思

+關注

關注

5文章

48瀏覽量

4937

原文標題:易靈思內部重配置實現遠程更新 -v1

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

賽靈思發布ISE12.2強化部分可重配置FPGA技術

賽靈思公司在2017年閃存峰會上展示可重配置存儲加速解決方案

采用FPGA實現DisplayPort詳細教程【賽靈思內部資料】

Xilinx的可重配置加速堆棧為云級應用提供業界最高計算效率

談談賽靈思的局部重配置技術

賽靈思可重配置加速堆棧方案,旨在快速開發和部署加速平臺

基于SRAM的可重配置電路PLD

賽靈思的局部重配置技術(Partial Reconfiguration)

易靈思IDE更新ROM可以不用全編譯了

易靈思FPGA軟件更新的節奏,也許能磨出一個好產品

易靈思內部重配置實現遠程更新

易靈思內部重配置實現遠程更新

評論