積分梳狀濾波器(CIC,Cascaded Integrator Comb),一般用于數(shù)字下變頻(DDC)和數(shù)字上變頻(DUC)系統(tǒng)。CIC 濾波器結(jié)構(gòu)簡(jiǎn)單,沒有乘法器,只有加法器、積分器和寄存器,資源消耗少,運(yùn)算速率高,可實(shí)現(xiàn)高速濾波,常用在輸入采樣率最高的第一級(jí),在多速率信號(hào)處理系統(tǒng)中具有著廣泛應(yīng)用。

DDC 原理

◆DDC 工作原理

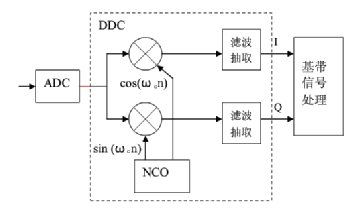

DDC 主要由本地振蕩器(NCO) 、混頻器、濾波器等組成,如下圖所示。

DDC 將中頻信號(hào)與振蕩器產(chǎn)生的載波信號(hào)進(jìn)行混頻,信號(hào)中心頻率被搬移,再經(jīng)過抽取濾波,恢復(fù)原始信號(hào),實(shí)現(xiàn)了下變頻功能。

中頻數(shù)據(jù)采樣時(shí),需要很高的采樣頻率來(lái)確保 ADC(模數(shù)轉(zhuǎn)換器)采集到信號(hào)的信噪比。經(jīng)過數(shù)字下變頻后,得到的基帶信號(hào)采樣頻率仍然是 ADC 采樣頻率,所以數(shù)據(jù)率很高。此時(shí)基帶信號(hào)的有效帶寬往往已經(jīng)遠(yuǎn)小于采樣頻率,所以利用抽取、濾波進(jìn)行數(shù)據(jù)速率的轉(zhuǎn)換,使采樣率降低,避免資源的浪費(fèi)和設(shè)計(jì)的困難,就成為 DDC 不可缺少的一部分。

而采用 CIC 濾波器進(jìn)行數(shù)據(jù)處理,是 DDC 抽取濾波部分最常用的方法。

◆帶通采樣定理

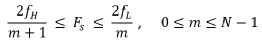

在 DDC 系統(tǒng)中,輸入的中頻載波信號(hào)會(huì)根據(jù)載波頻率進(jìn)行頻移,得到一個(gè)帶通信號(hào)。如果此時(shí)仍然采用奈奎斯特采樣定理,即采樣頻率為帶通信號(hào)最高頻率的兩倍,那么此時(shí)所需的采樣頻率將會(huì)很高,設(shè)計(jì)會(huì)變的復(fù)雜。此時(shí)可按照帶通采樣定理來(lái)確定抽樣頻率。

帶通采樣定理:一個(gè)頻帶限制在 的連續(xù)帶通信號(hào),帶寬為

的連續(xù)帶通信號(hào),帶寬為 。令

。令 ,其中 N 為不大于

,其中 N 為不大于 的最大正整數(shù),如果采樣頻率滿足條件:

的最大正整數(shù),如果采樣頻率滿足條件:

則該信號(hào)完全可以由其采樣值無(wú)失真的重建。

當(dāng) m=1 時(shí),帶通采樣定理便是奈奎斯特采樣定理。

帶通采樣定理的另一種描述方式為:若信號(hào)最高頻率為信號(hào)帶寬的整數(shù)倍,采樣頻率只需大于信號(hào)帶寬的兩倍即可,此時(shí)不會(huì)發(fā)生頻譜混疊。

所以,可以認(rèn)為采樣頻率的一半是 CIC 濾波器的截止頻率。

◆DDC 頻譜搬移

例如一個(gè)帶寬信號(hào)中心頻率為 60MHz,帶寬為 8MHz, 則頻率范圍為 56MHz ~ 64MHz,m 的可取值范圍為 0 ~ 7。取 m=1, 則采樣頻率范圍為 64MHz ~ 112MHz。

取采樣頻率為 80MHz,設(shè) NCO 中心頻率為 20 MHz,下面討論復(fù)信號(hào)頻譜搬移示意圖。

(1)考慮頻譜的對(duì)稱性,輸入復(fù)信號(hào)的頻譜示意圖如下:

(2)80MHz 采樣頻率采樣后,5664MHz 的頻帶被搬移到了 -24 -16MHz 與 136 ~ 144MHz(高于采樣頻率被濾除)的頻帶處,-64~ -56MHz 的頻帶被搬移到 -144~ -136MHz(高于采樣頻率被濾除)與 16~24MHz 的頻帶處。

采樣后頻帶分布如下:

(3)信號(hào)經(jīng)過 20MHz NCO 的正交電路后, -24~ -16MHz 的頻帶被搬移到 -44MHz 與 -44 -36MHz 的頻帶處,1624MHz 的頻帶被搬移到 -44MHz 與 36~44MHz 的頻帶處,如下所示。

(4)此時(shí)中頻輸入的信號(hào)已經(jīng)被搬移到零中頻基帶處。

-44~ -36MHz 和 3644MHz 的帶寬信號(hào)是不需要的,可以濾除;-44MHz 的零中頻信號(hào)數(shù)據(jù)速率仍然是 80MHz,可以進(jìn)行抽取降低數(shù)據(jù)速率。而 CIC 濾波,就是要完成這個(gè)過程。

上述復(fù)習(xí)了很多數(shù)字信號(hào)處理的內(nèi)容,權(quán)當(dāng)拋 DDC 的磚,引 CIC 的玉。

CIC 濾波器原理

◆單級(jí) CIC 濾波器

設(shè)濾波器抽取倍數(shù)為 D,則單級(jí)濾波器的沖激響應(yīng)為:

對(duì)其進(jìn)行 z 變換,可得單級(jí) CIC 濾波器的系統(tǒng)函數(shù)為:

令

可以看出,單級(jí) CIC 濾波器包括兩個(gè)基本組成部分:積分部分和梳狀部分,結(jié)構(gòu)圖如下:

◆積分器

積分器是一個(gè)單級(jí)點(diǎn)的 IIR(Infinite Impulse Response,無(wú)限長(zhǎng)脈沖沖激響應(yīng))濾波器,且反饋系數(shù)為 1,其狀態(tài)方程和系統(tǒng)函數(shù)分別為:

◆梳狀器

梳狀器是一個(gè) FIR 濾波器,其狀態(tài)方程和系統(tǒng)函數(shù)分別為:

◆抽取器

在積分器之后,還有一個(gè)抽取器,抽取倍數(shù)與梳狀器的延時(shí)參數(shù)是一致的。利用 z 變換的性質(zhì)進(jìn)行恒等變換,將抽取器移動(dòng)到積分器與梳狀器之間,可得到單級(jí) CIC 濾波器結(jié)構(gòu),如下所示。

◆參數(shù)說明

CIC 濾波器結(jié)構(gòu)變換之前的參數(shù) D 可以理解為梳狀濾波器的延時(shí)或階數(shù);變換之后,D 的含義 變?yōu)槌槿”稊?shù),而此時(shí)梳狀濾波器的延時(shí)為 1,即階數(shù)為 1。

很多學(xué)者會(huì)引入一個(gè)變量 M,表示梳狀器每一級(jí)的延時(shí),此時(shí)梳妝部分的延時(shí)就不為 1 了。那么梳狀器的系統(tǒng)函數(shù)就變?yōu)椋?/p>

其實(shí)把 DM 整體理解為單級(jí)濾波器延時(shí),或者抽取倍數(shù),也都是可以的。可能實(shí)現(xiàn)的方式或結(jié)構(gòu)不同,但是最后的結(jié)果都是一樣的。本次設(shè)計(jì)中,單級(jí)濾波器延時(shí)都為 M=1,即抽取倍數(shù)與濾波延時(shí)相同。

◆多級(jí) CIC 濾波器

單級(jí) CIC 濾波器的阻帶衰減較差,為了提高濾波效果,抽取濾波時(shí)往往會(huì)采用多級(jí) CIC 濾波器級(jí)聯(lián)的結(jié)構(gòu)。

實(shí)現(xiàn)多級(jí)直接級(jí)聯(lián)的 CIC 濾波器在設(shè)計(jì)和資源上并不是最優(yōu)的方式,需要對(duì)其結(jié)構(gòu)進(jìn)行調(diào)整。如下所示,將積分器和梳狀濾波器分別移至一組,并將抽取器移到梳狀濾波器之前。先抽取再進(jìn)行濾波,可以減少數(shù)據(jù)處理的長(zhǎng)度,節(jié)約硬件資源。

當(dāng)然,級(jí)聯(lián)數(shù)越大,旁瓣抑制越好,但是通帶內(nèi)的平坦度也會(huì)變差。所以級(jí)聯(lián)數(shù)不宜過多,一般最多 5 級(jí)。

CIC 濾波器設(shè)計(jì)

◆設(shè)計(jì)說明

CIC 濾波器本質(zhì)上就是一個(gè)簡(jiǎn)單的低通濾波器,截止頻率為采樣頻率除以抽取倍數(shù)后的一半。輸入數(shù)據(jù)信號(hào)仍然是 7.5MHz 和 250KHz,采樣頻率 50MHz。抽取倍數(shù)設(shè)置為 5,則截止頻率為 5MHz,小于 7.5MHz,可以濾除 7.5MHz 的頻率成分。設(shè)計(jì)參數(shù)如下:

輸入頻率: 7.5MHz 和 250KHz

采樣頻率: 50MHz

阻帶: 5MHz

階數(shù): 1(M=1)

級(jí)數(shù): 3(N=3)

關(guān)于積分時(shí)中間數(shù)據(jù)信號(hào)的位寬,很多地方給出了不同的計(jì)算方式,計(jì)算結(jié)果也大相徑庭。這里總結(jié)一下使用最多的計(jì)算方式:

其中,D 為抽取倍數(shù),M 為濾波器階數(shù),N 為濾波器級(jí)數(shù)。抽取倍數(shù)為 5,濾波器階數(shù)為 1,濾波器級(jí)聯(lián)數(shù)為 3,取輸入信號(hào)數(shù)據(jù)位寬為 12bit,對(duì)數(shù)部分向上取整,則積分后數(shù)據(jù)不溢出的中間信號(hào)位寬為 21bit。

為了更加寬裕的設(shè)計(jì),濾波器階數(shù)如果理解為未變換結(jié)構(gòu)前的多級(jí) CIC 濾波器直接型結(jié)構(gòu),則濾波器階數(shù)可以認(rèn)為是 5,此時(shí)中間信號(hào)最大位寬為 27bit。

◆積分器設(shè)計(jì)

根據(jù)輸入數(shù)據(jù)的有效信號(hào)的控制,積分器做一個(gè)簡(jiǎn)單的累加即可,注意數(shù)據(jù)位寬。

//3 stages integrator

module integrator

#(parameter NIN = 12,

parameter NOUT = 21)

(

input clk ,

input rstn ,

input en ,

input [NIN-1:0] din ,

output valid ,

output [NOUT-1:0] dout) ;

reg [NOUT-1:0] int_d0 ;

reg [NOUT-1:0] int_d1 ;

reg [NOUT-1:0] int_d2 ;

wire [NOUT-1:0] sxtx = {{(NOUT-NIN){1'b0}}, din} ;

//data input enable delay

reg [2:0] en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_r <= 'b0 ;

end

else begin

en_r <= {en_r[1:0], en};

end

end

//integrator

//stage1

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d0 <= 'b0 ;

end

else if (en) begin

int_d0 <= int_d0 + sxtx ;

end

end

//stage2

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d1 <= 'b0 ;

end

else if (en_r[0]) begin

int_d1 <= int_d1 + int_d0 ;

end

end

//stage3

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d2 <= 'b0 ;

end

else if (en_r[1]) begin

int_d2 <= int_d2 + int_d1 ;

end

end

assign dout = int_d2 ;

assign valid = en_r[2];

endmodule

Verilog CIC濾波器設(shè)計(jì)

Verilog CIC濾波器設(shè)計(jì)