SoC設計驗證趨勢

近幾十年,芯片設計復雜度的提升讓驗證成為IC設計中的技術瓶頸,而工藝節(jié)點的演進與設計和驗證能力的鴻溝也有待業(yè)內(nèi)創(chuàng)新方法學和解決方案去彌補和追趕。 當前數(shù)字芯片硅前驗證的主要手段有三個——邏輯仿真(Simulation)、硬件加速仿真(Emulation)驗證和原型驗證(Prototyping)。 邏輯仿真是傳統(tǒng)驗證手段,通過對模塊級邏輯的行為進行建模,芯片設計團隊可以利用仿真軟件分區(qū)塊對SoC進行驗證,以此確認芯片功能是否符合確定指標。然而單靠軟件仿真在當下的SoC設計中的局限性日益明顯,主要是因為軟件仿真在運行速度和容量方面的局限性,所以在SoC驗證階段啟用硬件加速仿真和原型驗證也漸漸成為業(yè)界的主流。 硬件加速仿真是將RTL導入到專門的硬件系統(tǒng)中進行仿真加速,通過加速器以及專門的外接設備,這個過程比仿真要快幾百甚至上千倍。因此設計團隊可以對整體SoC及系統(tǒng)進行功能驗證,快速定位SoC和系統(tǒng)設計中的缺陷。 原型驗證是將RTL映射到由FPGA搭建的原型驗證系統(tǒng)上進行功能仿真。雖然FPGA原型驗證系統(tǒng)更接近真實芯片的使用環(huán)境,可以配合軟件開發(fā)者進行最后調(diào)試,但是由于FPGA的利用率不高,同時受限于FPGA架構(gòu),原型驗證平臺的查錯和錯誤定位功能比不上硬件加速器,所以原型證往往是在RTL比較成熟之后進行軟硬件的協(xié)同驗證。

上述的三種驗證環(huán)境各有不同的應用場景和特色,廠家在驗證過程應該各取所長,利用各類工具特性在IC設計不同階段中發(fā)揮最大作用。現(xiàn)在芯片規(guī)模越來越大,硬件和軟件的交互變得越來越復雜,單一的硬件或軟件驗證方法已難以滿足要求。隨著更多的系統(tǒng)廠家進入芯片領域,軟硬件協(xié)同仿真在驗證活動中的占比越來越大,軟件團隊的介入點更加提前。在這一階段RTL code和軟件聯(lián)合迭代的需求,快速構(gòu)建硬件加速仿真和原型驗證環(huán)境的需求也日益旺盛。

硬件和軟件協(xié)同驗證已成為新趨勢,但也帶來了新的問題:

硬件仿真器價格昂貴,機房建設周期長,維護成本高;

驗證需要搭建軟件、硬件加速及FPGA原型驗證等多個環(huán)境,如何提高流程效率?

如何縮短每個驗證環(huán)境bring up時間,提高仿真加速硬件資源的利用率?

芯片設計人才緊缺,如何搭建硬件仿真加速環(huán)境?需要哪些團隊配合?

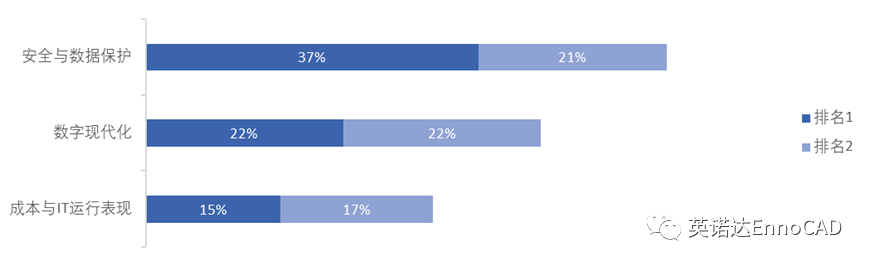

仿真與原型驗證上云 現(xiàn)代社會云無處不在,它早已滲入我們生活的每個角落。越來越多的企業(yè)也選擇上云,云已是公認的趨勢。云可以為企業(yè)降低采購和維護成本,可以為企業(yè)帶來更多計算資源,甚至是遠程及靈活性。2020年,德勤對500位企業(yè)IT負責人進行了訪問,統(tǒng)計了企業(yè)上云的動機,調(diào)查顯示,有接近58%的IT負責人將“安全與數(shù)據(jù)保護”列為企業(yè)上云排名第一和第二的動機,其次是“數(shù)據(jù)的現(xiàn)代化”,有三成負責人將“成本與IT運行性能”列為上云動機。由此可見,云服務經(jīng)過幾年的發(fā)展已經(jīng)得到了大部分企業(yè)用戶的認可,尤其是當下網(wǎng)絡攻擊復雜難防,企業(yè)的IT運維的壓力陡增,企業(yè)也希望將這部分工作移交給云平臺或第三方來維護。  上云遷移的驅(qū)動力調(diào)查,Source: Deloitte Insights EDA的設計流程復雜,其中每一個步驟都需要特殊工具完成。像硬件仿真/原型驗證這種需要批量作業(yè)、對算力要求較高的工具是天然適合上云的領域。設計團隊可以按需、按時使用,那么就能幫助到這些團隊以很小的成本使用硬件仿真資源,幫助企業(yè)縮短設計周期,提高驗證的效率。 英諾達SVS系統(tǒng)驗證平臺 英諾達EnCitius System VerificationStudio (SVS)系統(tǒng)驗證平臺是集成電路系統(tǒng)級芯片(SoC)及系統(tǒng)相關驗證的一站式全棧解決方案,通過英諾達自主研發(fā)的驗證流程和云平臺,SVS可以幫助芯片設計廠商加速驗證仿真流程、降低研發(fā)成本、提高流片良率、縮短time-to-market。 英諾達的系統(tǒng)驗證云平臺的核心集通用高性能服務器、硬件仿真加速器和原型驗證加速器的異構(gòu)算力中心。云平臺整體算力充足,單就硬件仿真加速器而言,單個設計容量支持從3200萬門到23億門,整體硬件仿真加速器容量達46億門,可以滿足國內(nèi)大部分芯片設計規(guī)模要求。此外,圍繞硬件對環(huán)境苛刻要求,云平臺采用了國內(nèi)最高機房建設標準,以及雙路市電供電+柴油供電等多個措施,保證機房環(huán)境安全、穩(wěn)定。 此外依托系統(tǒng)驗證硬件資源,SVS系統(tǒng)驗證平臺為客戶提供從子系統(tǒng)/SoC仿真, 硬件仿真加速驗證,到大規(guī)模設計原型驗證的驗證環(huán)境搭建、切換的一站式解決方案,客戶可以根據(jù)實際需求選擇其中一個和多個產(chǎn)品。

上云遷移的驅(qū)動力調(diào)查,Source: Deloitte Insights EDA的設計流程復雜,其中每一個步驟都需要特殊工具完成。像硬件仿真/原型驗證這種需要批量作業(yè)、對算力要求較高的工具是天然適合上云的領域。設計團隊可以按需、按時使用,那么就能幫助到這些團隊以很小的成本使用硬件仿真資源,幫助企業(yè)縮短設計周期,提高驗證的效率。 英諾達SVS系統(tǒng)驗證平臺 英諾達EnCitius System VerificationStudio (SVS)系統(tǒng)驗證平臺是集成電路系統(tǒng)級芯片(SoC)及系統(tǒng)相關驗證的一站式全棧解決方案,通過英諾達自主研發(fā)的驗證流程和云平臺,SVS可以幫助芯片設計廠商加速驗證仿真流程、降低研發(fā)成本、提高流片良率、縮短time-to-market。 英諾達的系統(tǒng)驗證云平臺的核心集通用高性能服務器、硬件仿真加速器和原型驗證加速器的異構(gòu)算力中心。云平臺整體算力充足,單就硬件仿真加速器而言,單個設計容量支持從3200萬門到23億門,整體硬件仿真加速器容量達46億門,可以滿足國內(nèi)大部分芯片設計規(guī)模要求。此外,圍繞硬件對環(huán)境苛刻要求,云平臺采用了國內(nèi)最高機房建設標準,以及雙路市電供電+柴油供電等多個措施,保證機房環(huán)境安全、穩(wěn)定。 此外依托系統(tǒng)驗證硬件資源,SVS系統(tǒng)驗證平臺為客戶提供從子系統(tǒng)/SoC仿真, 硬件仿真加速驗證,到大規(guī)模設計原型驗證的驗證環(huán)境搭建、切換的一站式解決方案,客戶可以根據(jù)實際需求選擇其中一個和多個產(chǎn)品。

硬件仿真器價格昂貴,機房建設周期長,維護成本高?

英諾達提供硬件仿真所需的所有基礎設施及配件,芯片公司無需承擔前期的建設成本,亦無運維的后顧之憂,更加聚焦于芯片的開發(fā)工作中。直接減少了前期構(gòu)建基礎設施和后期運維的時間,進一步縮短芯片整體開發(fā)周期。英諾達的AE和IT技術團隊可為客戶提供支持服務,包括幫助客戶搭建驗證環(huán)境,配置輔助設備,維持數(shù)據(jù)中心的高效運轉(zhuǎn),維護機房及設備等。

驗證需要搭建多個環(huán)境,如何提高流程效率?

英諾達SVS系統(tǒng)驗證平臺具備成熟的硬件仿真驗證流程,結(jié)合硬件云平臺給予客戶硬件仿真全流程的賦能,無論是零經(jīng)驗還是有經(jīng)驗客戶,英諾達都可以提供完善的流程指導和解決方案,芯片公司可以快速上手,低成本嘗試先進的硬件仿真技術。

如何縮短bring up時間,提高仿真加速硬件資源的利用率?

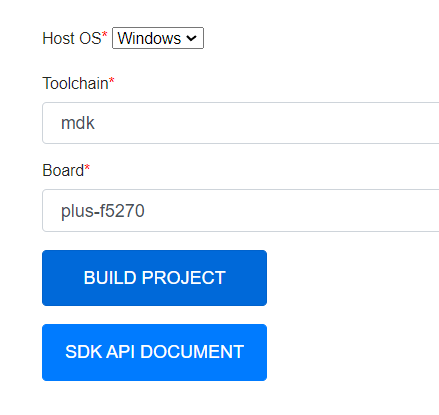

SVS平臺通過統(tǒng)一和簡化組件集成接口,實現(xiàn)不同驗證平臺組件快速集成,結(jié)合易用的集成工具和轉(zhuǎn)換腳本,提升了平臺之間組件切換的效率,減少了驗證環(huán)境構(gòu)建的時間。通過SVS工具可以生成golden的各類接口組件,實現(xiàn)硬件仿真加速環(huán)境和FPGA原型驗證環(huán)境的快速移植,可以有效縮短bring up的時間,將寶貴的驗證人力資源投入到驗證執(zhí)行階段而非環(huán)境搭建及調(diào)試階段。

如何搭建硬件仿真加速環(huán)境?需要哪些團隊配合?

硬件仿真加速和原型驗證環(huán)境的構(gòu)建過程包括驗證策略制定,環(huán)境方案制定,RTL代碼移植,環(huán)境組件集成開發(fā),軟硬件聯(lián)合調(diào)試等環(huán)節(jié)。涉及設計、驗證、軟件、測試多團隊之間配合,需要建立一個高效的流程來保證驗證環(huán)境的質(zhì)量。在驗證高峰期,軟硬件迭代的次數(shù)會很多,快速的版本迭代對驗證效率的提升幫助很大,SVS可以快速從零開始構(gòu)建開發(fā)環(huán)境,并高效進行database的迭代和管理。 驗證過程中遇到難題和瓶頸遠不止于此,英諾達SVS系統(tǒng)驗證平臺自上線以來,已幫助多名用戶解決了驗證難題,提高了驗證效率和流片良率,英諾達亦希望通過線上交流等方式將此經(jīng)驗分享給更多有需求的客戶。 5月30日1030鎖定直播間,英諾達將為大家分享最新的硬件加速技術和一站式SoC及系統(tǒng)驗證解決方案,解答觀眾提出的相關問題;在產(chǎn)品演示環(huán)節(jié),英諾達將演示如何使用EnCitius SVS系統(tǒng)驗證平臺幫助客戶在云端實現(xiàn)驗證加速。

責任編輯:彭菁

-

集成電路

+關注

關注

5392文章

11624瀏覽量

363192 -

加速器

+關注

關注

2文章

807瀏覽量

38090 -

硬件仿真

+關注

關注

1文章

31瀏覽量

19322

原文標題:云端驗證時代來臨,如何應對全新挑戰(zhàn)

文章出處:【微信號:gh_387c27f737c1,微信公眾號:英諾達EnnoCAD】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

如何搭建企業(yè)AI開發(fā)環(huán)境

Verilog 電路仿真常見問題 Verilog 在芯片設計中的應用

SSM開發(fā)環(huán)境的搭建教程 SSM與Spring Boot的區(qū)別

【MM32F5270】Keil開發(fā)環(huán)境搭建

【干貨分享】硬件在環(huán)仿真(HiL)測試

TI RF Transceiver EVM自動化環(huán)境搭建方法

如何搭建硬件仿真加速環(huán)境

如何搭建硬件仿真加速環(huán)境

評論