來源:《半導體芯科技》雜志

作者:Sumant Sarkar, 泛林集團半導體工藝與整合工程師

使用Coventor SEMulator3D? 創建可以預測寄生電容的機器學習模型

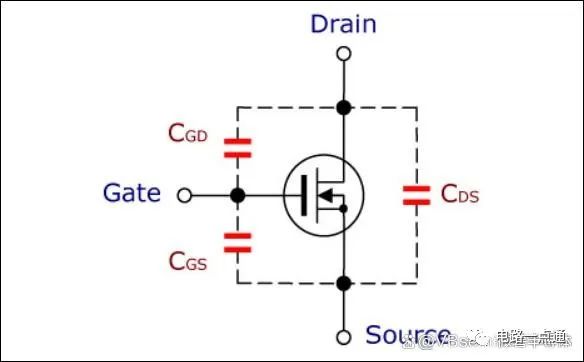

減少柵極金屬和晶體管的源極/漏極接觸之間的寄生電容可以減少器件的開關延遲。減少寄生電容的方法之一是設法降低柵極和源極/漏極之間材料層的有效介電常數,這可以通過在該位置的介電材料中引入空氣間隙來實現。這種類型的方式過去已經用于后道工序(BEOL)中,以減少金屬互連之間的電容[1-4]。本文中,我們將專注于前道工序(FEOL),并演示在柵極和源極/漏極之間引入空氣間隙的SEMulator3D?模型[5]。

SEMulator3D?是一個虛擬的制造軟件平臺,可以在設定的半導體工藝流程內模擬工藝變量。利用SEMulator3D?設備中的實驗設計(DoE)功能,我們展示了寄生電容與刻蝕深度和其他用于制作空氣間隙的刻蝕工藝參數的相關性,以及它與空氣間隙大小和體積的相關性。

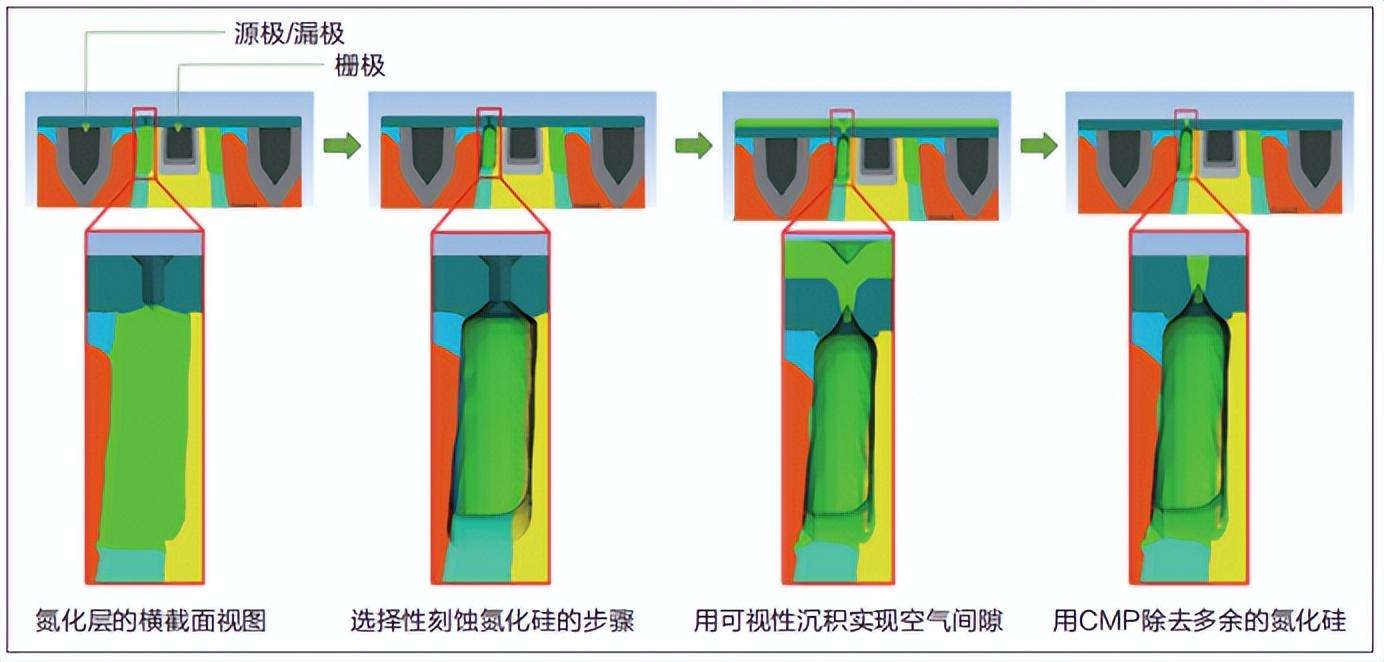

圖1顯示了SEMulator3D?FinFET模型的橫截面。為了在FinFET的柵極和源極/漏極之間引入空氣間隙,我們進行了高選擇比的氮化硅刻蝕工藝,然后進行經過優化的氮化硅沉積工藝,以封閉結構并產生空氣間隙結構。接著用氮化硅CMP(化學機械拋光)工藝對表面進行平坦化處理。

△圖1:在FinFET模型中引入空氣間隙的SEMulator3D工藝流程。可視性沉積的步驟通過在頂端夾止的方式產生空氣間隙,然后進行CMP步驟除去多余的氮化硅。空氣間隙減少了柵極和源極/漏極之間的寄生電容。空氣間隙的大小可以通過改變刻蝕反應物的刻蝕深度、晶圓傾角和等離子體入射角度分布來控制。

使用SEMulator3D的虛擬測量功能測量以下指標:

1.柵極金屬和源極/漏極之間的寄生電容

2.空氣間隙的體積

3.空氣間隙z軸的最小值,代表空氣間隙的垂直尺寸

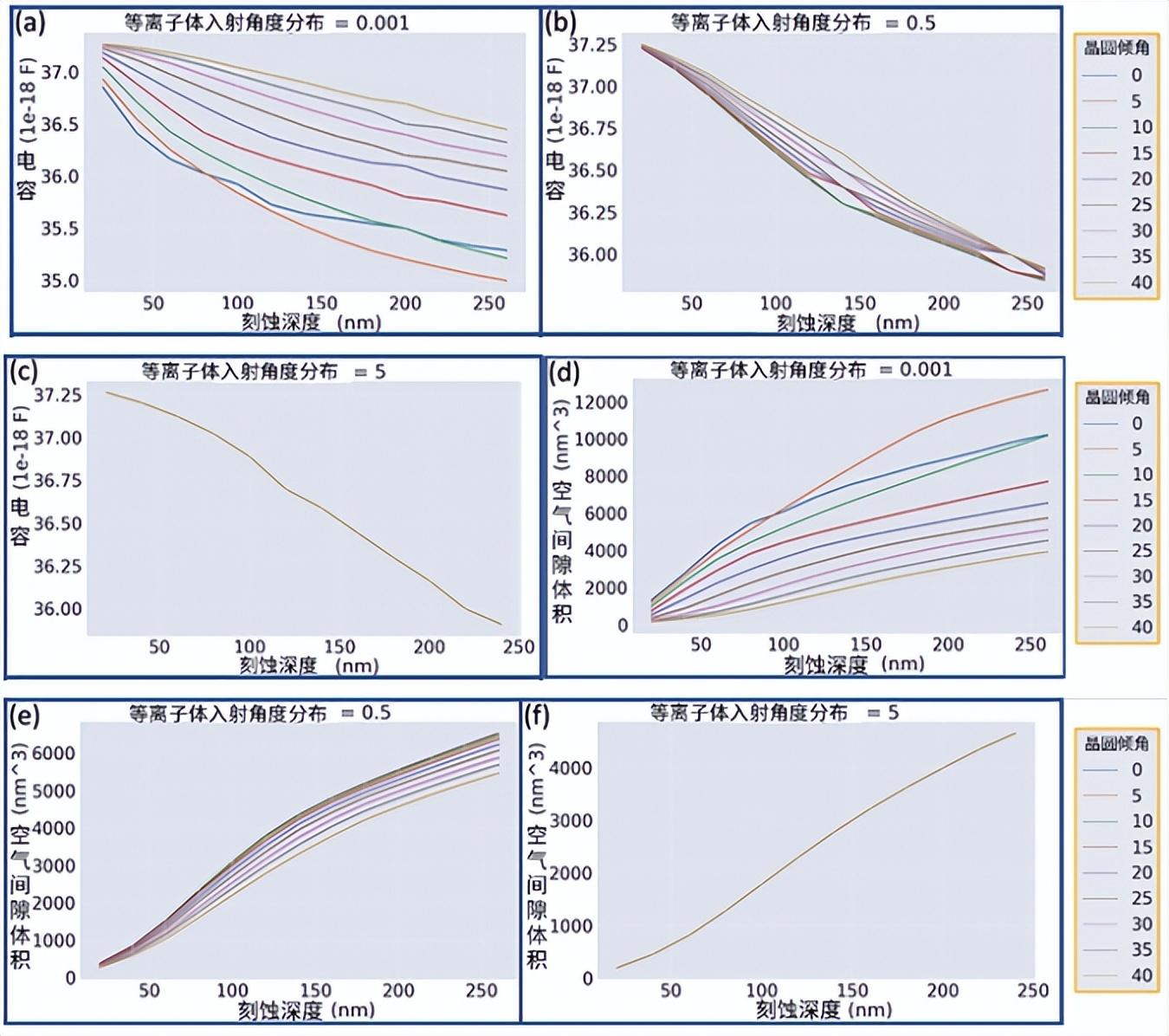

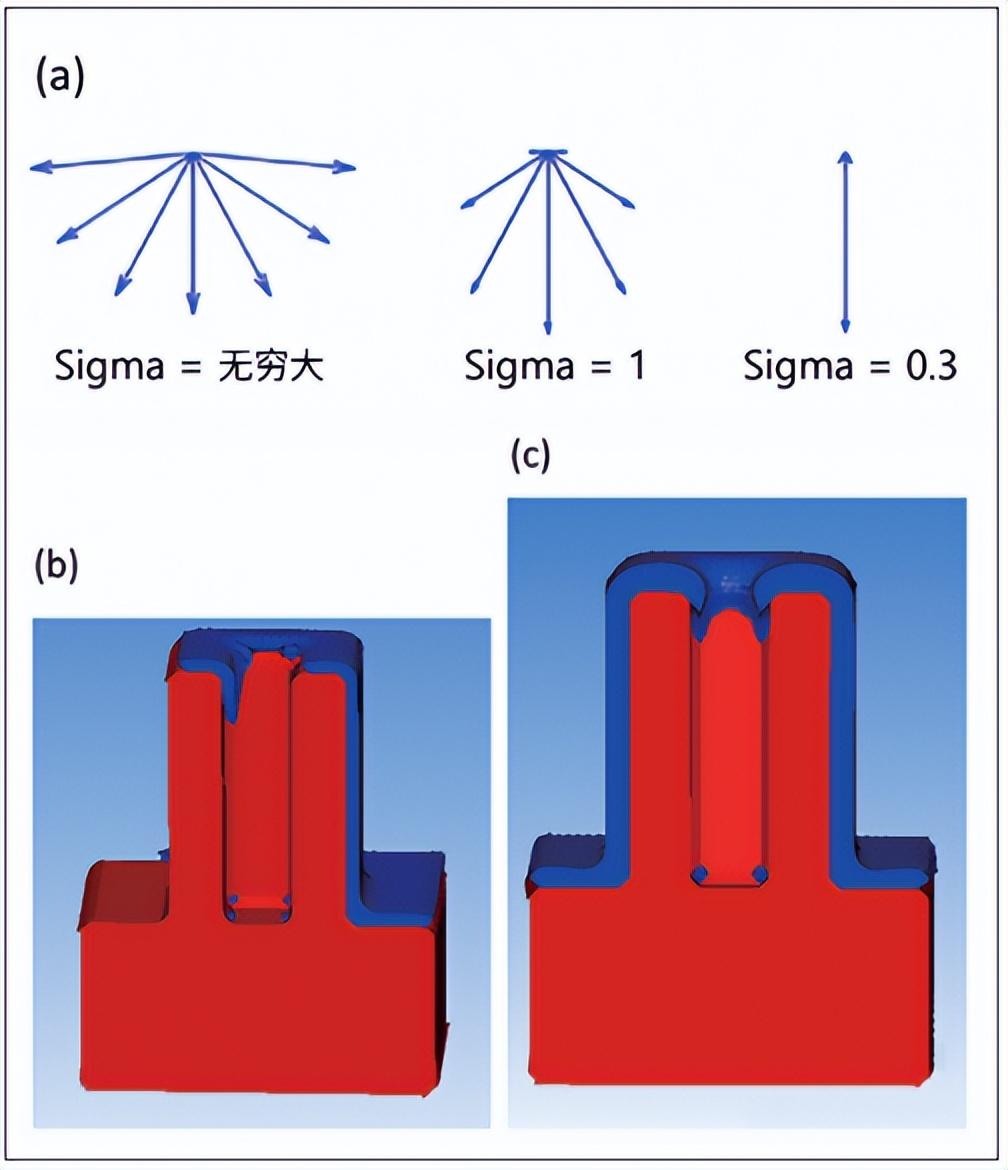

在氮化硅刻蝕步驟中,刻蝕深度、刻蝕反應物等離子體入射角度分布(在文獻中稱為等離子體入射角度分布)和晶圓傾角(假定晶圓旋轉)在實驗設計期間是變化的。圖2a-f顯示了在不同的晶圓傾角和等離子體入射角度分布值下,電容和空氣間隙的體積如何跟隨刻蝕深度發生變化。隨著刻蝕深度的增加,產生的空氣間隙也變大(圖2d)。因為空氣的介電常數比氮化物要低很多,所以這降低了有效的介電常數。相應地,柵極和源極/漏極之間的寄生電容就減小了。傾斜角減小會將刻蝕反應物從側壁移開,并將其推向所產生的空氣間隙底部(圖3b-c)。這解釋了為什么在給定的深度和等離子體入射角度分布值下,晶圓傾角越小,空氣間隙越大,電容越小(圖2a&d)。另一個重要的結果是,等離子體入射角度分布的增加會導致晶圓傾角影響減弱。當等離子體入射角度分布設置為5度(對應較寬/等向性的角分散)的時候,晶圓傾角對電容和空氣間隙體積完全沒有影響(圖2c&f)。這與等離子體入射角度分布增加對刻蝕的影響是一致的。等離子體入射角度分布增加會使刻蝕反應物更等向性地轟擊基板(圖3a)。這意味著相比等離子體入射角度分布值低的時候,晶圓傾角不再影響刻蝕行為。

△圖2:隨著刻蝕深度增加,空氣間隙體積增大,寄生電容減少(圖2a&d)。隨著晶圓傾角降低,這種下降更為急劇。但晶圓傾角的影響隨著等離子體入射角度分布的增加而減小,當等離子體入射角度分布為5度時,晶圓傾角對電容和空氣間隙體積沒有影響(圖2c&f)。

△圖3:(a)角分散(sigma)對刻蝕反應物方向性的影響;(b)45度晶圓傾角的影響(晶圓被固定);(c)80度晶圓傾角的影響(晶圓旋轉)。圖片來源:SEMulator3D產品文檔

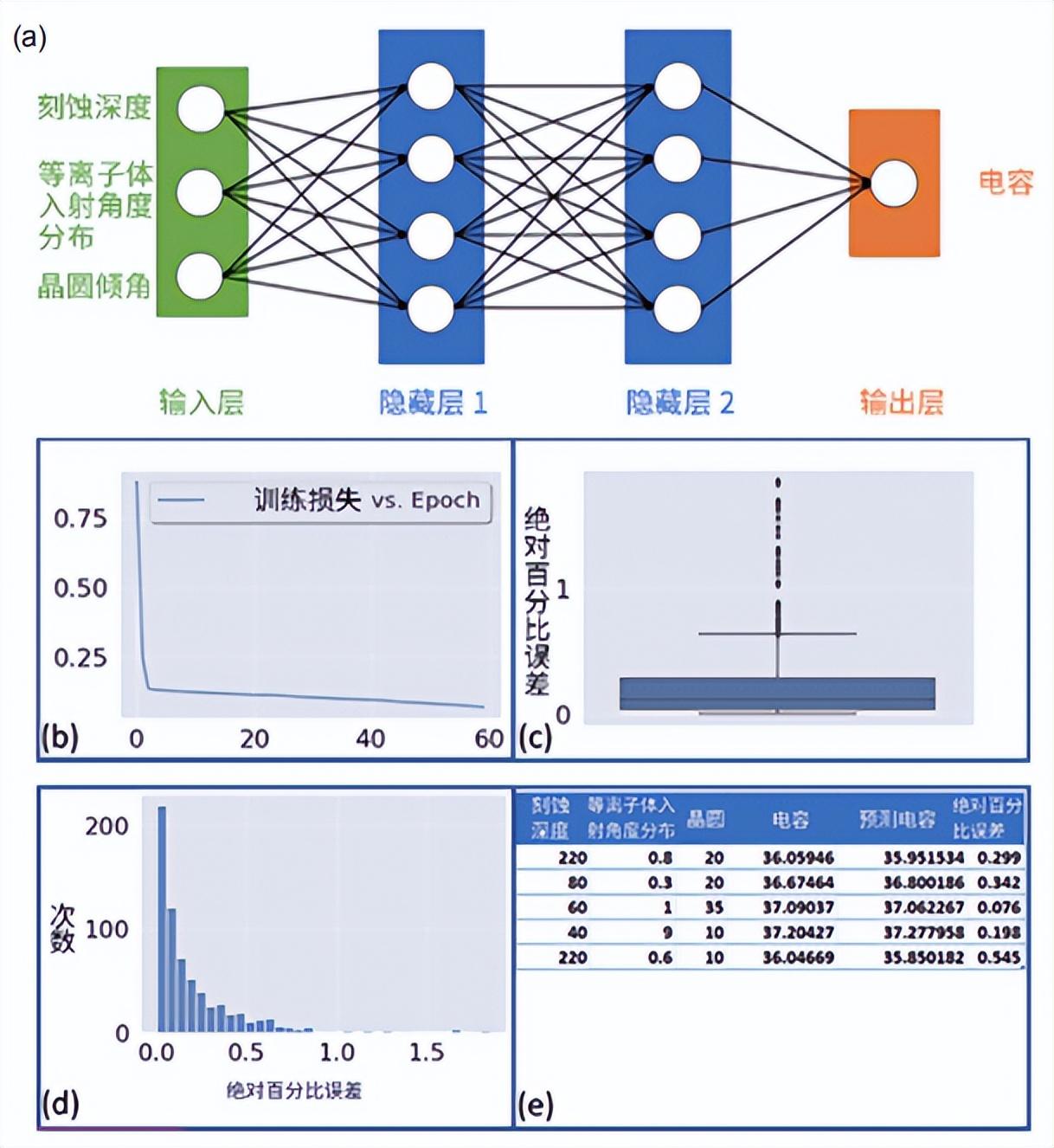

運行大型的實驗設計需要消耗很多時間和算力資源。但這在工藝優化中很有必要——實驗設計參數空間上的任何減少都有助于減少所需的時間和資源。能夠基于自變量預測結果的機器學習模型非常有用,因為它能減少為所有自變量組合進行實驗設計的需求。為了這一目標,將從實驗設計中收集到的數據分成訓練集(70%)和測試集(30%),然后將其輸入人工神經網絡(ANN)。該模型有兩個隱藏層(圖4a),用網格搜索法進行超參數調優。該模型在測試數據上運行,發現其平均準確度為99.8%。四分之三測試集的絕對百分比誤差(APE)為0.278%及以下(圖4c)。圖4e顯示了預測和實際寄生電容的測試行樣本。這種機器學習的應用使我們能夠降低實驗設計的規模,減少所需時間。我們可以大幅減小參數空間,與此同時并沒有明顯降低結果的準確性。在我們的案例中,實驗設計的規模從~5000減少到~2000個參數組合。SEMulator3D的自定義python步驟將這種類型的機器學習代碼整合到工藝模擬中,其結果可以導入半導體工藝模型的下一個步驟。

△圖4:根據刻蝕深度、晶圓傾角和等離子體入射角度分布來預測寄生電容的人工神經網絡(ANN)模型。測試數據的預測準確度為99.8%。衡量預測電容和實際電容之間差異的指標是絕對百分比誤差(APE)。75%測試案例的APE值為0.28%或更低。準確的機器學習模型可以幫助探索更小的參數空間,從而減少所需的時間和算力資源。

結論

使用Coventor SEMulator3D?在FinFET器件的柵極和源極/漏極之間引入虛擬空氣間隙,我們研究了空氣間隙對寄生電容的影響,并通過改變刻蝕工藝參數,研究了對空氣間隙體積和寄生電容的影響。隨后,結果被輸入到人工神經網絡中,以創建一個可以預測寄生電容的機器學習模型,從而減少為每個刻蝕參數值組合進行實驗設計的需求。

審核編輯黃宇

-

半導體

+關注

關注

334文章

27703瀏覽量

222628 -

電容

+關注

關注

100文章

6090瀏覽量

150986 -

晶體管

+關注

關注

77文章

9745瀏覽量

138896

發布評論請先 登錄

相關推薦

CAN通信節點多時,如何減少寄生電容和保障節點數量?

半大馬士革工藝:利用空氣隙減少寄生電容

深入解析晶振時鐘信號干擾源:寄生電容、雜散電容與分布電容

仿真的時候在哪些地方添加寄生電容呢?

在LF411CD的放大模塊出現輸出會發生振蕩,請問該元件輸入端(2端)與GND間的寄生電容多大?

普通探頭和差分探頭寄生電容對測試波形的影響

系統寄生參數對SiC器件開關的影響分析

引入空氣間隙以減少前道工序中的寄生電容

引入空氣間隙以減少前道工序中的寄生電容

評論