DC IVAC/ DC CIVAC指令用于將一個虛擬地址對應的cache line從data cache或是unified cache失效或清除失效到PoC點。N2 core硬件默認會將DC IVAC升級為DC CIVAC操作。

Point of Coherency (PoC)位于:確保系統中所有可以訪問內存的agent訪問這個地址可以看到同樣的copy的地方,不管它的訪問內存類型(memory type)和cache屬性(cacheable or non cacheable)是什么。

在很多系統中,它都位于系統主內存。

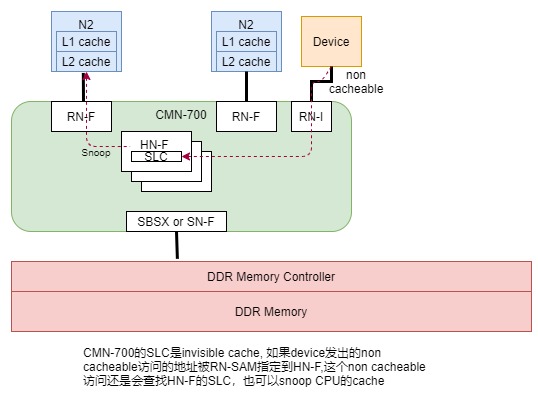

在一個N2+CMN-700的系統中,

CMN-700的system level cache (SLC)是invisible cache, 如果device發出的non cacheable訪問的地址被RN-SAM指定到HN-F,這個non cacheable訪問還是會查找HN-F的SLC,也可以snoop CPU的cache。

這是否意味著,這樣的系統的PoC點在CMN-700的SLC,而不需要在系統主內存呢?因為DC IVAC/ DC CIVAC只需要將數據失效/清除失效到SLC,不需要失效/清除失效掉SLC中對應的cache line,其他CPU和Device就可以看到同樣的copy了。

確實,如果系統中所有可以訪問內存的master都接到CMN-700的RN-F,RN-I, RN-D上,并且他們訪問的地址是在RN-SAM里面指定到HN-F,PoC只到SLC是可以的。

但是如果系統中有其他不接到CMN-700的master,或者它們訪問的地址RN-SAM里面不是指定到HN-F,那么就無法顯示PoC要求的:確保系統中所有可以訪問內存的agent訪問這個地址可以看到同樣的copy的地方,不管它的訪問內存類型(memory type)和cache屬性(cacheable or non cacheable)是什么。

因此,在N2+CMN-700的系統,DC IVAC/ DC CIVAC還是需要失效/清除掉SLC中對應的cache line。

CMN-700支持將這些cache maintanance operation (CMO)下傳到內存控制器,如果CMN-700之下還接有其他更低level的cache的話,下傳這些CMO可以進一步使CMO PoC的操作影響到更低level的cache。控制是否下傳是可以通過編程每個SN-F對應的HF-N寄存器cmn_hns_sam_sn_properties中的cmo_prop_en來實現。

-

控制器

+關注

關注

112文章

16448瀏覽量

179483 -

寄存器

+關注

關注

31文章

5363瀏覽量

121199 -

SAM

+關注

關注

0文章

113瀏覽量

33579 -

cache技術

+關注

關注

0文章

41瀏覽量

1087

發布評論請先 登錄

相關推薦

Arm Neoverse家族新增V1和N2兩大平臺,突破高性能計算瓶頸

什么是CMN?CMN中的PMU概述

Arm Neoverse CMN?700相干網狀網絡技術參考手冊

ARM Neoverse N2 PMU指南

Arm Neoverse N2汽車硬件技術概述

ARM Neoverse?N2軟件優化指南

Arm Neoverse V2參考設計版本C技術概述

Arm Neoverse? N2核心加密擴展技術參考手冊

ARM Neoverse?N2核心技術參考手冊

互聯網巨頭紛紛啟用Arm CPU架構,Arm最新Neoverse V1和N2平臺加速云服務器芯片自研

解密Arm Neoverse V1和Neoverse N2平臺為下一代基礎設施帶來計算變革

TWS耳機新的增長點在哪里

Arm發布新一代Neoverse數據中心計算平臺,AI負載性能顯著提升

Arm新Arm Neoverse計算子系統(CSS):Arm Neoverse CSS V3和Arm Neoverse CSS N3

Neoverse N2和CMN-700系統的PoC點在哪里?

Neoverse N2和CMN-700系統的PoC點在哪里?

評論