有關加法器的知識,加法器是用來做什么的,故名思義,加法器是為了實現加法的,它是一種產生數的和的裝置,那么加法器的工作原理是什么,為什么要采用加法器,下面具體來看下。

一、加法器的原理

加法器是為了實現加法的,即是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。如果加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。

對于1位的二進制加法,有五個的相關量:1,被加數A,2,被加數B,3,前一位的進位CIN,4,此位二數相加的和S,5,此位二數相加產生的進位COUT。前三個量為輸入量,后兩個量為輸出量,五個量均為1位。

對于32位的二進制加法,也有五個相關量:1,被加數A(32位),2,被加數B(32位),3,前一位的進位CIN(1位),4,此位二數相加的和S(32位),5,此位二數相加產生的進位COUT(1位)。

二、采用加法器的原因

如果需要實現32位的二進制加法,一種自然想法就是將1位的二進制加法重復32次(即逐位進位加法器),這么做無疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必須在第1位計算出結果后,才能開始計算;第3位必須在第2位計算出結果后,才能開始計算等。而最后的第32位必須在前31位全部計算出結果后,才能開始計算。這種方法使得實現32位的二進制加法所需的時間是實現1位的二進制加法的時間的32倍。

可見,上述方法是將32位的加法1位1位串行進行,需要縮短進行的時間,就要設法使上敘進行過程并行化。

逐位進位加法器,在每一位的計算時,都在等待前一位的進位。那么不妨預先考慮進位輸入的所有可能,對于二進制加法來說,就是0與1兩種可能,并提前計算出若干位針對這兩種可能性的結果。等到前一位的進位來到時,可以通過一個雙路開關選出輸出結果。這就是進位選擇加法器的思想。

提前計算多少位的數據為宜?

同為32位的情況:線形進位選擇加法器,方法是分N級,每級計算32/N位;平方根進位選擇加法器,考慮到使兩個路徑(1,提前計算出若干位針對這兩種可能性的結果的路徑,2,上一位的進位通過前面的結構的路徑)的延時達到相等或是近似方法,或是2345666即第一級相加2位,第二級3位,第三級4位,第四級5位,第五級6位,第六級6位,第七級6位;或是345677即第一級相加3位,第二級4位,第三級5位,第四級6位,第五級7位,第六級7位。

-

加法器

+關注

關注

6文章

183瀏覽量

30233 -

半加器

+關注

關注

1文章

29瀏覽量

8824 -

二進制加法

+關注

關注

0文章

4瀏覽量

1770

發布評論請先 登錄

相關推薦

十進制加法器,十進制加法器工作原理是什么?

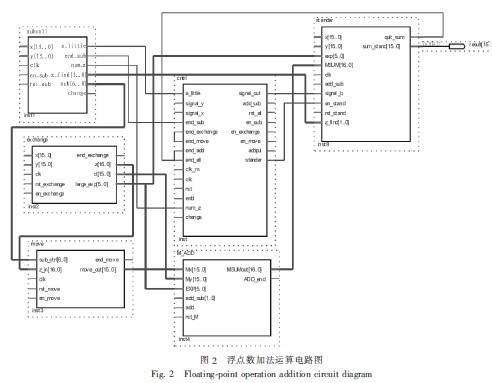

FPU加法器的設計與實現

同相加法器電路原理與同相加法器計算

加法器的原理及采用加法器的原因

加法器的原理及采用加法器的原因

評論