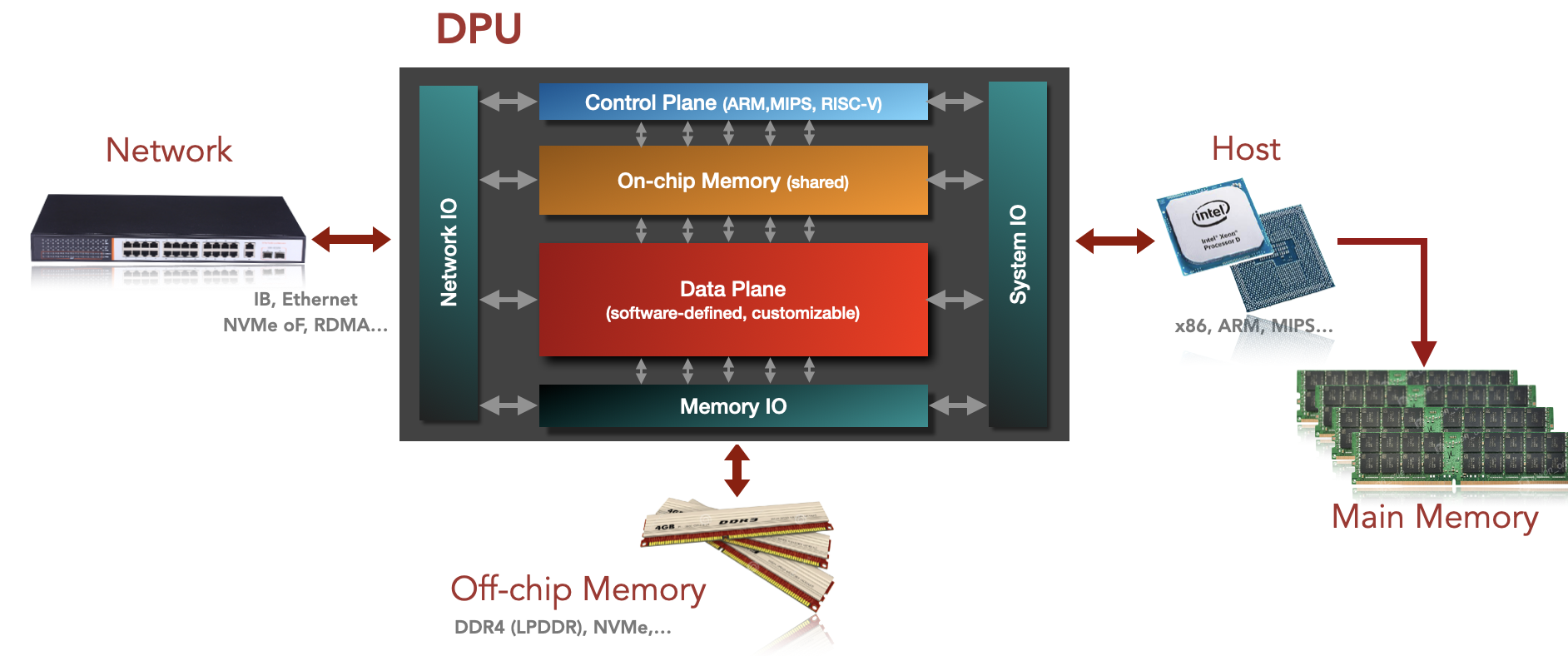

為了滿足“數(shù)據(jù)為中心”的設(shè)計(jì)理念,本節(jié)給出一個(gè)通用的DPU參考設(shè)計(jì)。目前DPU架構(gòu)的演化比較快,DPU既可以呈現(xiàn)為一個(gè)被動(dòng)設(shè)備作為CPU的協(xié)處理器,也可以作為一個(gè)主動(dòng)設(shè)備,承接Hypervisor的一些功能。尤其是容器技術(shù)、虛擬化技術(shù)的廣泛采用,DPU的角色已經(jīng)不僅僅是一個(gè)協(xié)處理器,而是呈現(xiàn)出更多的HOST的特征,比如運(yùn)行Hypervisor,做跨節(jié)點(diǎn)的資源整合,為裸金屬和虛擬機(jī)提供虛擬網(wǎng)絡(luò),數(shù)據(jù)安全,熱遷移等支撐。宏觀來(lái)看,DPU架構(gòu)至少可以分為以下幾個(gè)核心組成部分:

圖DPU架構(gòu)參考設(shè)計(jì)

一、控制平面

負(fù)責(zé)管理、配置,通常由通用處理器核來(lái)實(shí)現(xiàn)。控制平臺(tái)負(fù)責(zé)DPU設(shè)備運(yùn)行管理,以及計(jì)算任務(wù)和計(jì)算資源的配置。運(yùn)行管理通常包含設(shè)備的安全管理和實(shí)時(shí)監(jiān)控兩個(gè)主要功能。在安全管理方面支持支持如信任根、安全啟動(dòng)、安全固件升級(jí)以及基于身份驗(yàn)證的容器和應(yīng)用的生命周期管理等。在設(shè)備實(shí)時(shí)監(jiān)控方面,對(duì)DPU各子系統(tǒng)、數(shù)據(jù)平面中各處理核動(dòng)態(tài)監(jiān)測(cè),實(shí)時(shí)觀察設(shè)備是否可用、設(shè)備中流量是否正常,周期性生成報(bào)表,記錄設(shè)備訪問(wèn)日志核配置修改日志。

計(jì)算任務(wù)和計(jì)算資源配置方面,根據(jù)計(jì)算任務(wù)實(shí)施配置數(shù)據(jù)平面中處理單元間的通路,以及各處理單元參數(shù)。根據(jù)資源利用情況實(shí)時(shí)進(jìn)行任務(wù)調(diào)度以及在計(jì)算單元的映射和部署。同時(shí)DPU上層同時(shí)會(huì)支持多個(gè)虛擬機(jī),控制平面在任務(wù)部署時(shí)還要進(jìn)行虛擬設(shè)備的管理,考慮虛擬機(jī)間數(shù)據(jù)和資源隔離,記錄運(yùn)行狀態(tài)協(xié)助虛擬機(jī)熱遷移。最后,當(dāng)DPU集成第三方計(jì)算平臺(tái),如GPU、FPGA等,還需要參與部分卸載任務(wù)調(diào)度。

由于控制平面任務(wù)多樣,靈活性要求較高,算力要求較低,通常由通用處理器核來(lái)實(shí)現(xiàn),比如ARM、MIPS等核心。為便于用戶統(tǒng)一管理和配置DPU設(shè)備,提供較好的可編程性,通常會(huì)運(yùn)行標(biāo)準(zhǔn)Linux應(yīng)用程序。并且控制平面與數(shù)據(jù)平面數(shù)據(jù)交互驅(qū)動(dòng)程序需要進(jìn)行深度優(yōu)化,來(lái)提升控制平面與數(shù)據(jù)平面有效地交互,任務(wù)調(diào)度效率。

二、IO子系統(tǒng)

主要分為三個(gè)大類:

(1)系統(tǒng)IO,負(fù)責(zé)DPU和其他處理平臺(tái)(如X86、ARM處理器、GPU、FPGA等)或高速外部設(shè)備(如SSD)的集成。系統(tǒng)IO通常傳輸數(shù)據(jù)量較大對(duì)帶寬有著極高的要求,因此多基于PCIe來(lái)實(shí)現(xiàn)。系統(tǒng)IO接口分為兩大類:EP(Endpoint)類和RC(Root Complex)類。

EP類接口負(fù)責(zé)將DPU作為從設(shè)備與X86、ARM等處理平臺(tái)相連接。為了充分利用DPU上的內(nèi)部資源,此類接口要支持強(qiáng)大的硬件設(shè)備虛擬化功能,比如SR-IOV和VirtIO。并且可以靈活地支持多種類型的設(shè)備,如NIC、Storage、Compute設(shè)備等。

RC類接口負(fù)責(zé)將DPU作為主設(shè)備與加速平臺(tái)(如GPU、FPGA)或外設(shè)(SSD)相連接。通過(guò)此種方式將部分?jǐn)?shù)據(jù)處理卸載到第三方加速平臺(tái)GPU、FPGA中處理,通常數(shù)據(jù)量較大,需要支持較強(qiáng)的DMA方案。

(2)網(wǎng)絡(luò)IO,負(fù)責(zé)DPU與高速網(wǎng)絡(luò)相連接,主要是以太網(wǎng)或者FC為主。為了能應(yīng)對(duì)急劇增加的網(wǎng)絡(luò)帶寬,DPU中通常輔以專門的網(wǎng)絡(luò)協(xié)議處理核來(lái)加速網(wǎng)絡(luò)包的處理。包括L2/L3/L4層的ARP/IP/TCP/UDP網(wǎng)絡(luò)協(xié)議處理、RDMA、數(shù)據(jù)包交換協(xié)議、基本網(wǎng)絡(luò)虛擬化協(xié)議等,可以實(shí)現(xiàn)100G以上的網(wǎng)絡(luò)包線速處理。

(3)主存IO,負(fù)責(zé)緩存網(wǎng)絡(luò)IO和系統(tǒng)IO輸入輸出數(shù)據(jù),以及數(shù)據(jù)平面中間數(shù)據(jù)結(jié)果。也可作為共享內(nèi)存,實(shí)現(xiàn)不同處理核之間的數(shù)據(jù)通信。目前主存IO主要包含DDR和HBM接口類型,兩類接口,DDR可以提供比較大的存儲(chǔ)容量,可以提供512GB以上的存儲(chǔ)容量;HBM可以提供比較大的存儲(chǔ)帶寬,可以提供500GB/s以上的帶寬。兩種存儲(chǔ)接口相結(jié)合可以滿足不同存儲(chǔ)容量和帶寬的需求,但是需要精細(xì)的數(shù)據(jù)管理,這塊也是DPU設(shè)計(jì)中比較有挑戰(zhàn)的。

三、數(shù)據(jù)平面

主要負(fù)責(zé)高速數(shù)據(jù)通路的功能單元的集成,通常集成多個(gè)處理核。數(shù)據(jù)平面的功能主要分為五類:

1)高速數(shù)據(jù)包處理,主要對(duì)接收到的網(wǎng)絡(luò)數(shù)據(jù)包進(jìn)行如OvS(開(kāi)放式虛擬交換機(jī))解析、匹配和處理,以及RDMA遠(yuǎn)程數(shù)據(jù)傳輸加速等操作,和之前的網(wǎng)絡(luò)處理器NP功能類似,但是在性能上有更高的要求,處理帶寬線速要達(dá)到100G、200G甚至400G。同時(shí),在進(jìn)行有狀態(tài)數(shù)據(jù)處理時(shí)也有著更高的要求,如TCP協(xié)議,要求硬件記錄各連接信息,并能實(shí)現(xiàn)多連接間無(wú)縫切換。

2)虛擬化協(xié)議加速,支持SR-IOV、VirtIO和PV(Para-Virtualization)等虛擬化。支持網(wǎng)絡(luò)虛擬化VxLAN、Geneve Overlay卸載和VTEP等協(xié)議卸載。

3)安全加密,在線IPSec和TLS加密加速,以及多種標(biāo)準(zhǔn)加解密算法和國(guó)密算法。并且對(duì)于安全算法的處理性能有較高的要求,要達(dá)到網(wǎng)絡(luò)線速,從而不影響其它正在運(yùn)行的加速操作。

4)流量壓縮,對(duì)網(wǎng)絡(luò)數(shù)據(jù)包,或者要存儲(chǔ)的數(shù)據(jù),進(jìn)行實(shí)時(shí)地?cái)?shù)據(jù)壓縮/解壓縮處理,壓縮過(guò)程中還要完成地址的轉(zhuǎn)換和重映射等操作。或者在線完成數(shù)據(jù)流變換處理,如面向多媒體流、CDN(內(nèi)容分發(fā)網(wǎng)絡(luò))和4K/8K IP視頻的“Packet Pacing”流量整形加速等。

5)其他算法加速。除了上述網(wǎng)絡(luò)、安全協(xié)議外還要支持NVMe等存儲(chǔ)協(xié)議,業(yè)務(wù)相關(guān)的處理卸載也呈增長(zhǎng)趨勢(shì),如大數(shù)據(jù)分析SQL加速。

四、DPU設(shè)計(jì)的關(guān)鍵

數(shù)據(jù)平面是整個(gè)DPU設(shè)計(jì)的關(guān)鍵,也是DPU設(shè)計(jì)中最有挑戰(zhàn)的模塊。主要面臨四個(gè)挑戰(zhàn):

1)數(shù)據(jù)中心的工作負(fù)載復(fù)雜多樣,數(shù)據(jù)平面支持的處理核種類要足夠多,不僅包括網(wǎng)絡(luò)、存儲(chǔ)、安全和虛擬化等基礎(chǔ)設(shè)施服務(wù),另外業(yè)務(wù)相關(guān)的處理也在加速向DPU平臺(tái)卸載。

2)高并發(fā)性數(shù)據(jù)處理,數(shù)據(jù)中心承載的業(yè)務(wù)多且復(fù)雜,多虛擬機(jī)多種類業(yè)務(wù)并發(fā)要求數(shù)據(jù)平面集成足夠數(shù)量的核心,規(guī)模要達(dá)到幾百個(gè)核心規(guī)模。隨著數(shù)據(jù)中心數(shù)據(jù)量的不斷增加,對(duì)處理性能提出越來(lái)越多的挑戰(zhàn),DPU數(shù)據(jù)平面在處理核規(guī)模上要具有非常強(qiáng)的可擴(kuò)展性。

3)復(fù)雜的片上互聯(lián)系統(tǒng),隨著DPU數(shù)據(jù)平面處理核數(shù)量的增加,再加之高并發(fā)處理線程運(yùn)行,同時(shí)還要兼顧好數(shù)據(jù)平面數(shù)據(jù)處理的靈活,這就要求處理核之間的數(shù)據(jù)交互既要靈活又要兼顧高帶寬。處理核之間的數(shù)據(jù)互聯(lián),以及核間的數(shù)據(jù)一致性成為另一設(shè)計(jì)難題。

4)高效簡(jiǎn)易的編程方式,數(shù)據(jù)中心業(yè)務(wù)的復(fù)雜多變決定了DPU數(shù)據(jù)平臺(tái)可編程性的硬性需求。一方面要兼顧計(jì)算效率,必須直觀表達(dá)出并發(fā)處理任務(wù),充分利用計(jì)算資源。另一方面要兼顧DPU的易用性,盡量采用高級(jí)語(yǔ)言進(jìn)行編程,易于設(shè)計(jì)、開(kāi)發(fā)和維護(hù)。

總之,DPU數(shù)據(jù)平面需要一種大規(guī)模敏捷異構(gòu)的計(jì)算架構(gòu)。這一部分的實(shí)現(xiàn)也處在“百家爭(zhēng)鳴”的階段,各家的實(shí)現(xiàn)方式差別較大,有基于通用處理器核的方式,有基于可編程門陣列FPGA的方式,也有基于異構(gòu)眾核的方式,還有待探索。

-

DPU

+關(guān)注

關(guān)注

0文章

368瀏覽量

24260

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FE1.1S的國(guó)產(chǎn)替代芯片DPU1.1S 高性能、低功耗4口高速USB2.0HUB控制器芯片 USB拓展塢等應(yīng)用之選

利用NVIDIA DPF引領(lǐng)DPU加速云計(jì)算的未來(lái)

在NVIDIA BlueField-3 DPU上運(yùn)行WEKA客戶端的實(shí)際優(yōu)勢(shì)

《金融街午餐會(huì)》年終特別節(jié)目——新質(zhì)生產(chǎn)力大路演,“數(shù)據(jù)搬運(yùn)高手”DPU如何打破AI時(shí)代算力瓶頸?

安謀科技發(fā)布“玲瓏”DPU和新一代VPU

中科馭數(shù)分析DPU在云原生網(wǎng)絡(luò)與智算網(wǎng)絡(luò)中的實(shí)際應(yīng)用

IaaS+on+DPU(IoD)+下一代高性能算力底座技術(shù)白皮書(shū)

中科馭數(shù)CEO鄢貴海:從計(jì)算系統(tǒng)的三個(gè)視角重新審視DPU的核心價(jià)值

芯片軟件全上陣 DPU“全家桶”來(lái)了!中科馭數(shù)成功舉辦2024產(chǎn)品發(fā)布會(huì)

中科馭數(shù)發(fā)布高性能DPU芯片K2-Pro

NVIDIA DPU編程入門開(kāi)課儀式在澳門科技大學(xué)成功舉辦

DPU技術(shù)賦能下一代AI算力基礎(chǔ)設(shè)施

明天線上見(jiàn)!DPU構(gòu)建高性能云算力底座——DPU技術(shù)開(kāi)放日最新議程公布!

中科馭數(shù)DPU技術(shù)開(kāi)放日秀“肌肉”:云原生網(wǎng)絡(luò)、RDMA、安全加速、低延時(shí)網(wǎng)絡(luò)等方案組團(tuán)亮相

FPGA-Based DPU網(wǎng)卡的發(fā)展和應(yīng)用

DPU特征結(jié)構(gòu)系列(二)一種DPU參考設(shè)計(jì)

DPU特征結(jié)構(gòu)系列(二)一種DPU參考設(shè)計(jì)

評(píng)論