Allegro和 Sigrity 軟件最新發(fā)布了一系列的產(chǎn)品更新(SPB17.4 QIR4 release)。我們將通過實例講解、視頻演示讓您深入了解 Allegro PCB Editor、Allegro System Capture、Allegro Package Designer Plus(本期內(nèi)容)、Sigrity Aurora、Sigrity SystemSI(本期內(nèi)容)、Sigrity SystemPI等產(chǎn)品的新功能及用法,助力提升設(shè)計質(zhì)量和設(shè)計效率。

Cadence Sigrity SystemSI 的模塊化設(shè)計允許用戶方便地搭建任意拓撲,支持最新的 IBIS/Spice/ TouchStone/IBIS-AMI 模型。

Sigrity SystemSI 可以對高速串行通道進行眼圖和誤碼率分析,對系統(tǒng)中的任意參數(shù)進行掃描,得到最優(yōu)化配置,并且集成了 PCI-E、SATA 等工業(yè)標準,直接對仿真結(jié)果進行判別。

Sigrity SystemSI 可以對整個 DDR 系統(tǒng)進行準確的 SSN 分析,集成 JEDEC 標準,自動為用戶量測 SI 參數(shù),并以此為基礎(chǔ),進行自動化時序分析。

面對 10Gbps 以上的高速通道傳輸?shù)耐ㄓ?a target="_blank">信號,我們大多數(shù)會采用差分方式設(shè)計,這樣可以持續(xù)更快速地傳輸大比特量數(shù)據(jù)。

Sigrity SystemSI 的高速串行和并行模塊,可以適應高速信號傳輸通道的標準分析流程,支持 AMI 算法建模接口,能夠更高效地創(chuàng)建發(fā)送端和接收端模型,同時內(nèi)部的參數(shù)定義方式將芯片設(shè)計和業(yè)界高速傳輸標準(DDR/HDMI/USB/PCI-E等)以流程化的方式提供給用戶,最終滿足用戶對系統(tǒng)總體 BER 的預測,并判斷抖動、噪聲是否都在指定的容限內(nèi),實現(xiàn)更簡單易用的流程化操作。

Sigrity SystemSI

系統(tǒng)信號仿真亮點——

2#為GDDR6 接口增加基于 JEDEC 自動化分析功能

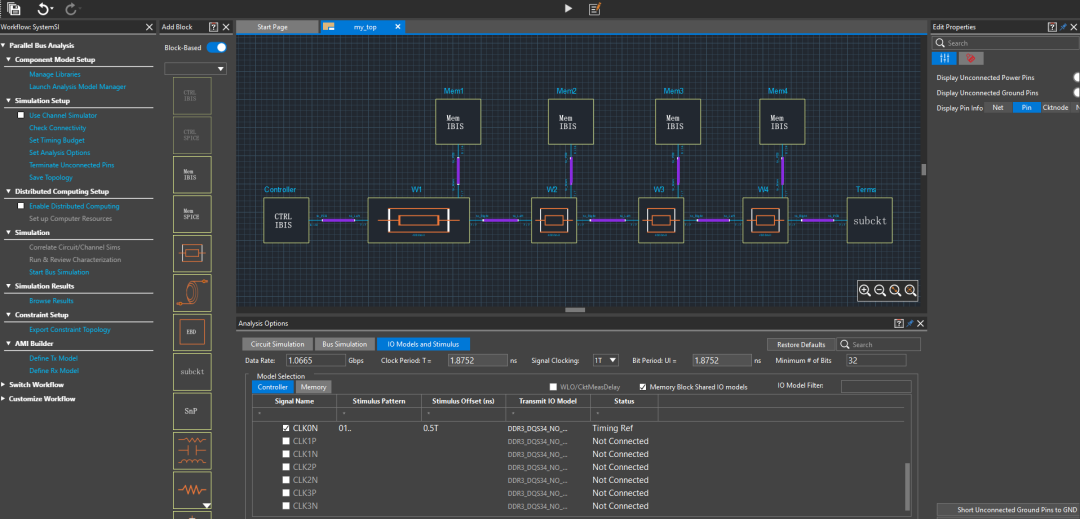

Wbench_SPB17.4_QIR4 更新之后,Sigrity SystemSI 可以支持為 GDDR6 接口增加基于 JEDEC 協(xié)議的自動化分析功能。接下來使用一個 DDR 的例子來說明 GDDR6 分析流程及內(nèi)存塊支持多個模型等功能。

實例講解 · 圖文版

1

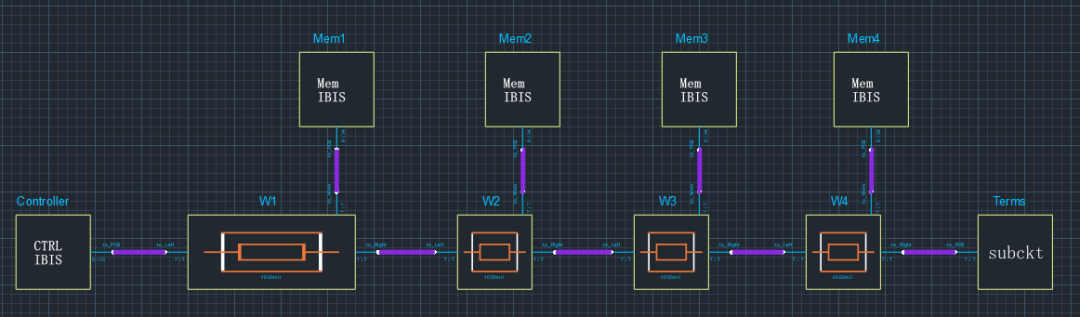

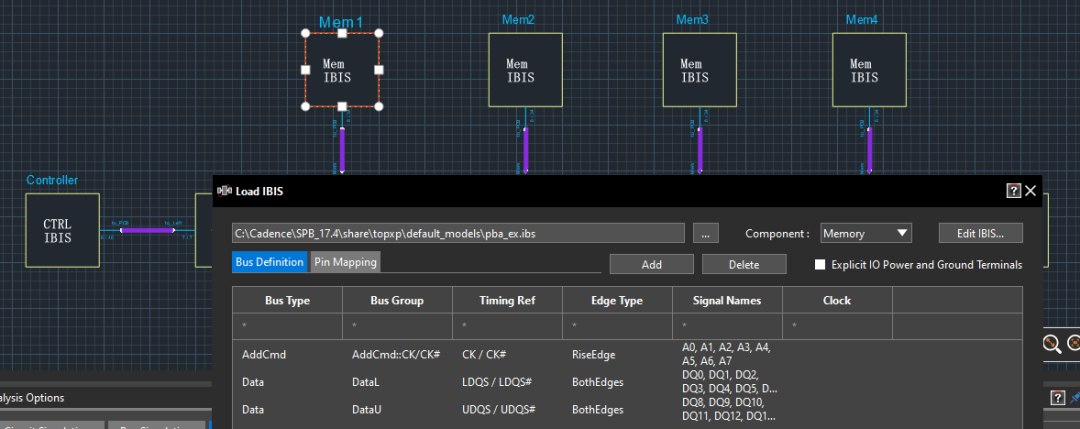

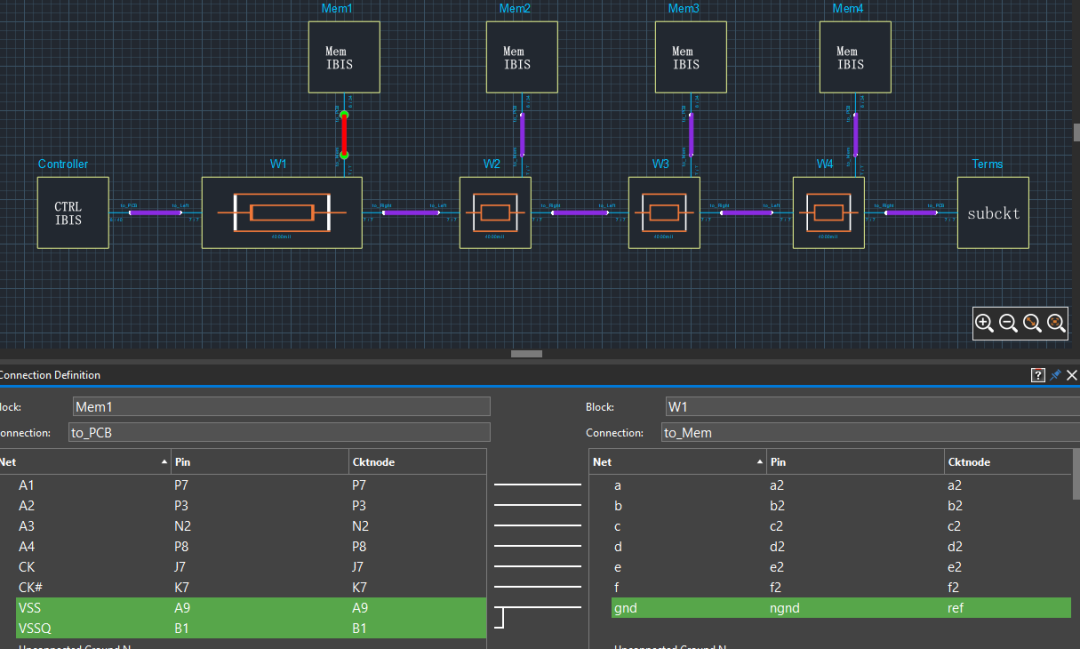

之前版本中拓撲的內(nèi)存塊僅支持分配相同的 IBIS 模型文件,現(xiàn)在的版本中不同位號的內(nèi)存塊可以分配給不同的 IBIS 型號,相當于不同的內(nèi)存可以使用不同公司/廠商的 IBIS 模型文件。

2

拓撲中不同組的內(nèi)存塊可以分配不同的 IBIS 組件模型文件。

3

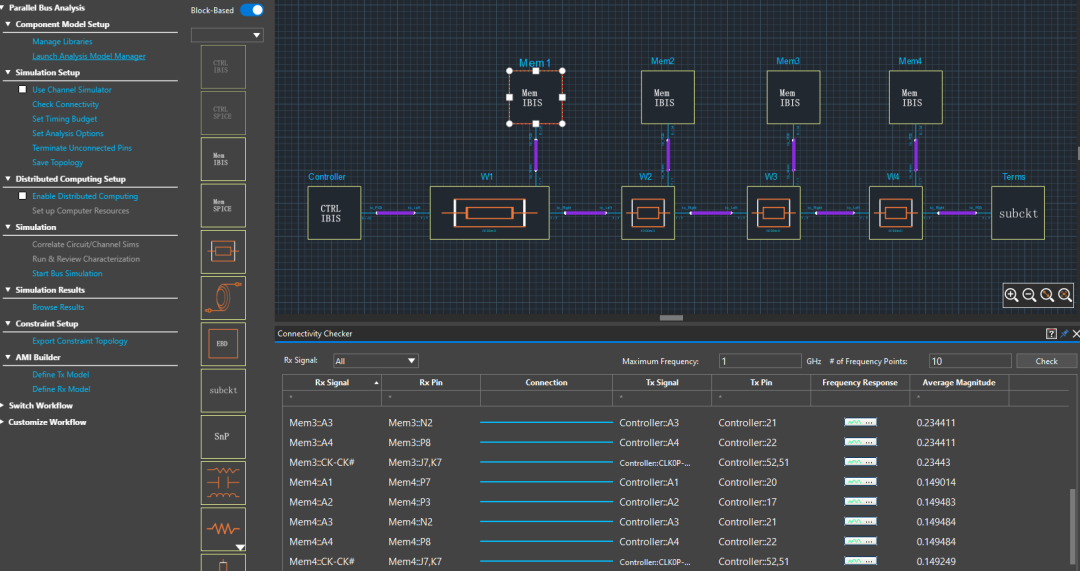

檢查內(nèi)存仿真模塊之間的電氣連接,檢查互連信號發(fā)送接收的數(shù)據(jù)完整度。

4

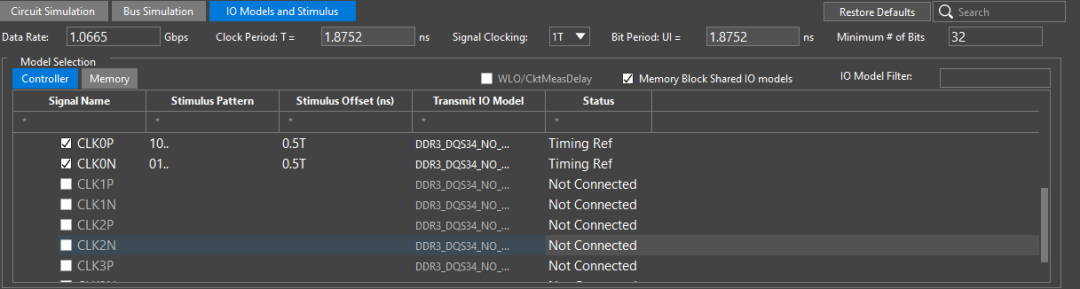

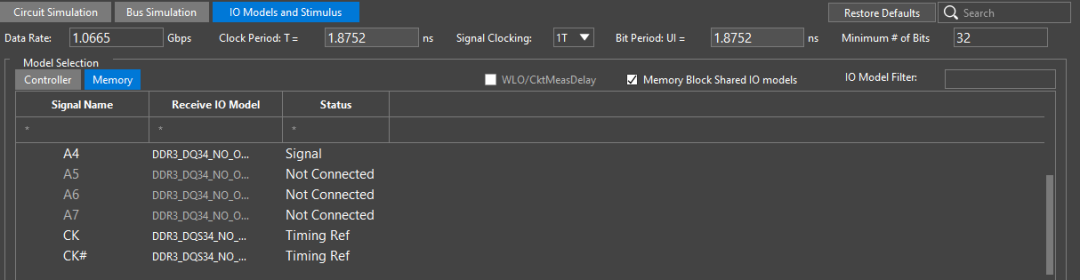

設(shè)置控制器模型參數(shù)、數(shù)據(jù)速率、信號周期以及發(fā)送和接收端的 IBIS 模型。

5

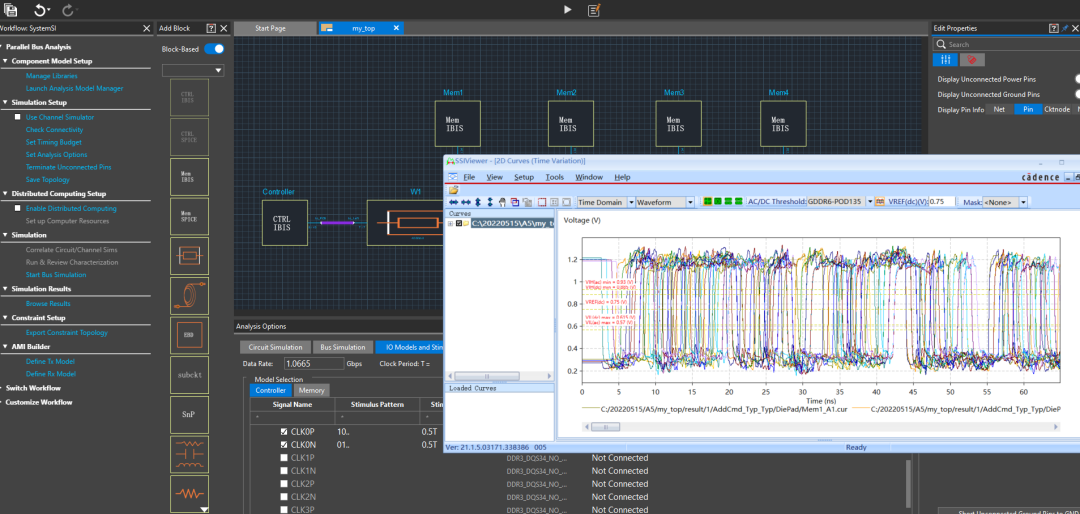

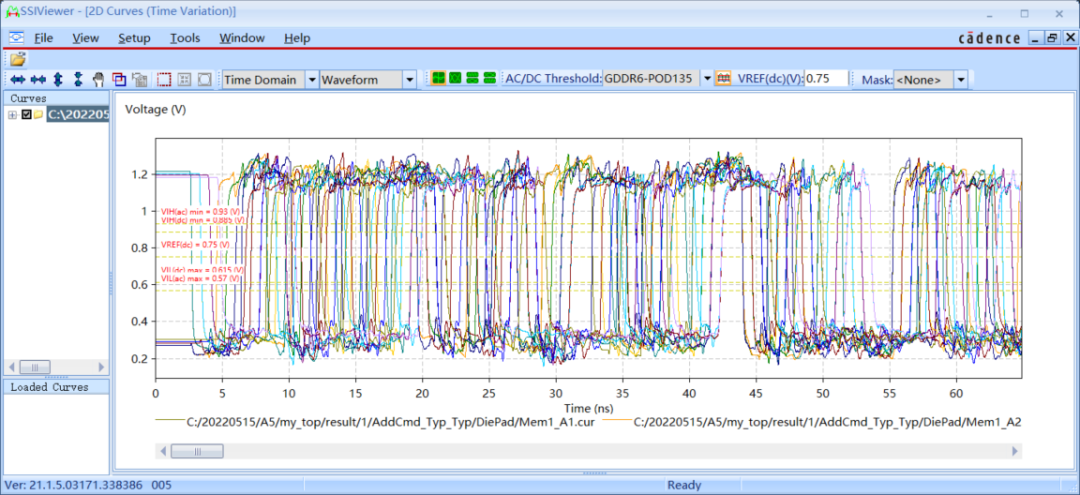

設(shè)置參數(shù)完成以后,執(zhí)行仿真可以看到仿真完成后的結(jié)果波形數(shù)據(jù)。

6

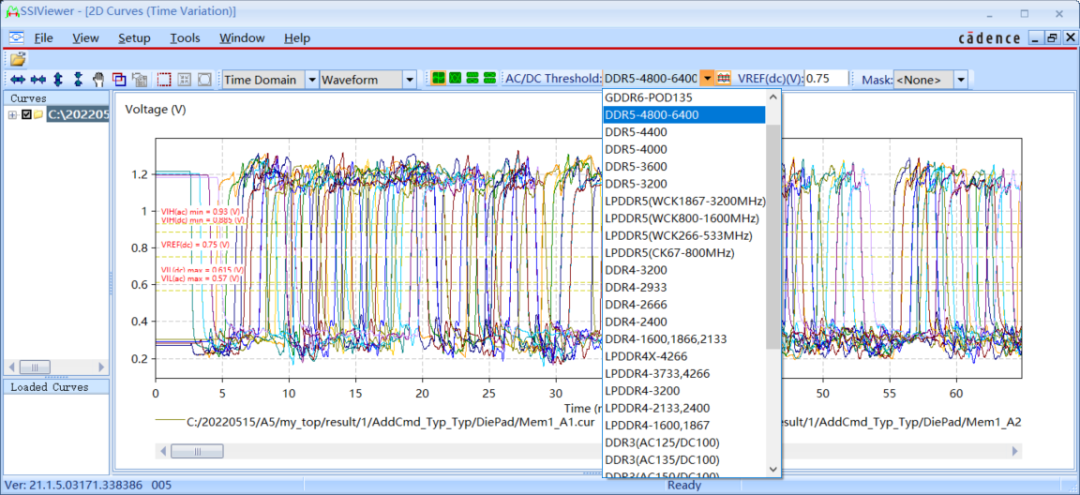

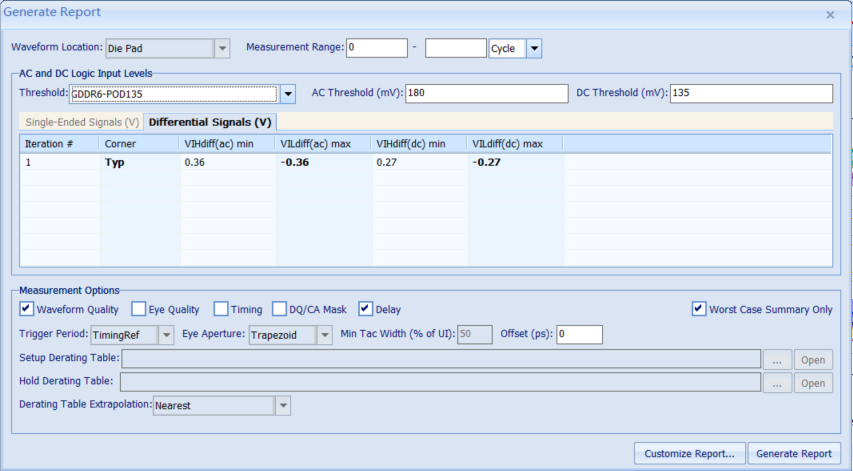

調(diào)用新增加的 GDDR6 接口模板分析波形數(shù)據(jù)。

7

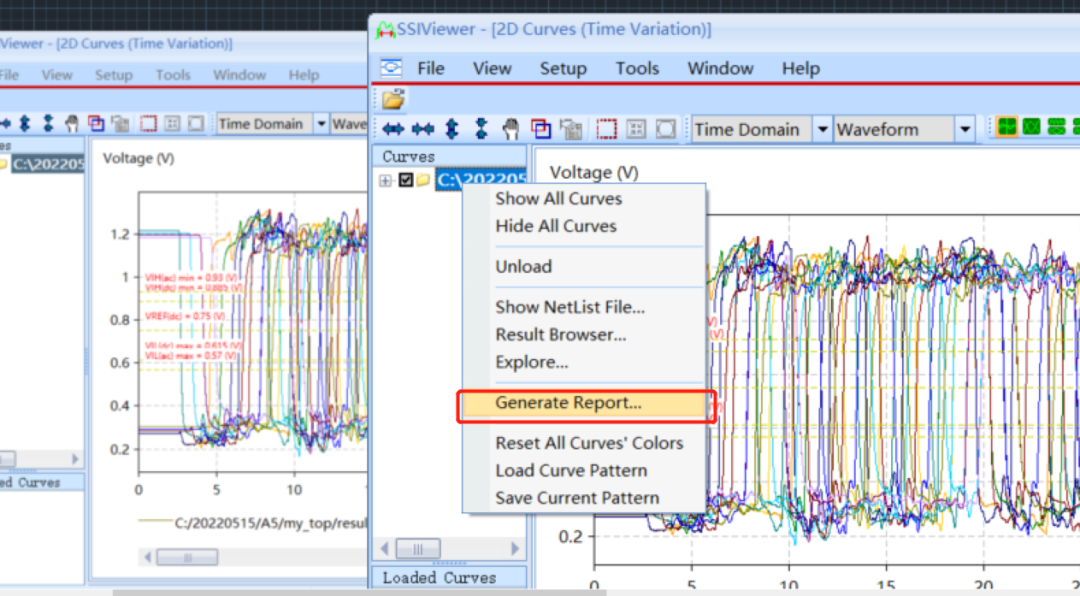

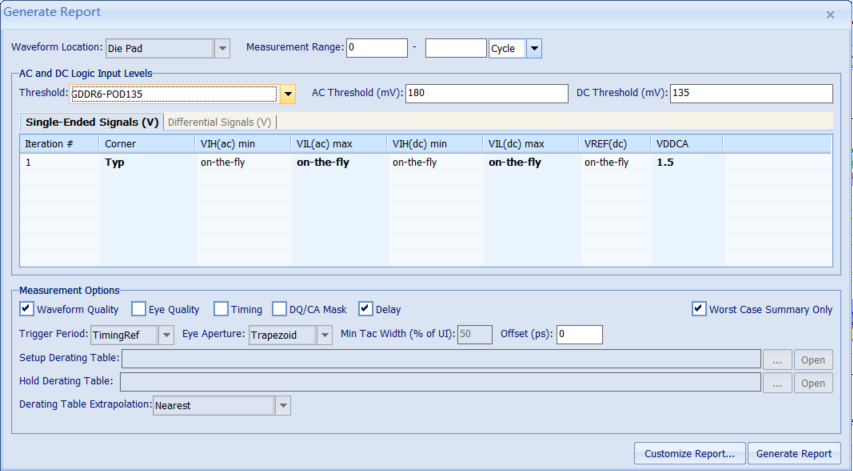

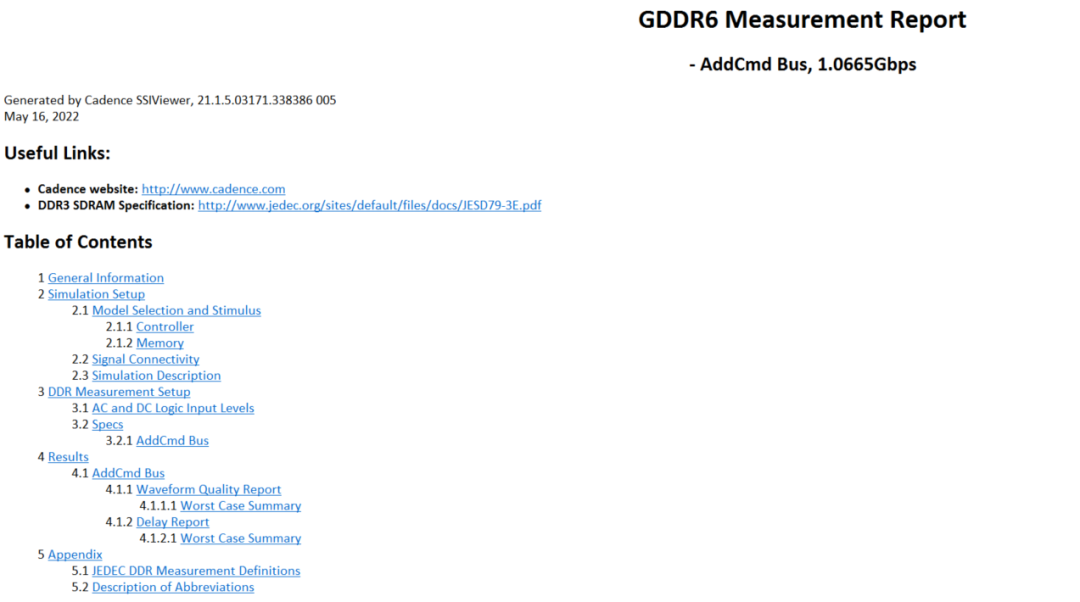

支持生成 GDDR6 基于 JEDEC 自動化分析功能的報告。

8

支持生成 GDDR6 基于JEDEC 自動化分析功能的報告。

9

支持生成 GDDR6 基于JEDEC 自動化分析功能的報告。

-

allegro

+關(guān)注

關(guān)注

42文章

662瀏覽量

145557

發(fā)布評論請先 登錄

相關(guān)推薦

下一代高端顯卡標配,容量和速度雙翻倍的GDDR7登場!

滿足廣西地區(qū)的配網(wǎng)自動化分布式DTU集中式DTU

RFID技術(shù)助力物流自動化分揀:提升速度、效率與準確性

Cadence Allegro 17.4PCB阻抗分析功能操作說

英偉達推出搭載GDDR6顯存的GeForce RTX 4070顯卡

Allegro X 23.11 版本更新 I PCB 設(shè)計:梯形布線的分析性能提升

Allegro X 23.11 版本更新 I PCB 設(shè)計:DFA_BOUND 用于 DFA 規(guī)則設(shè)定

美光出樣業(yè)界容量密度最高新一代 GDDR7 顯存

有辦法自動為CYUSB4347-BZXC更新固件嗎?

AMD RDNA4或采用GDDR6顯存,Navi 4X或Navi 4C具備216個計算單元?

Rambus推GDDR7內(nèi)存控制器IP滿足AI應用需求

英偉達、AMD新款顯卡或仍配備2GB GDDR7顯存

利用Sigrity Aurora進行PCB布線后的仿真分析-阻抗及寄生參數(shù)析

2022 Sigrity SPB 17.4 版本更新 I SystemSI 為GDDR6接口增加基于JEDEC自動化分析功能

2022 Sigrity SPB 17.4 版本更新 I SystemSI 為GDDR6接口增加基于JEDEC自動化分析功能

評論