2023年5月9日至11日,首屆EDA國際研討會(International Symposium of EDA,ISEDA)于在中國南京隆重舉辦。作為業內知名的數字前端驗證 EDA 解決方案供應商,思爾芯受邀參加這場中國首個 EDA 領域專業盛會,并積極參與了會議的各個環節。與來自國內外的知名學者、高校專家和企業領袖齊聚一堂,共同探討 EDA 領域的前沿技術和未來發展趨勢。 在此次研討會上,思爾芯總裁林鎧鵬先生發布了一場重要的技術演講,介紹了當前超大規模集成電路驗證中必備的硬件仿真器和原型驗證系統的部分核心技術,對大型多核組網的編譯流程遇到的技術挑戰,提供了一些相關技術方案和實現思路。

在此次研討會上,思爾芯總裁林鎧鵬先生發布了一場重要的技術演講,介紹了當前超大規模集成電路驗證中必備的硬件仿真器和原型驗證系統的部分核心技術,對大型多核組網的編譯流程遇到的技術挑戰,提供了一些相關技術方案和實現思路。

在整個數字芯片開發的過程中,功能驗證是非常重要的一部分,其中包含了硬件仿真、原型驗證等多種驗證手段。隨著集成電路設計規模的增長,涉及的芯片系統也變得越來越復雜,單個 FPGA 大多數無法提供足夠的邏輯資源,這就不可避免地要進行設計分割,將設計映射到多個 FPGA 上來進行驗證和調試,也意味著設計編譯會變得非常耗時和困難。工程師想要盡可能快地完成編譯和驗證工作,同時保證設計的正確性和可靠性。這就需要充分考慮如快速綜合、架構驅動的設計分割、時延驅動的 TDM 分配、擁塞預測的互聯組網等多方面的因素。

思爾芯有著高效的編譯、分割和驗證技術可以有效解決上述挑戰。通過引入機器學習,自適應系統組網分割,并行多策略編譯等技術,可更快的獲得更高的成功機會。相關技術不但可應用于硬件仿真和原型驗證,對于AI加速,HPC系統設計也有明顯的參考價值。

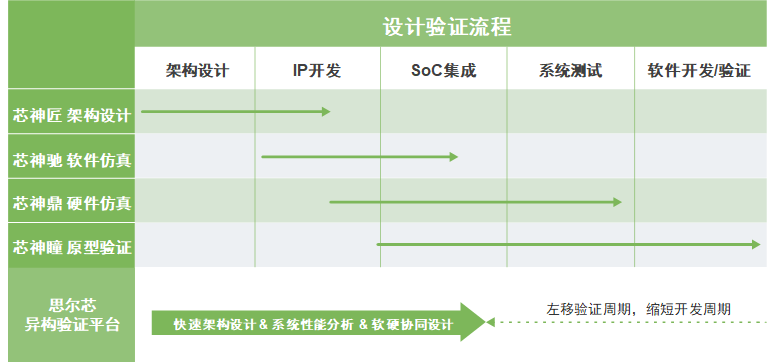

思爾芯將這一系列技術應用于自研的原型驗證(Prodigy芯神瞳)、硬件仿真( OmniArk 芯神匠)等 EDA 工具上。這些技術的應用可以更好地支持工程師進行編譯和驗證工作,提高整個 SoC 設計的效率和質量,大大縮短整個芯片開發周期。思爾芯作為數字前端驗證 EDA 解決方案供應商,其解決方案涵蓋芯片設計驗證的完整流程,從早期的芯片規劃驗證到軟硬件協同驗證都有相應的解決方案。豐富的產品線包含架構設計、軟件仿真、硬件仿真、原型驗證和驗證云等,有著完善的功能驗證布局。尤其是在原型驗證方面有著近 20 年商業 EDA 工具產品技術和市場經驗,對此有著成熟的技術與更前沿的見解。因此,思爾芯在該領域一直有著豐富的經驗和技術,可以為學術界和工業界提供創新性的解決方案。

思爾芯總裁林鎧鵬先生發布的重要技術演講使得在場觀眾深受啟發,這將有助于推動 EDA 技術的發展,并架起 EDA 研究人員和芯片開發人員之間富有成效和新穎的溝通交流橋梁。同時,林鎧鵬表示,思爾芯將通過持續支持 EDA 學術競賽,推進產學研合作等方式,培養更多 EDA 人才,研究更多前沿算法,共同開發更先進的驗證工具。 //

-

組網

+關注

關注

1文章

359瀏覽量

22416 -

思爾芯

+關注

關注

0文章

123瀏覽量

1314

發布評論請先 登錄

相關推薦

EDA精英挑戰賽賽果公布!思爾芯“戰隊”薪火相承斬獲“麒麟杯”

思爾芯亮相IIC Shenzhen,創新解決方案賦能RISC-V芯片設計

思爾芯賽題正式發布,邀你共戰EDA精英挑戰賽!

思爾芯芯神瞳原型驗證系統通過上海市高新技術成果轉化項目認定

上海立芯亮相ISEDA 2024,共話EDA發展“芯”問題

直擊ISEDA 2024現場:思爾芯的EDA技術與教育并行

年度技術突破EDA公司!思爾芯憑先進解決方案榮獲2024中國IC設計成就獎

演講預告|思爾芯邀您共聚中國IC領袖峰會,一起探索“芯”未來

ISEDA現場|思爾芯發布重要技術演講:如何應對大型多核組網的編譯挑戰?

ISEDA現場|思爾芯發布重要技術演講:如何應對大型多核組網的編譯挑戰?

評論