關于 Verilog HDL 的認知

常見認知(錯誤)

正確認知

HDL:hardware Description

- HDL 語言僅是對已知硬件電路的文本表現形式編寫前,對所需實現的硬件電路“ 胸有成竹 ”

- Verilog HDL 的基本功能之一是描述可綜合的硬件電路。

- 相比 C 語言,最顯著的區別在于 HDL 語言具備以下硬件設計的基本概念:

Verilog HDL 用于可綜合描述的語句

- always

- if-else

- case

- assign

這里課件上的 for 不可用于綜合,這點不敢茍同

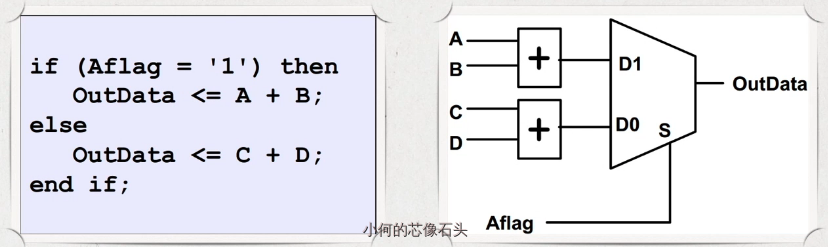

if-else 相關語句的硬件結果映射及優化

if-else 硬件結構

- 映射的硬件結構: Multiplexing Hardware -> 多路選擇器, 輸出結果由輸入的選擇條件決定

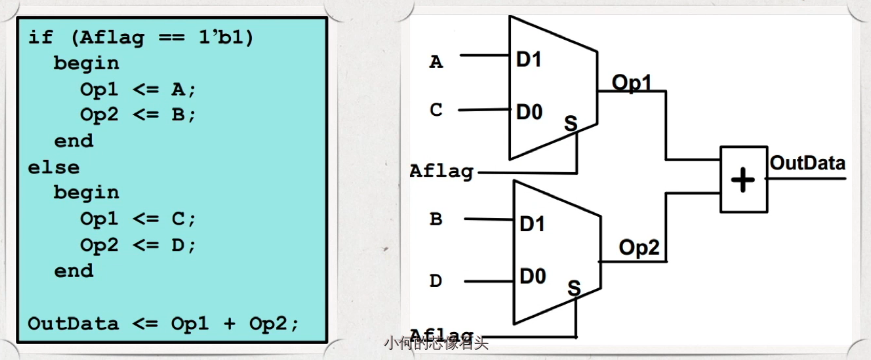

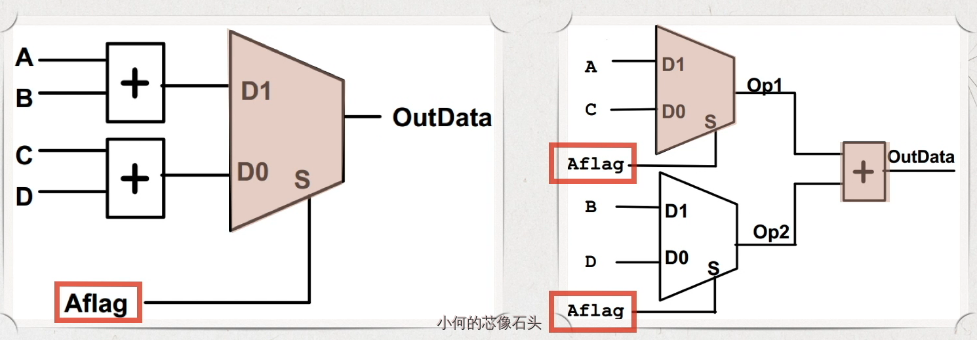

- 重構 if-else 映射的硬件結構:減少了一個加法器,減少了硬件面積:

trade-off :但是在這種情況下,電路的傳播延遲 -> 數據通路的延遲沒改變,但是控制通路的傳播也變成了一個選擇器和加法器之和,如果 aflag 到來延遲晚,則后一種電路沒前者好的性能沒這么好:

單 if 語句-無優先級的判斷結構

如以下代碼:

always@(a or b or c or d or sel)begin

z=0;

if(sel[3])

z=d;

else if(sel[2])

z=c;

else if(sel[1])

z=b;

else if(sel[0])

z=a;

end

硬件結構為:

多 if 語句-具有優先級的判斷結構

如以下代碼:

always@(a or b or c or d or sel)begin

z=0;

if(sel[0])z=a;

if(sel[1])z=b;

if(sel[2])z=c;

if(sel[3])z=d;

end

硬件結構為:

最后一級選擇信號具有最高的優先級,具有優先級的多選結構會消耗組合邏輯

- 若某些設計中,有些信號要求先到達(如關鍵使能信號,選擇信號等),而有些信號需要后到達(如慢速信號,有效時間較長的信號等),此時則需要采用此結構

- 設計方法:最高優先級給最遲到達的關鍵信號

此處結合阻塞賦值與非阻塞賦值去想都是成立的

case-無優先級的判斷結構

如以下代碼:

always@(a or b or c or d or sel)begin

case(sel)

2'b00: z=d;

2'b01: z=c;

2'b10: z=b;

2'b11: z=a;

default: z=1'b0;

endcase

end

- 與單 if 語句的區別: 條件多為互斥

- 多用于指令譯碼電路

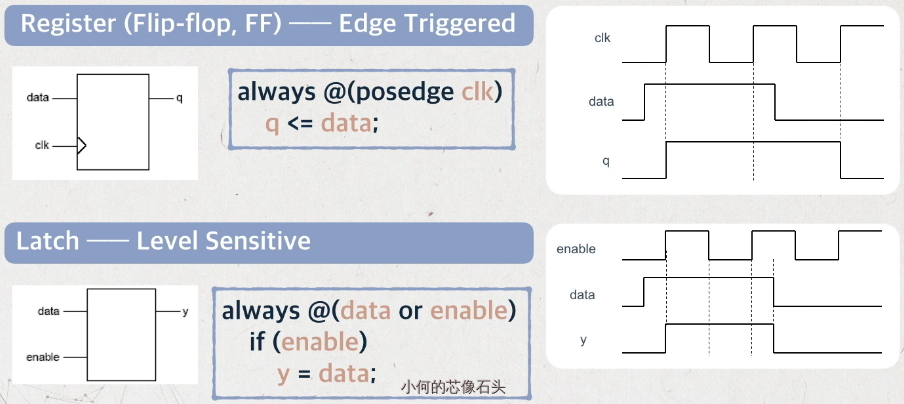

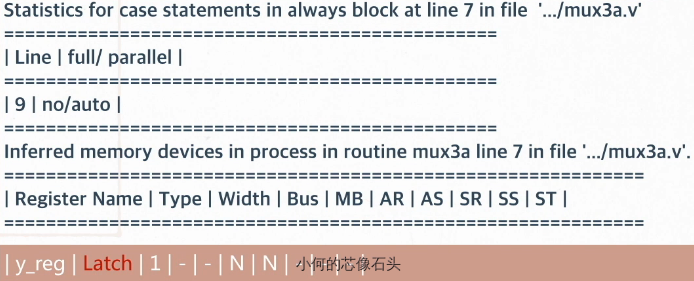

慎用 Latch

綜合器很難解釋 latch,因此,除非特殊用途,一般避免引入 latch.

一般只在異步電路與門控時鐘中用到

- latch 由電平觸發,非同步控制.在使能信號有效時,latch 相當于通路,在使能信號無效時 latch 保持輸出狀態。DFF 由時鐘沿觸發,同步控制。

- latch 容易產生毛刺(glitch),DFF 則不易產生毛刺。

- latch 將靜態時序分析變得極為復雜。

- 一般的設計規則時:在絕大多數設計中避免產生 latch。latch 最大的危害在于 不能過濾毛刺 。這對于下一級電路時極其危險的。所以,只要能用 D 觸發器的地方,就不用 latch。

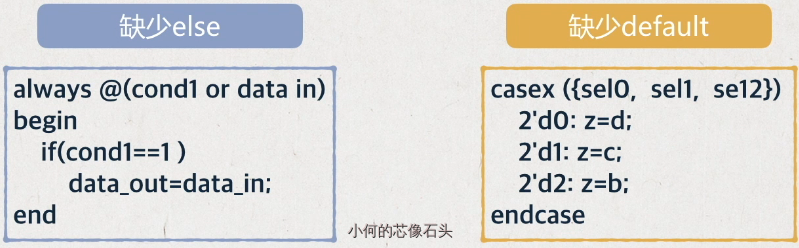

- 易引入 latch 的途徑:使用不完備的條件判斷語句

所以防止產生非目的性 latch 的措施:

- 使用完備的 if-else 語句

- 為每個輸入條件設計輸出操作,為 case 語句設置 default 操作

- 仔細檢查綜合器生成的報告,latch 會以 warning 的形式報告

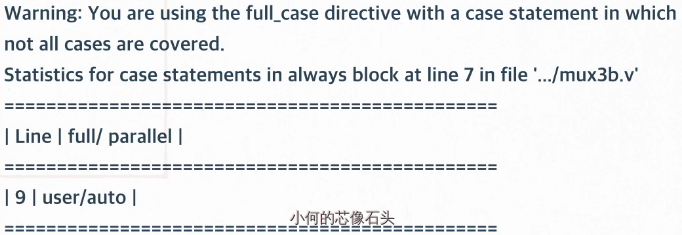

利用綜合器指令指定電路結構

full-case

對如紅綠燈等只有紅綠黃三種情況下,采用 2bit 的狀態編碼則會產生分支賦值不完備的情況:

always@(a or b or c or sel)begin

case(sel)

2'b00: y=a;

2'b01: y=b;

2'b10: y=c;

endcase

end

此時現實的狀態已經完備了,但是從數字電路角度出發會有一個 2'b11 下的 latch

此時使用 full-case:

- full-case: 告訴綜合器,當前 case 結構所列條件已完備

always@(a or b or c or sel)begin

case(sel) // synopsys full_case

2'b00: y=a;

2'b01: y=b;

2'b10: y=c;

endcase

end

此時綜合器結果:

則不會推斷出 latch

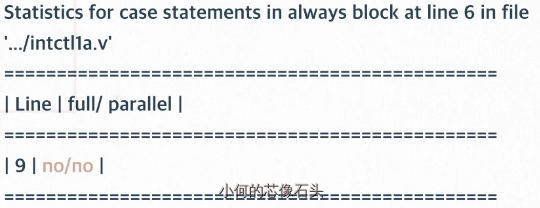

parallel_case

當 case 語句中的分支條件不互斥,則 case 語句存在優先級,如:

always@(irq)begin

int = 3'b0;

casez(irq)

3'b1??: int[2]=1'b1;

3'b?1?: int[1]=1'b1;

3'b??1: int[0]=1'b1;

endcase

end

綜合器報告:

使用 parallel-case 原語:告訴 DC,所有條件互斥,并行且無優先級

always@(irq)begin

int = 3'b0;

casez(irq) // synopsys parallel_case

3'b1??: int[2]=1'b1;

3'b?1?: int[1]=1'b1;

3'b??1: int[0]=1'b1;

endcase

end

合理使用 parallel case 約束,可以條件譯碼邏輯

邏輯復制-均衡負載

通過邏輯賦值,降低關鍵信號的扇出,進而降低該信號的傳播延遲,提高電路性能:

trade-off: 資源消耗

資源共享-減少面積

若電路中存在較多公共單元,可以通過資源共享來減少面積:

但一般共享會導致性能下降

資源順序重排-降低傳播延時

對到達延遲大的信號,可以重排其電路順序以降低傳播延時,提高性能:

如圖,假設 A 來得比較晚,就可以將其盡可能放在后面,隱藏他的延遲

":?"僅用于連線,always 用于邏輯運算

盡可能使用 always 來描述電路,assign 僅僅用來實現連線,如:

assign a = (b==1)?((c&&d)? 1'b1:1'b0):1'b0;

與 always 塊描述的:

always@(*) begin

if(b==1'b1)

if(c&&d == 1'b1)

a=1'b1;

else

a=1'b0;

else

a=1'b0;

end

關于 assign 和三目運算符:

- 僅用于信號連線

- 難以閱讀,且多層嵌套后很難被綜合器解釋

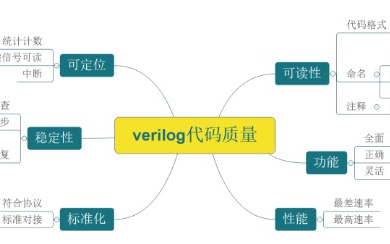

可綜合風格對代碼的要求

完整的 always 敏感信號列表

- 所有的組合邏輯或所存的 always 結構必須由敏感信號列表.其中必須包括所有的輸入信號

- 原因: 綜合過程將產生要給取決于除命案列表中所有其它值的結構,它將可能在行為仿真和門級仿真間產生潛在的失配.

每個 always 敏感信號列表對應一個時鐘

- 在綜合過程中,每個 Verilog always 敏感信號列表只能對應一個時鐘。

- 原因:這是將每一個過程限制在單一寄存器類型的要求,有利于邏輯綜合和時序分析

不允許 Wait 聲明和# delay 聲明

- Wait 聲明語句,無論時清楚還是含糊,都不能用于可綜合設計。

- 原因:從 RTL 級轉換到 gate 級的綜合工具一般都不支持 Wait 聲明和# delay 聲明,為了有效的綜合,這些語句應該避免。

- 例外:在不需要進行綜合的行為模塊中,如測試模塊,表示行為的虛擬期間模塊中可以使用。

在時序電路中必須使用非阻塞賦值(<=)

在組合邏輯中必須使用阻塞賦值(=)

模塊劃分

分開異步邏輯與同步邏輯

- 建議分開異步邏輯與同步邏輯

- 原因:簡化綜合時的問題,簡化約束和編碼難度

- 例外:不可應用于非綜合模塊中(例如:總線模塊,總線監視器或是模擬模塊)除非他們被設計來綜合仿真。

分開控制邏輯和存儲器

- 建議分開控制邏輯與存儲器邏輯為獨立模塊

- 原因:存儲器一般由 memory compiler 生成,便于高層的存儲器模塊的使用和便于重新描述為不同的存儲器類型。混用不利于綜合,不利于方便更換工藝庫和平臺。

-

寄存器

+關注

關注

31文章

5363瀏覽量

121166 -

觸發器

+關注

關注

14文章

2003瀏覽量

61347 -

HDL語言

+關注

關注

0文章

47瀏覽量

8957 -

dff

+關注

關注

0文章

26瀏覽量

3451 -

多路選擇器

+關注

關注

1文章

22瀏覽量

6559

發布評論請先 登錄

相關推薦

10個嵌入式小技巧 教你寫出高質量代碼!

高質量代碼的設計特點

如何編寫高質量的Javascript代碼

教你如何書寫高質量的Verilog代碼?

教你如何書寫高質量的Verilog代碼?

評論