本文作者:

DSG Product Engineering Group 劉杰

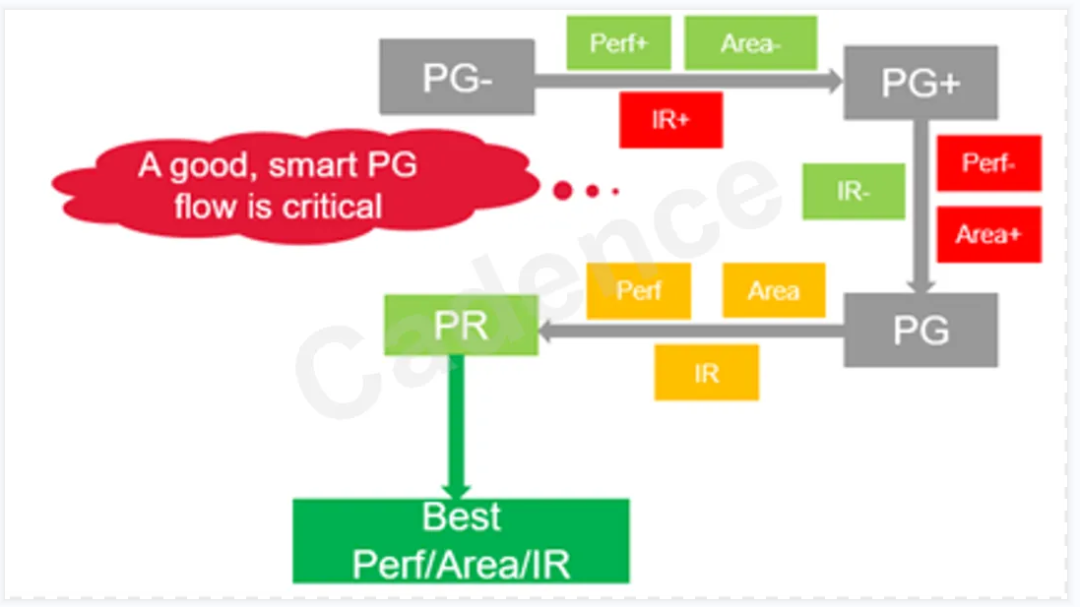

我們知道,一塊芯片的性能通常通過頻率、功耗、面積(即 PPA)三個方面去評估。在芯片設計過程中,工程師經常會對頻率,面積進行調整,但是很少會對芯片供電網絡(即 PG)進行比較大的調整,甚至在一些情況下明知道目前的 PG 可能不是最優的,工程師也沒有動力去調整,為什么呢?

因為在傳統的設計方法下,想要設計一個滿足各方面要求的 PG 網絡,是需要花費大量時間的。

“

1

一方面是設計一個合理的 PG 網絡本身需要較高的試錯成本,工程師需要對其中的每個參數進行精確計算,甚至拼湊才可能得到符合要求的結果。所以一套成熟的 PG 腳本都是經過十幾甚至幾十個版本的不斷打磨迭代最終形成的。

“

2

第二方面是 PG 腳本運行費時,動則十幾甚至幾十個小時的運行時間,也是設計過程中的一大痛點。

那我們有沒有什么解決方案,可以幫助工程師用原來十分之一甚至更少的時間設計出一個合格的電源網絡,并且可以根據不同的設計要求快速調整呢?

答案便是由 Cadence 提供的新型電源網絡設計方法 —— PSDL。

?

?什么是 PSDL?

PSDL 是 PG Structure Description Language 的簡稱,顧名思義,它是 Innovus 中一種全新的電源網絡結構的描述語言。

PSDL 主要包含兩部分的內容:

|

1 |

每層金屬電源走線的樣式; |

|

2 |

不同層金屬電源走線的連接關系。當我們能夠把上面兩部分的內容都說清楚的時候,芯片的電源網絡其實自然就形成了。 |

PSDL 的工作模式以及相比傳統 PG 產生

流程,它有什么樣的優點?

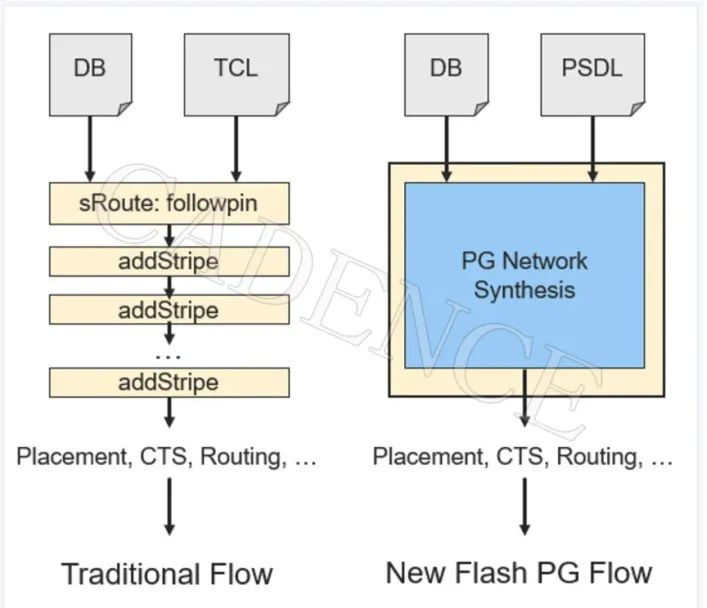

在介紹 PSDL 的優點之前,我們首先對比一下 PSDL 與傳統流程的區別。如下圖:

傳統流程:

在 floorplan 階段,通過一條條執行以 addStripe 為核心的命令的方式,完成 PG 創建。

PSDL流程:

在 floorplan 階段,讀入完整的 PSDL 文件,然后調用 Innovus 內部的 flash PG 引擎,一次性生成 PG 網絡。

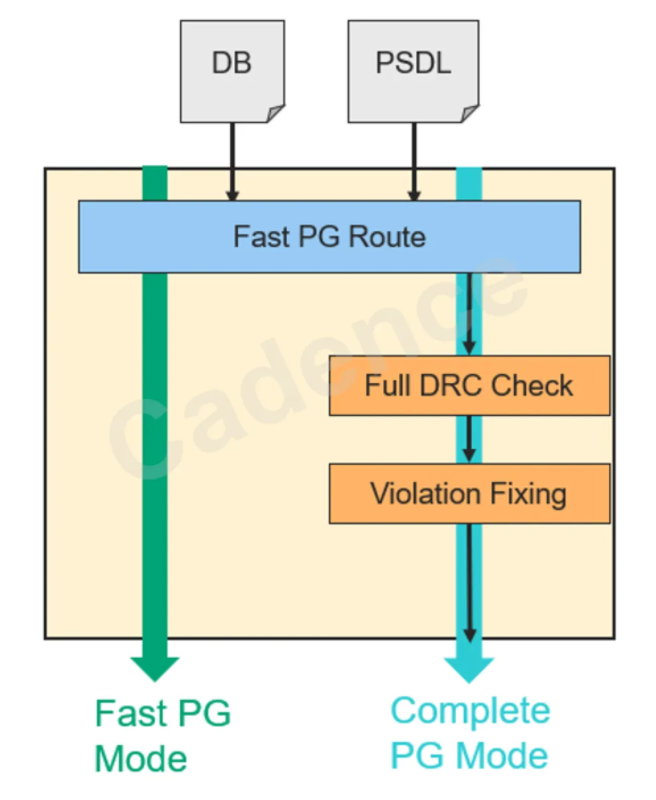

其中 flash PG 引擎工作時又分為兩種模式,快速模式(fast mode)和完整模式(complete mode)。其中快速模式用于快速產生 PG,幫助工程師檢查 PG pattern 是否符合設計要求并進行功耗分析;完整模式是在快速模式的基礎上,工具嘗試檢查并處理 PG 產生的 DRC,希望可以在修理 DRC 的基礎上保證 PG 連接性。工程師可以根據不同的需求場景,選擇使用不同的模式,充分發揮 PSDL 的優勢。

· PSDL 的優點

?

相比 TCL 腳本,更加便于理解和書寫,便于工程師快速學習應用。

?

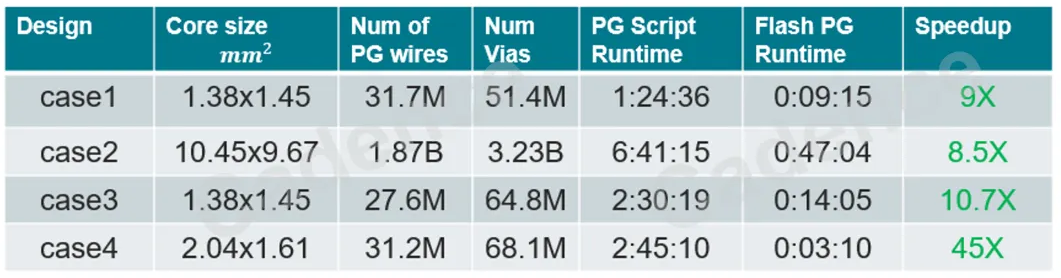

運行速度更快。PSDL 調用新的 Flash PG 引擎可以大幅提升 PG 生成速度,相比傳統的 addStripe 腳本方式普遍可以提升 10 倍左右。

?

通用性高,不依賴于芯片的大小及 floorplan 等信息。針對不同的設計需求,不同的工藝,通過一些微小的調整可以實現快速遷移復用。

?

自動從 LEF 文件中提取不同層金屬的物理信息。減少工程師重復的測量,計算等基礎工作,讓工程師有更多精力專注在 PG 結構設計方面。

下面是不同客戶的實際案例測試結果,發現新的 Flash PG 引擎在運行速度方面普遍可以提升 10 倍左右。同時我們也發現,當芯片的 PG 結構越復雜,并且造成傳統 PG 腳本越臃腫時(如 case 4),PSDL 展現出的優勢也更加明顯。

?

?· PSDL 包含哪些內容?

一個完整的 PSDL 文件主要包括 VARIABLE、PATTERN、AREA、REGION。其中,PATTERN 和 REGION 是必須的部分,其他部分可以根據實際情況進行增減。

?

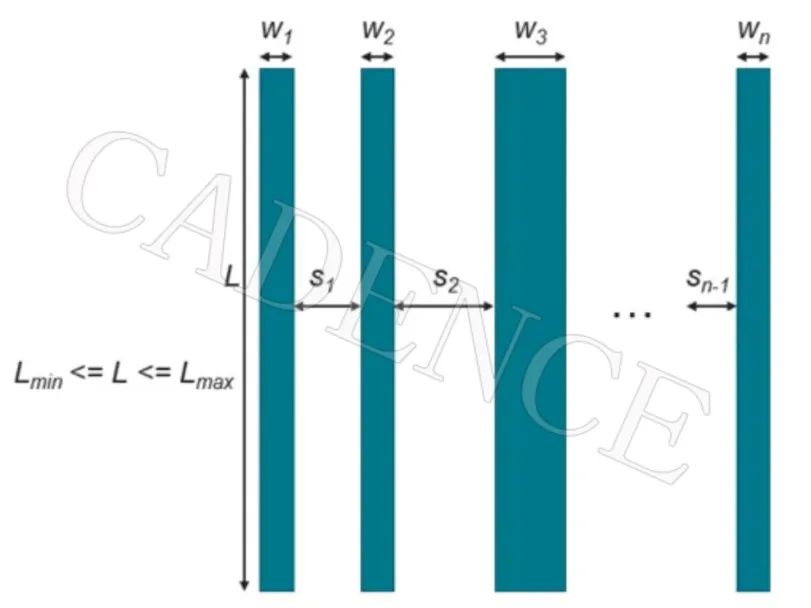

PATTERN:

用于描述 PG 中每一層金屬走線的具體結構樣式;包括名稱,類型,走線方向,線寬,間距,長度等基礎信息。

?

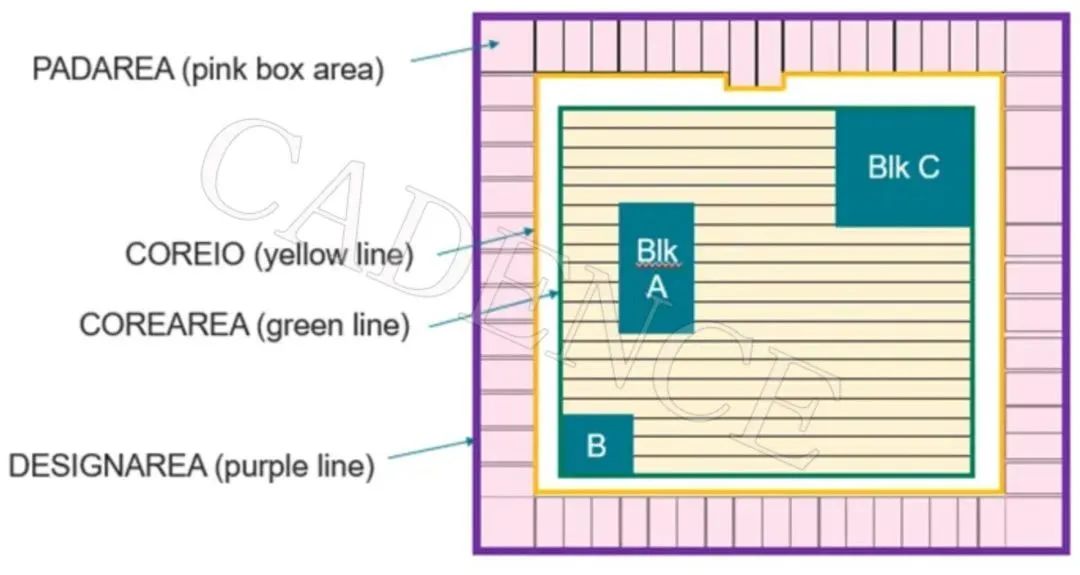

REGION:

用于描述在一個具體的區域,產生某種類型的 PG 網絡結構,主要包括所選區域,金屬層信息等。其中區域選擇可以是芯片中的任何區域,比如一個 block,instance,或者是一個 cell。這種通過單個指令便可實現在特定區域產生 PG 的方式,大大減輕了傳統方式中用腳本命令進行面積計算的工作量,進一步提升工作效率,減少工具運算時間。

?

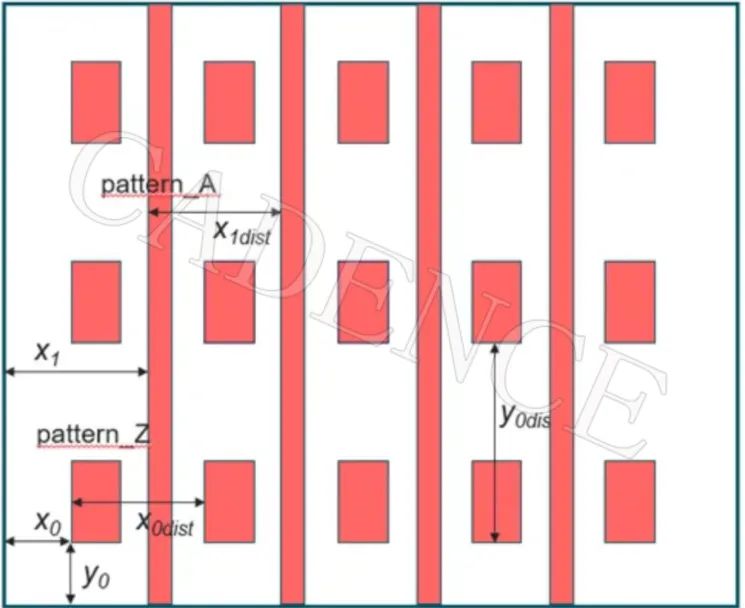

METAL:

用于描述具體的一層中,所走金屬線的類型及位置。如下圖,表示在選定區域中,M3 上面vdd 使用前面定義的 pattern_Z(STAPLE類型)和 pattern_A(STRIPE)。其中初始偏移量、間距、數量可以由 OFFSET、STEPDISTANCE、SIZE 等進行定義。

?

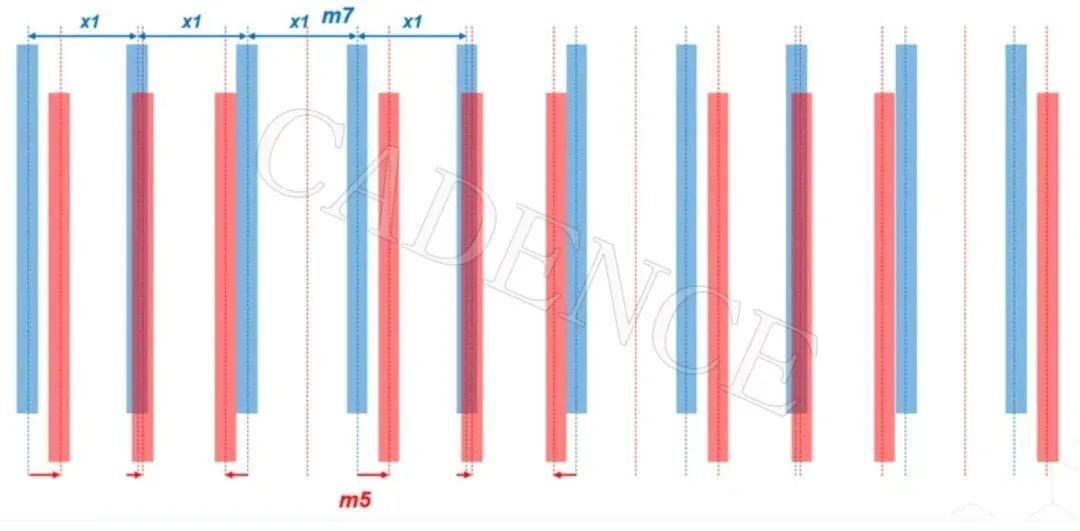

FOLLOW 和 ALIGNMENT:

作為 PSDL 中的另一大亮點,工程師可以通過 FOLLOW 和 ALIGNMENT 描述不同金屬線的相對位置關系,實現更加智能化的 PG 設計。通過這種方式,不但可以減少不必要的手動計算工作,也可以保證不同層之間的連接性,同時在需要調整時也非常容易。

PSDL 相比傳統方式,不但在運行速度上展現出巨大優勢,而且使得電源網絡設計更容易,維護和更新更方便靈活,它將對目前的后端實現流程產生影響。未來,PSDL 將和機器學習技術緊密融合,助力芯片工程師進一步提高芯片 PPA 的同時,有效解決電壓降過大等電源網絡問題。

關于 Cadence

Cadence 是電子系統設計領域的關鍵領導者,擁有超過 30 年的計算軟件專業積累。基于公司的智能系統設計戰略,Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計概念成為現實。Cadence 的客戶遍布全球,皆為最具創新能力的企業,他們向超大規模計算、5G 通訊、汽車、移動設備、航空、消費電子、工業和醫療等最具活力的應用市場交付從芯片、電路板到完整系統的卓越電子產品。Cadence 已連續九年名列美國財富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請訪問公司網站www.cadence.com。

2023 Cadence Design Systems, Inc. 版權所有。在全球范圍保留所有權利。Cadence、Cadence 徽標和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標志均為 Cadence Design Systems, Inc. 的商標或注冊商標。所有其他標識均為其各自所有者的資產。

-

Cadence

+關注

關注

65文章

930瀏覽量

142454

原文標題:更快,更強,更智能:Cadence 新型電源網絡設計方法介紹

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SOLIDWORKS 2025更強勁的性能優勢簡介

Wolfspeed榮獲世紀電源網行業大獎

一文解析LISN人工電源網絡

吹田電氣(深圳)有限公司亮相電源網(亞洲)工程師技術高峰論壇

更快、更小、更節能,開關電源迎來測試挑戰

4G新型智能電表是什么?

網絡模塊的安裝方法

人工智能神經網絡芯片的介紹

Cadence擴充系統IP產品組合,推出NoC以優化電子系統連接性

沒開玩笑!高速信號不能參考電源網絡這條規則,其實很難做到

沒開玩笑!高速信號不能參考電源網絡這條規則,其實很難做到

海洋儀器參加電源網2024年高新電源技術研討會-北京站圓滿結束

更快,更強,更智能:Cadence 新型電源網絡設計方法介紹

更快,更強,更智能:Cadence 新型電源網絡設計方法介紹

評論