交錯式ADC轉換器絕對是推動更高效接口的一部分。交錯式ADC轉換器為系統設計人員提供了多種優勢。然而,隨著轉換器帶寬的增加,需要在FPGA或ASIC中處理大量數據。必須有一些有效的方法來處理轉換器中的所有數據。在采樣速率在千兆采樣范圍內的轉換器中繼續使用LVDS接口變得不切實際。因此,JESD204B是將大量數據從轉換器傳輸到FPGA或ASIC的良好、高效方法。

讓我們花點時間離開界面,看看交錯。在通信基礎設施中,除了對DPD(數字預失真)等線性化技術有更寬的帶寬要求外,還不斷推動更高采樣速率的ADC,以允許多頻段、多載波無線電。在軍事和航空航天領域,更高的采樣速率ADC允許多用途系統,可用于通信、電子監控和雷達等。在工業儀器儀表中,對更高采樣速率ADC的需求總是在增加,以便可以精確測量更高速的信號。首先,讓我們了解交錯式ADC的基礎知識。

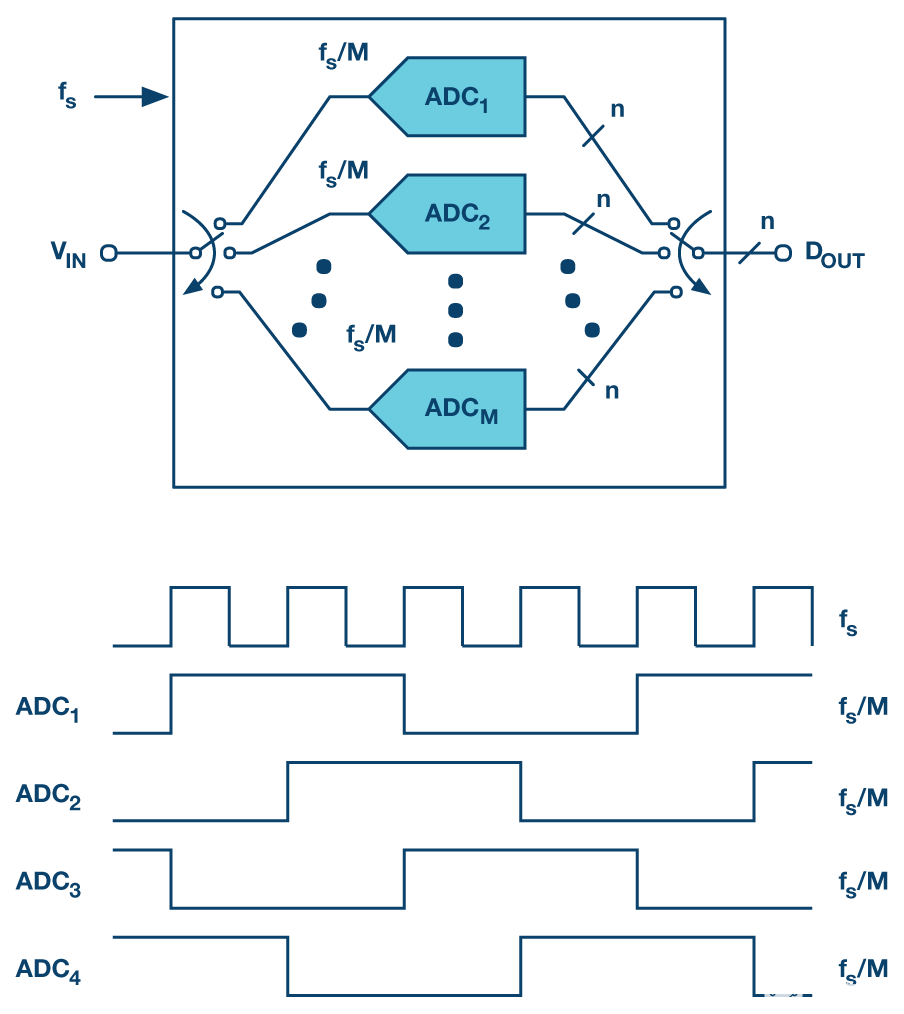

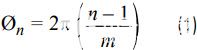

利用m個ADC可以將有效采樣速率提高m 倍。 為了簡單易懂,我們只關注兩個ADC的情況。在這種情況下,如果兩個ADC的采樣速率為fS交錯,所得采樣率僅為2fS.這兩個ADC必須具有時鐘相位關系才能正確交錯。時鐘相位關系由公式1決定,其中n是特定的ADC,m是ADC的總數。

例如,交錯連接兩個采樣速率為250MSPS的ADC,以實現500MSPS的采樣速率。在這種情況下,公式1可用于推導兩個ADC的時鐘相位關系,由公式2和3給出。

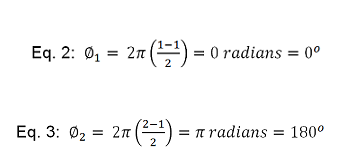

現在我們知道了時鐘相位關系,可以檢查樣本的構造。圖1直觀地顯示了兩個250MSPS交錯ADC的時鐘相位關系和樣本結構。

圖1

兩個交錯式250MSPS ADC – 基本圖

請注意 180° 時鐘相位關系以及樣本的交錯方式。輸入波形由兩個ADC交替采樣。在這種情況下,交錯是通過使用500MHz時鐘輸入實現的,該輸入被分頻為<>。分頻器負責將時鐘所需的相位發送到每個ADC。

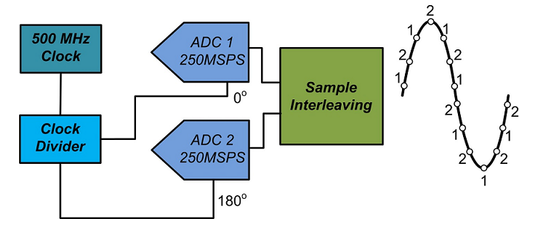

圖 2 顯示了此概念的另一個表示形式。

圖2

兩個交錯式 ADC – 時鐘和采樣

通過交錯這兩個250MSPS ADC,采樣速率提高到500MSPS。這將轉換器奈奎斯特區的寬度從125MHz擴展到250MHz,使可用工作帶寬翻倍。增加的操作帶寬帶來了許多優勢。無線電系統可以增加支持的頻段數量;雷達系統可以提高空間分辨率,測量設備可以實現更大的模擬輸入帶寬。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606038 -

轉換器

+關注

關注

27文章

8745瀏覽量

148057 -

adc

+關注

關注

99文章

6534瀏覽量

545768

發布評論請先 登錄

相關推薦

交錯式ADC的基礎知識

有ADC和傳感器的基礎知識嗎?

交錯式功率因數校正

ADC轉換器的基礎知識詳細資料說明

交錯ADC:揭開謎團

交錯式ADC:基礎知識

交錯式ADC:基礎知識

評論