CPU運行時間是寶貴的資源,我們要把有限的CPU時間投入到更有意義的事情中去。

在我們進行嵌入式開發(fā)的過程中,你一定干過這幾件事:用GPIO模擬某種通信接口,比如SPI等;用空循環(huán)來實現(xiàn)延時delay;空等寄存器的關鍵狀態(tài)位。也許是出于無奈,比如所使用的芯片沒有硬件SPI或通道不夠,亦或者此時CPU除了空轉(zhuǎn)并沒有其它事情要作,但是我們一定要有這樣的意識:這是在浪費CPU資源。

CPU是嵌入式系統(tǒng)的核心,但是它不必深入?yún)⑴c到每一個細節(jié)中去。記住:CPU是片上所有硬件資源的統(tǒng)領者,而非事必躬親的苦力。我們要學會盡最大可能充分利用片上硬件資源,甚至在芯片外部擴展一些專門的硬件電路來完成功能設計。

本章振南將通過幾個實例來向大家說明如何減輕CPU負擔,而用片內(nèi)片外的硬件來實現(xiàn)我們想要的功能。

1. 石油測井儀器

0x01

背景知識

在我的職業(yè)生涯中,有5年多的時間在作石油儀器。這是一個很傳統(tǒng)的行業(yè),但也是非常綜合性和吃技術的行業(yè)。

有人說:“你這一章似乎要講的是CPU的利用率問題,怎么又講起石油儀器來了?”別急,振南自有用意。

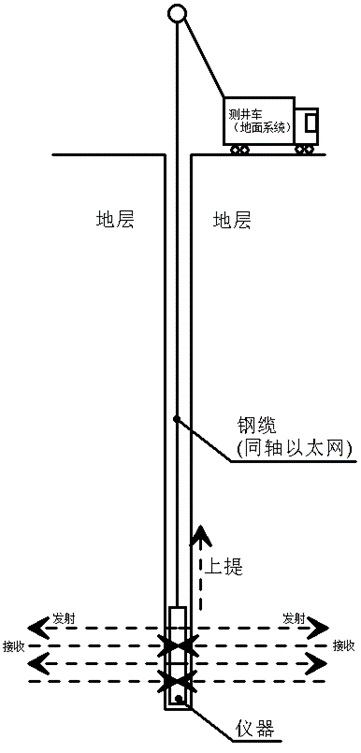

上圖所示為石油測井系統(tǒng)的簡易拓撲示意圖。工作時測井車通過輪盤拉動鋼纜上提,與此同時儀器向外發(fā)射信號(電或超聲),并接收返回信號經(jīng)過計算將結(jié)果通過同軸以太網(wǎng)上傳到地面系統(tǒng),由上位機繪制出曲線。最終曲線將交給解釋工程師,來判斷油氣儲層的位置。

上提的速度是一定的,我們當然希望在某一個深度上多采集一些數(shù)據(jù),即盡量提高采樣率。這樣最終的測井曲線上就能體現(xiàn)出更多的細節(jié)。

OK,這就是最基本的原理和背景。

0x02

測井數(shù)據(jù)采傳的實現(xiàn)

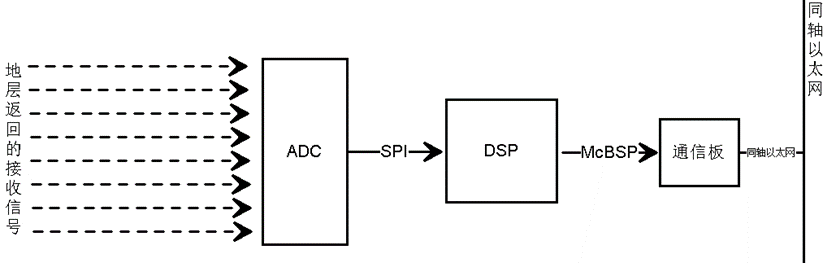

電路上比較清晰,下圖為測井儀器數(shù)據(jù)采傳原理框圖:

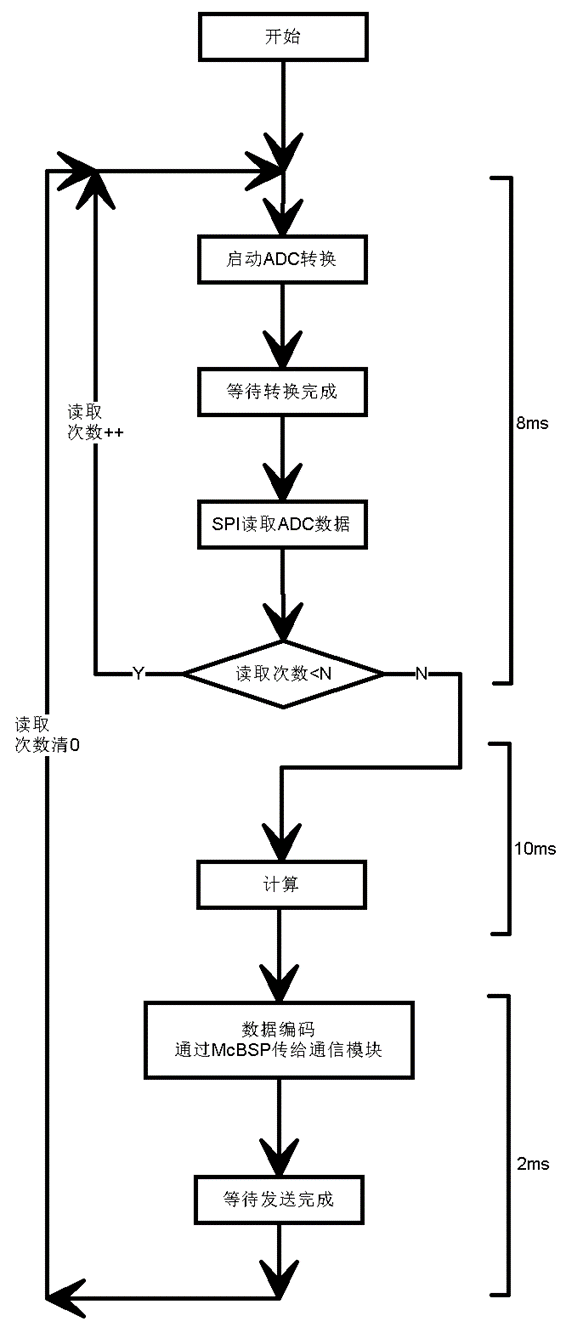

最直接的初級方案

最直接的方案是所有人都能想到的方案,就是采集、計算、發(fā)送按部就班的進行,如下圖所示。

每一個周期要作的事情就是:ADC采集一段波形,然后進行計算,主要是一些數(shù)字濾波、FFT、DPSD之類的數(shù)字信號處理,最終將結(jié)果數(shù)據(jù)按協(xié)議格式打包通過McBSP(TI DSP專有的通信接口)發(fā)送給同軸以太網(wǎng)通信模塊。我們當然希望這個周期越短越好,這需要將一些步驟優(yōu)化壓縮。

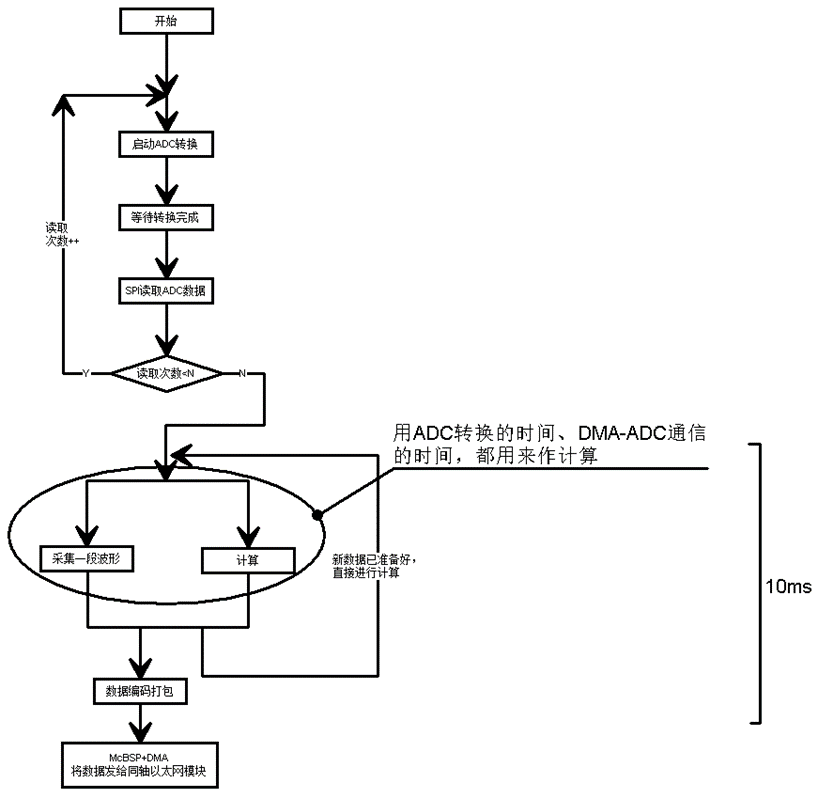

加入DMA的優(yōu)化方案

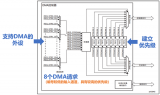

上面的方案,仔細看一下就會發(fā)現(xiàn),它的所有操作都是需要CPU參與的,大量的時間都在等待外設。如何降低CPU的參與度,把其寶貴的時間不要浪費在空等上,而放在核心算法的計算上,如下圖所示:

我們首先由CPU參與完成一次波形采集,然后開始針對采集數(shù)據(jù)進行計算,因為涉及大量浮點數(shù)據(jù)的數(shù)字信號處理,所以計算過程會比較花時間,一次計算大約需要花費10ms。與此同時,我們適時的不斷啟動ADC轉(zhuǎn)換,在其轉(zhuǎn)換的時間間隙里進行計算,然后直接啟動SPI-DMA傳輸來讀取ADC的轉(zhuǎn)換數(shù)據(jù),而CPU不用去等DMA傳輸完成,可以利用DMA傳輸?shù)臅r間進行計算,最后回過頭來立即進行下一次計算,因為此時新的波形已經(jīng)準備好了。這樣,一個周期的時間可以壓縮到10ms,采樣率比原來提高了一倍。

振南是想通過這個實例來告訴大家:CPU的運行時間是寶貴的,將片上的硬件資源充分的利用起來將可以釋放出更多的CPU時間來作更有意義的事情。一些技巧和DMA的合理運用是行之有效的辦法。

其實很多時候能被用來發(fā)揮的硬件資源并不只限于片內(nèi),我們自己設計一些簡單的片外電路加以輔助,有時候可以達到意想不到的效果,請往下看。

2. 巧驅(qū)攝像頭

0x01

攝像頭時序分析

我知道很多人都對攝像頭模塊感興趣,想用單片機驅(qū)動一下試試效果,但是作成功的并不多,下圖為比較盛行的OV7670攝像頭模塊和模組:

究其原因有幾點:1、攝像頭CMOS芯片的時序較為復雜;2、SCCB通信及相關寄存器的配置;3、時序過快,而且是按其固有頻率主動輸出,難于捕捉和采集數(shù)據(jù)。

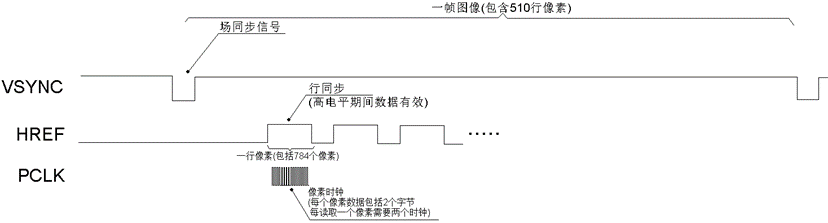

它的時序有多快,我們來看下圖所示的OV7670的時序圖:

OV7670在VGA模式下可達到的最高幀率30fps,即每秒鐘產(chǎn)生30幀640X480尺寸的圖像。從官方資料上得知VGA模式下實際輸出的行數(shù)為510,每行輸出的像素數(shù)為784(多出來的行數(shù)與像素數(shù)是多余的,其數(shù)據(jù)是無效的,我們只關注HREF為高電平期間的像素數(shù)據(jù))。這樣,PCLK的時鐘周期為1/(30510784*2)=41.7ns。想要用一般單片機的GPIO來直接采集像素數(shù)據(jù),幾乎是不可能的,因為IO與CPU的速度都不夠快。

0x02

使用DCMI+DMA

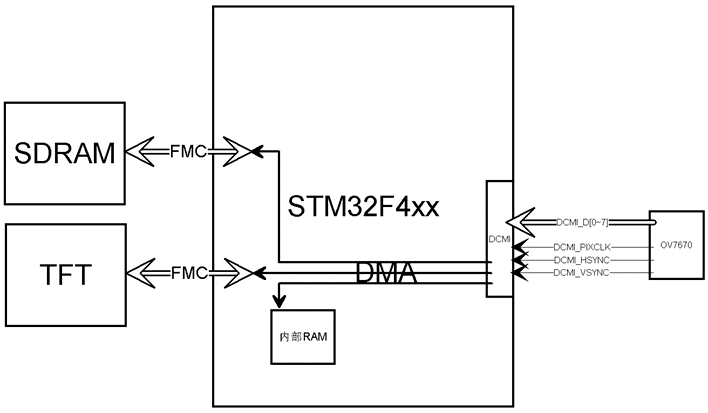

要讀取攝像頭如此高速的數(shù)據(jù),必須要有專門的硬件。我們可以選用ST的STM32F4系列單片機,它內(nèi)置了DCMI(數(shù)字攝像頭模塊接口),使用它將可以很輕松的完成圖像獲取的功能。它要配合DMA來工作,如下圖示:

DCMI獲取攝像頭數(shù)據(jù),可以通過DMA直接將數(shù)據(jù)保存到內(nèi)部RAM或外部的SDRAM,甚至直接寫入到TFT中,實現(xiàn)圖像的實時動態(tài)顯示。而在整個過程中,CPU只不過在作一些配置性的工作,并沒有參與圖像數(shù)據(jù)采集和傳輸。所以,用高端芯片會使我們的開發(fā)工作如虎添翼,事半功倍。就是因為它有更強大的硬件外設來為我們完成特定的功能實現(xiàn)。當然,更強大的硬件也意味著更多的學習成本,我們需要仔細學習如何正確的使用它來達到想要的效果。

有些時候,硬件外設電路甚至比CPU內(nèi)核更復雜,比如有些多媒體編解碼SOC,CPU內(nèi)核只是51或M0,片上更大的面積是諸如H.264之類的編解碼電路。所以,作嵌入式開發(fā)的工程師,首先要充分了解自己手上有哪些硬件資源,而不要所有功能都純依靠CPU來實現(xiàn)。

0x03

自搭外部電路

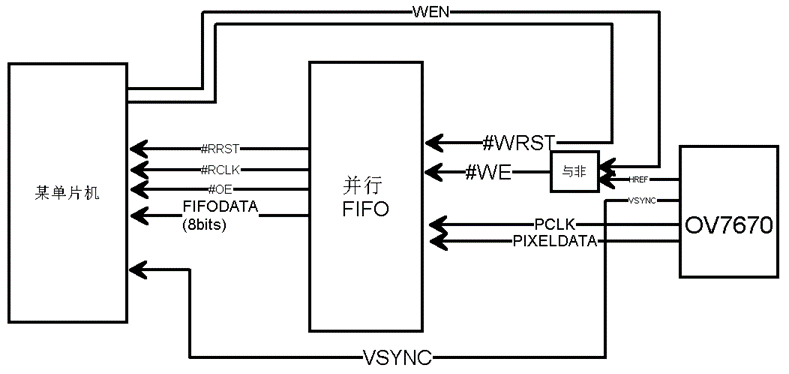

本節(jié)的名字是“巧驅(qū)攝像頭”,上面所介紹的方案都不算不上一個“巧”字。上述方案中必須要求單片機有DCMI之類的專用硬件,那不用DCMI可不可以?比如拿普通的51或低端的M0單片機,可不可以實現(xiàn)對攝像頭的驅(qū)動。答案是肯定的,不過這需要我們在外部電路上作些手腳,如下圖所示為通過片外并行FIFO+時序調(diào)理實現(xiàn)圖像采集:

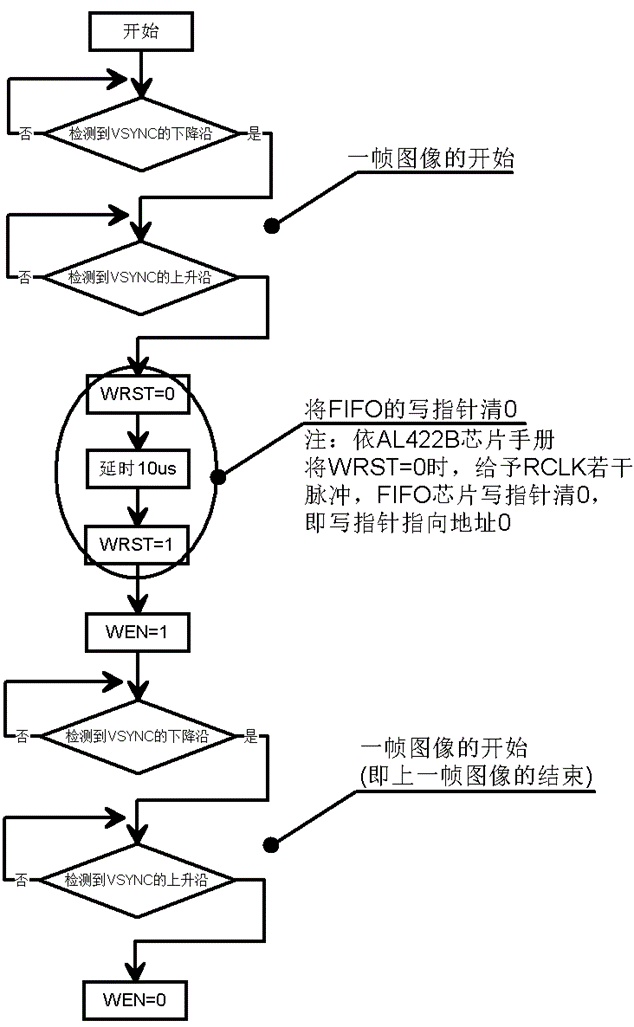

配合下面的流程圖,大家就知道其巧妙之處了,如下圖所示為通過片外并行FIFO實現(xiàn)一幀數(shù)據(jù)的獲取:

程序按上圖描述的邏輯運行之后,一幀圖像就存到FIFO中了。此時單片機可以慢慢從讀取端(并行FIFO分為寫入端與讀取端,分別對應的有寫指針與讀指針)讀到圖像數(shù)據(jù)了。這樣CPU和IO的速度就再也不是瓶頸。通過這樣的機制,任何單片機都可以輕松實現(xiàn)圖像采集了。

在此過程中,CPU都干了什么?似乎只有等待幀同步信號VSYNC和操作幾個IO。這種方式比DCMI+DMA更省CPU(DMA實際上會占用一半的片內(nèi)數(shù)據(jù)總線帶寬,使CPU的運行效率降低),而且更靈活,對單片機硬件的依賴更小。

3. 單片機巧驅(qū)7寸大液晶屏

通過上面幾個實例,大家應該知道振南所謂“巧驅(qū)”的路數(shù)了吧,對,就是多讓硬件說話,我們要作“軟硬兼施”的工程師。

OK,如果我問大家:“我能用51或M0單片機,驅(qū)動7寸大屏液晶(800*480),如圖6.10,并且流暢播放視頻,你信不信?”你一定會說:“不太可能吧,刷屏速率不夠。”但我既然這么問,那振南一定是已經(jīng)實現(xiàn)了,這里我就把實現(xiàn)過程給大家講一下。

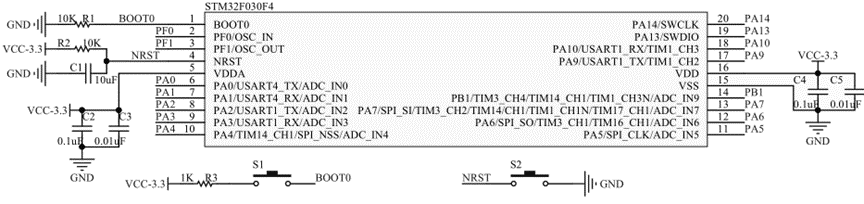

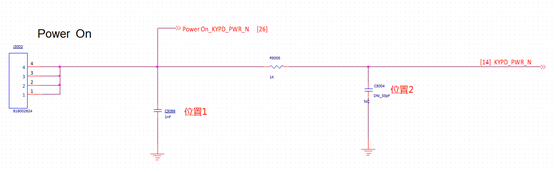

先來看原理圖,下圖為巧驅(qū)7寸液晶屏原理圖之MCU部分:

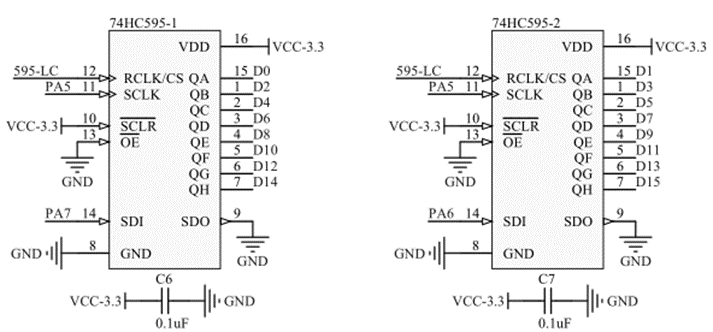

下圖為巧驅(qū)7寸液晶屏原理圖之74HC595串轉(zhuǎn)并部分:

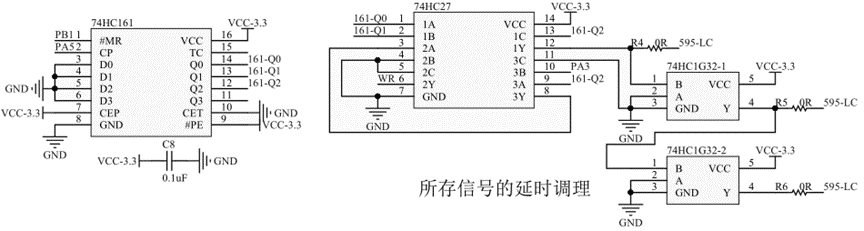

下圖為巧驅(qū)7寸液晶屏原理圖之八8進制計數(shù)與時序調(diào)理部分:

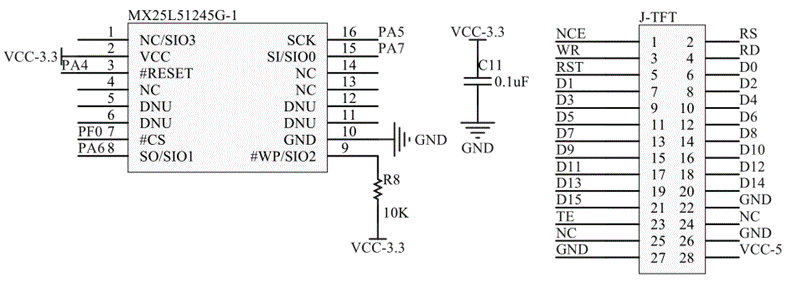

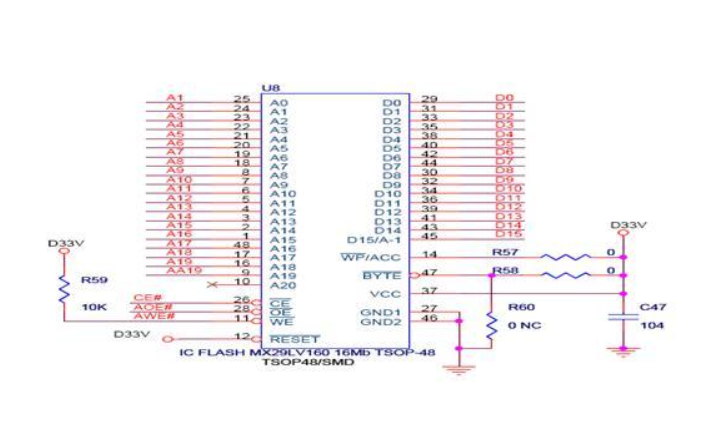

下圖為巧驅(qū)7寸液晶屏原理圖之spiFlash與7寸TFT接口部分:

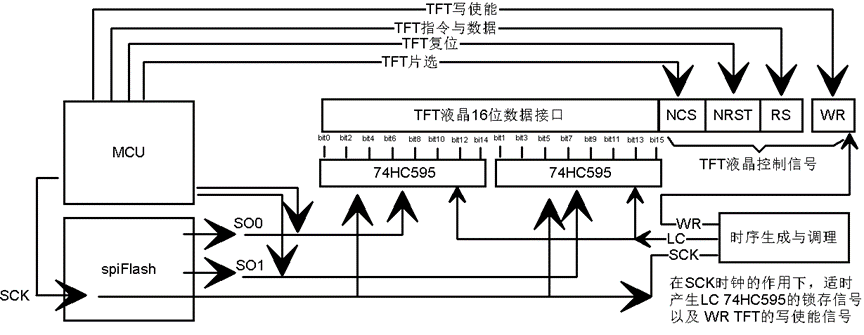

基本的實現(xiàn)邏輯如圖6.15所示。

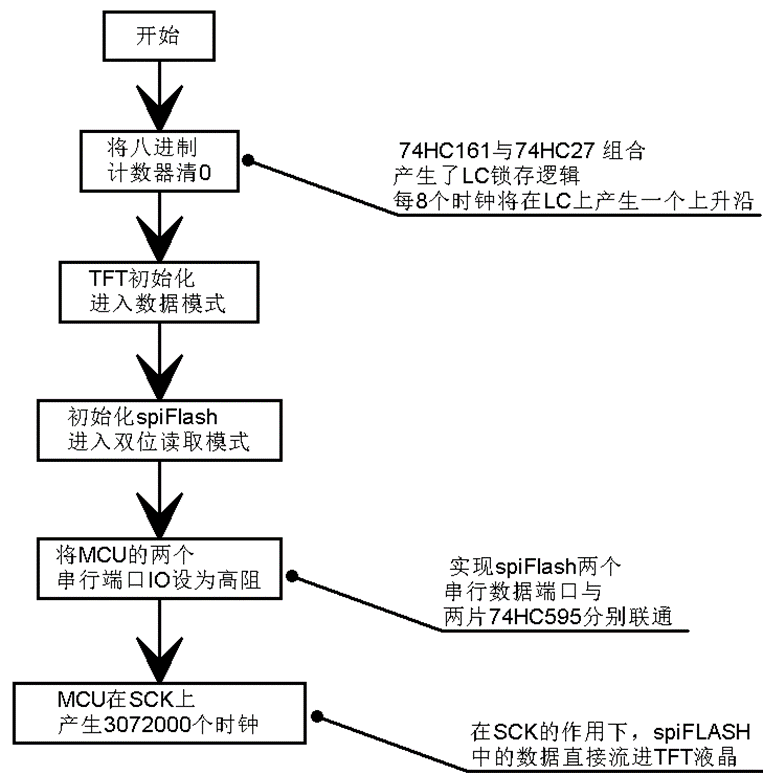

仔細觀察上面的原理圖與邏輯框圖,估計很多人已經(jīng)明白了振南的意思,振南再給出配套的流程圖,邏輯就更清晰了,如下圖所示:

兩片74HC595用于將16位串行數(shù)據(jù)轉(zhuǎn)換為并行,與TFT液晶的16位數(shù)據(jù)接口相連。74HC595的串行數(shù)據(jù)輸入同時與MCU的兩個GPIO以及spiFlash的兩個串行數(shù)據(jù)端口相連。當spiFlash失能時(即CS置高),其數(shù)據(jù)端口呈現(xiàn)高阻,此時74HC595可由MCU操作;而當MCU的GPIO設置為高阻時,兩片74HC595可分別接收來自spiFlash的雙位串行數(shù)據(jù)。這樣的復用設計,可以使MCU對TFT液晶進行預先的初始化,使其工作在純像素數(shù)據(jù)寫入的模式;而在高速數(shù)據(jù)寫入的階段,MCU退出而讓TFT接收來自spiFlash的數(shù)據(jù)。

兩片74HC595實現(xiàn)串轉(zhuǎn)并的要點在于LC鎖存信號的產(chǎn)生,每產(chǎn)生8個SCK脈沖,則自動產(chǎn)生一個LC上上升沿,這是時序生成與理調(diào)邏輯的一部分。實現(xiàn)的根本在于74HC161與74HC27的組合運用,如圖6.13。首先對74HC161復位清零,此時[Q2:Q0]=000,74HC27是三輸入或非門,其輸出1Y,即595-LC為1;時鐘的輸入后[Q2:Q0]隨之自增001、010 …… 在000之前595-LC均為0,而8個時鐘之后,595-LC將變?yōu)?,即產(chǎn)生了上升沿。這里振南給595-LC增加了兩級74HC1G32作為緩沖,為的是增加一些延時,以使74HC595的存鎖數(shù)據(jù)輸出更穩(wěn)定。

然后是液晶的WR信號的產(chǎn)生:從圖6.12中可以看到,WR信號是一個GPIO與八位計數(shù)器輸出最高位Q2的或非非(沒錯,是或非非)。當Q2為0時,WR受控于GPIO,此時可用于MCU對TFT預先進行初始化操作。當GPIO為0時,WR受控于Q2,每8個時鐘會產(chǎn)生一個下降沿(前面那個或非非是為了推遲一下這個下降沿,以使16位并行數(shù)據(jù)寫入液晶更穩(wěn)定),并維持4個時鐘周期。

基本的要點已經(jīng)描述清楚了。至于時鐘的產(chǎn)生,唯一的要求是要產(chǎn)生特定數(shù)量的時鐘,而不能是連續(xù)不斷的。比如一幀圖像的數(shù)據(jù)量為800*480半字,我們要輸出3072000個時鐘才能讓一幀圖像顯示到液晶上。所以我們不能用MCO或者是PWM,而要用SPI,如果是8位SPI,要寫384000次,如果是16位SPI,則要寫192000次。當然,為了節(jié)省更多的CPU資源,我們可以使用DMA。當時鐘不斷的產(chǎn)生,一幀幀的圖像顯示到液晶上時,視頻就流暢的播放出來了。

我曾經(jīng)把我這個“巧驅(qū)大屏”的實驗講給了我的同事聽,他們在贊嘆的同時,還說:“你不作FPGA真是浪費了!”其實我是作過一段時間的FPGA的,那還是在2007年在Intel中國研究院實習工作的時候。

好了,本章用3個實例闡述了本章最開頭的那句話:CPU時間是寶貴的,我們要把有限的CPU時間投入到更有意義的事情中去。

實際開發(fā)中,充分地利用硬件資源,自行靈活擴展一些硬件電路,通常可以達到意想不到的效果,甚至可以化不可能為可能。

永遠記住:我們很多時候作的是嵌入式軟件的工作,但歸根結(jié)底我們搞的還是硬件。

審核編輯:湯梓紅

-

嵌入式

+關注

關注

5092文章

19177瀏覽量

307682 -

寄存器

+關注

關注

31文章

5363瀏覽量

121167 -

cpu

+關注

關注

68文章

10904瀏覽量

213020 -

接口

+關注

關注

33文章

8691瀏覽量

151919 -

SPI

+關注

關注

17文章

1722瀏覽量

92128

原文標題:CPU,你省省心吧!

文章出處:【微信號:嵌入式攻城獅,微信公眾號:嵌入式攻城獅】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

介紹幾個是常用的DMA傳輸路徑

人工智能設備減輕影像科醫(yī)生的工作負擔

釋放改革紅利,減輕用戶電費負擔

可穿戴式機器人助力救災活動,減輕了人體腰部40%的負擔

PMU如何通過執(zhí)行任務減輕主CPU的負荷

如何進行CPU內(nèi)部Flash讀寫的實例資料說明

減輕家務負擔,手持吸塵器哪個牌子好

巴士駕駛員輔助系統(tǒng)減輕工作負擔

集成電路設計助于減輕電源設計人員的負擔

利用無線電源減輕戰(zhàn)場電池負擔

請問DMA控制器可以減輕CPU負擔嗎?

通過幾個實例說明如何減輕CPU負擔

通過幾個實例說明如何減輕CPU負擔

評論