信號完整性分析越來越重要

芯片和電子產品一直都在向小型化、高度集成化以及高速化的方向發展,可產品的研發周期卻越來越緊迫。這對工程師們來說是一個巨大的考驗。

無論是數據中心的產品、還是汽車和工業設備,甚至是我們日常使用的消費電子產品,它們的信號速率都在迅猛攀升!

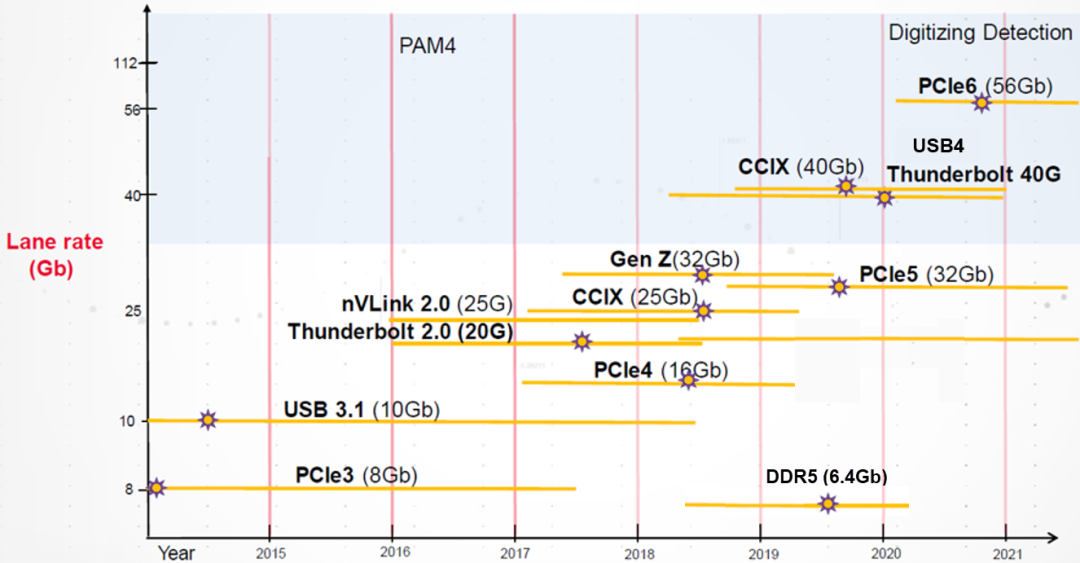

看看下面這張圖,PCIe6.0的速率已經達到了56Gbps,USB4達到了40Gbps,并行總線DDR5也達到了驚人的6.4Gbps,同時,高速總線的調制模式也從以往的NRZ發展到了PAM4甚至更高階的調制技術。

還有一些新型總線的出現,比如CCIX, GenZ,CXL等等。這些變化給工程師們帶來了前所未有的挑戰,也使得信號完整性分析變得比以往更加重要。

信號完整性是信號傳輸的一個綜合指標,它涵蓋了發送端、接收端以及傳輸路徑中的PCB、連接器、線纜或其他無源器件對信號的影響。各種總線協議都對這些部分有相應的定義,例如PCIe總線。

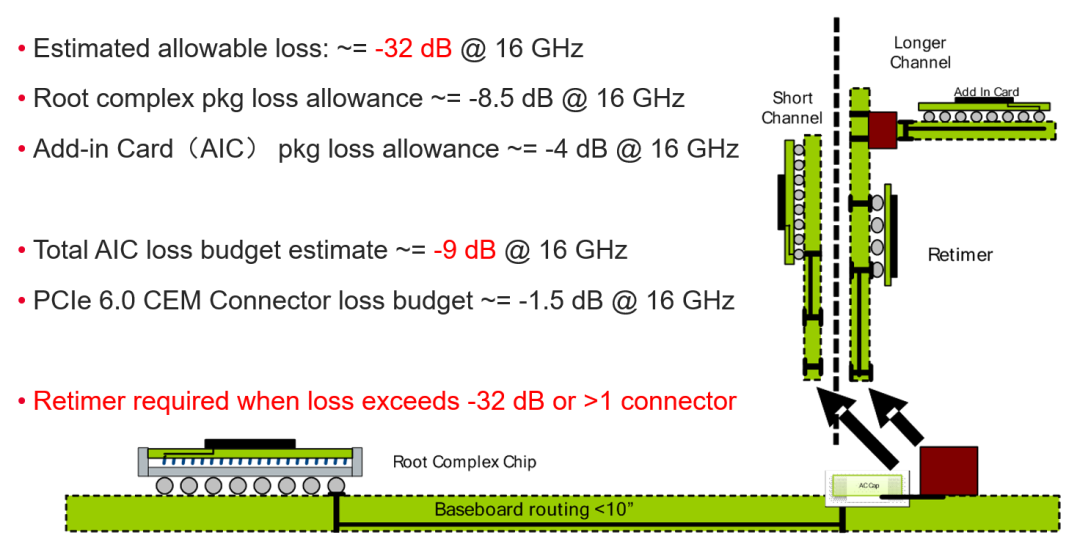

下圖展示了PCIe6.0規范中對各個部分插入損耗的定義。無論是進行仿真還是測試,都需要確保滿足這一標準。

PCIe6.0 InsertionLoss

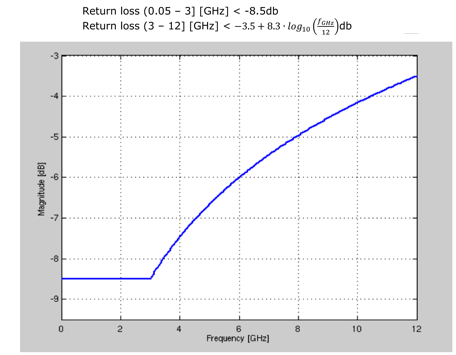

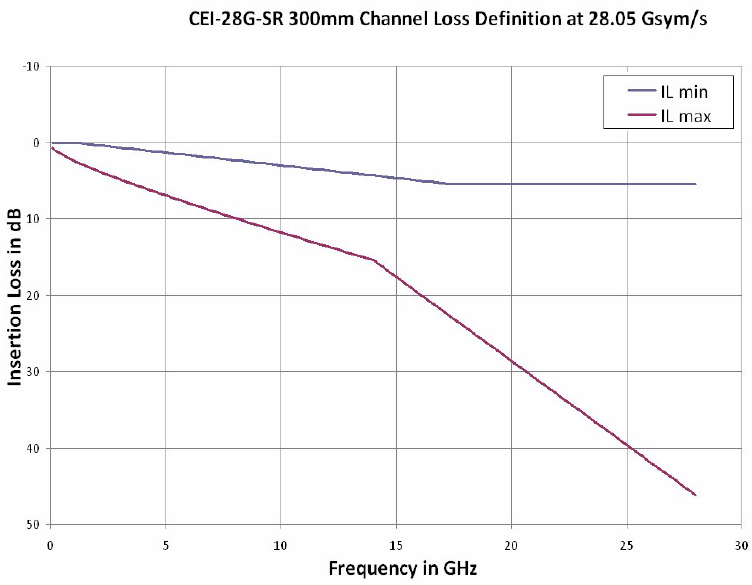

下面這張圖展示了在USB4和Thunderbolt3.0規范中定義的傳輸通道的回波損耗。同樣地,在OIF規范中,我們也可以找到插入損耗、回波損耗等等的明確定義。這些標準為我們的工程師在設計過程中提供了寶貴的參考依據。

Thunderbolt3.0 and USB4 Return Loss

CEI-28G-SR Channel Insertion Loss

一般來說,當我們分析信號完整性時,我們會關注眼圖、時序、阻抗、插入損耗、回波損耗、串擾等等因素。但隨著信號速率的不斷提高和傳輸方式的多樣化,信號完整性分析的指標也變得更加多樣化。在原來的基礎上我們還需要考慮ICN、ICR、COM、ILD、BER等等指標。這無疑給信號完整性工程師增加了很大的工作量。

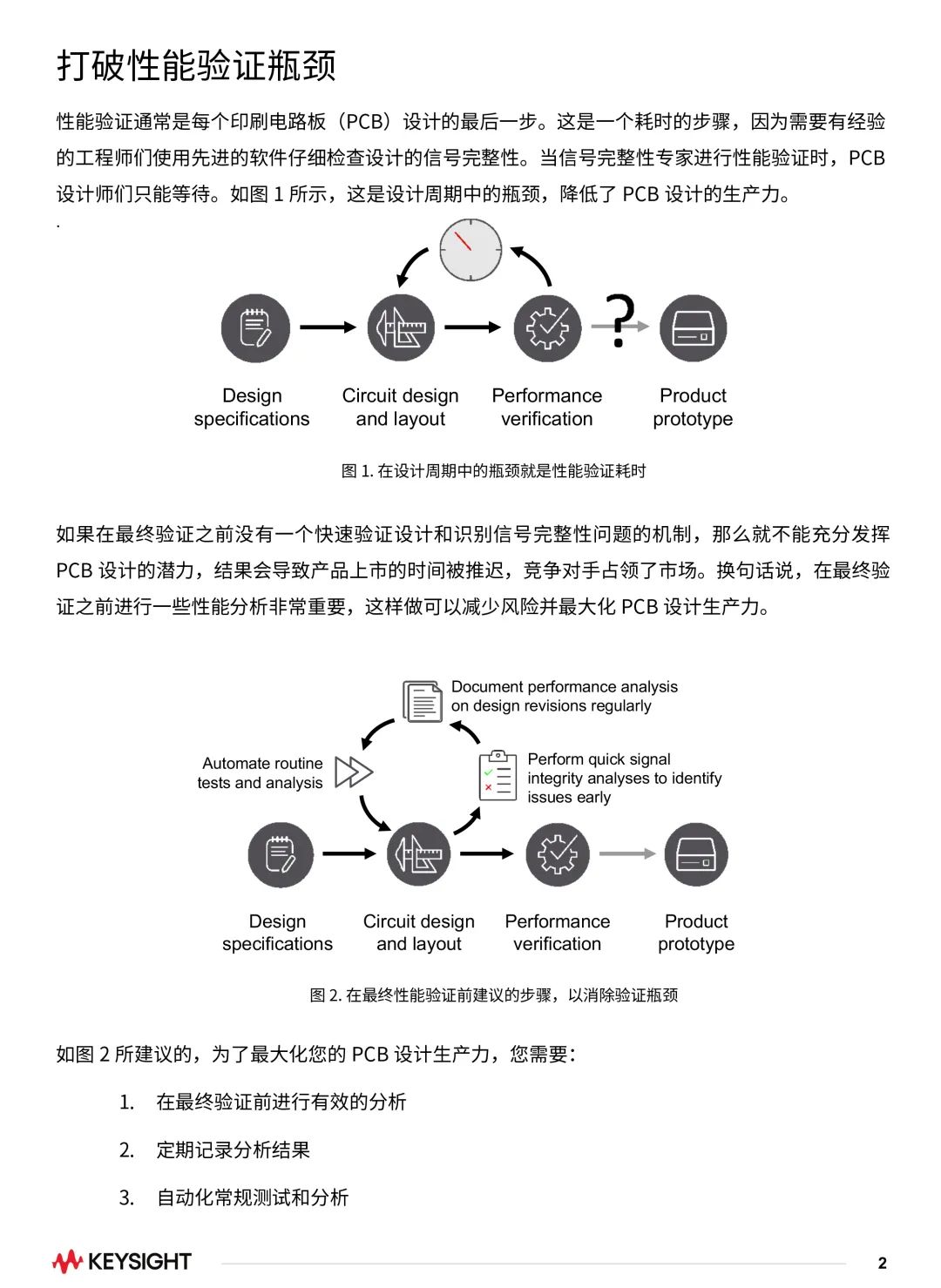

在高速數字電路設計中,硬件工程師通常會將設計交給信號完整性工程師進行分析,他們通過詳盡復雜的分析來發現潛在問題和隱患。盡管現如今的信號完整性分析工具功能強大且高效,能夠節省大量時間,但整個信號完整性仿真過程仍然是相當耗時的。

此外,信號完整性工程師在公司中的數量通常比硬件工程師少得多,這導致信號完整性分析成為整個設計流程的一個瓶頸。

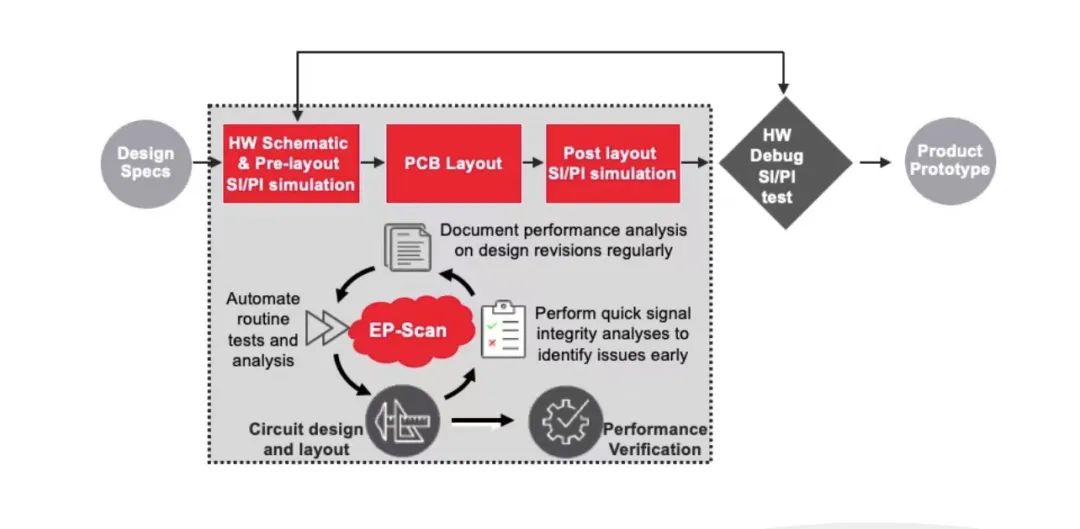

為了突破性能驗證的瓶頸,是德科技在今年初推出了EP-Scan(Electrical Performance Scan)電氣性能掃描軟件,它為我們提供了一種快速檢測電氣性能的方法,讓硬件工程師們能夠及時發現初級的SI問題,避免后期可能出現的麻煩。有了它,硬件工程師只需簡單的操作,就能進行快速掃描,查看信號的電氣特性,找出潛在的信號完整性問題。

當然,對于更復雜的信號完整性分析,依然需要SI工程師們的專業知識和技能,通過深入的分析和仿真來解決。

接下來,讓我們一起來了解如何通過簡單的三個步驟解決信號完整性分析中的瓶頸問題。

第一步,加載設計和設置。

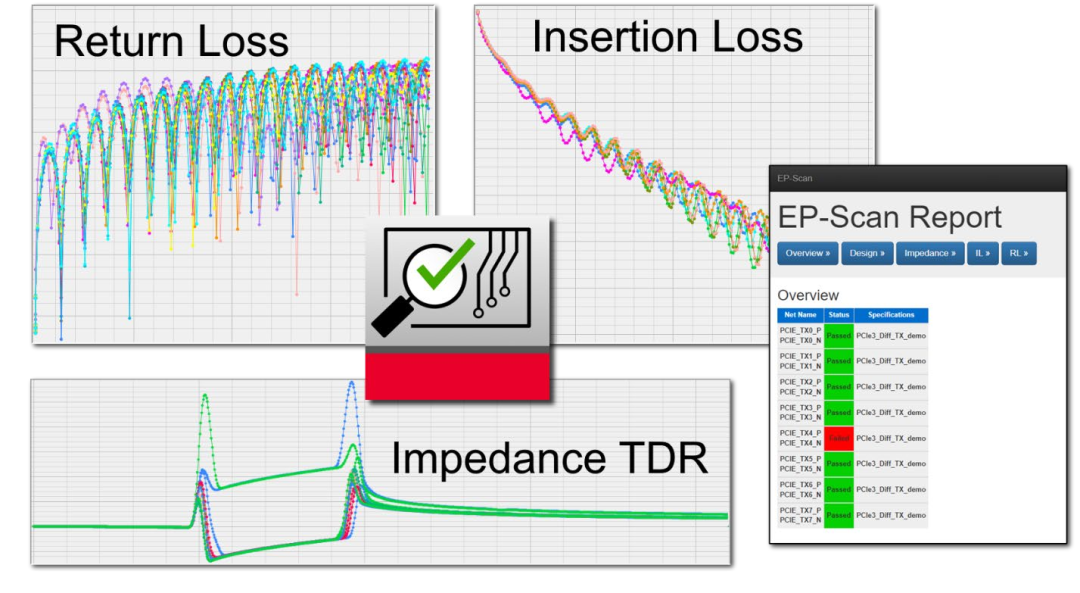

使用EP-Scan,我們可以輕松加載PCB Layout設計或導入ODB++文件。然后,我們選擇特定的網絡進行分析,更棒的是,我們還能為這個網絡設定測試計劃,并選擇相應的電器規范(EP-Scan內置了一些電器規范,如PCIE、USB、DDR等),然后根據相應的電氣規范對阻抗、延時、插入損耗和回波損耗等指標進行分析。

第二步,進行電氣性能掃描。

這個步驟非常簡單,只需輕輕按下一個按鈕,就能一鍵運行所有的測試計劃。此外,每當我們對設計進行修改時,我們可以再去自動運行EP-Scan里面事先設定好測試計劃,以便輕松檢查信號完整性問題。這樣,我們可以在修改后立即獲得反饋,確保設計的穩定性和可靠性。

第三步,生成報告和存檔。

在完成信號完整性分析后,EP-Scan可以一鍵生成詳細的報告。這個功能極大地簡化了結果的展示和存檔過程,避免了繁瑣的復制粘貼工作。我們可以輕松地分享分析結果給團隊成員或管理層,并記錄下設計的進展和改進。這樣,我們能夠保持透明的溝通和高效的工作流程。

通過這三個簡單的步驟,EP-Scan為硬件工程師提供了方便、高效的工具,簡化了分析流程,節約時間和精力。它突破了性能驗證瓶頸,讓您專注于設計的優化和改進,更快地將產品推向市場。

EP-Scan生成的測試報告

點擊查看

關于是德科技

是德科技(NYSE:KEYS)啟迪并賦能創新者,助力他們將改變世界的技術帶入生活。作為一家標準普爾 500 指數公司,我們提供先進的設計、仿真和測試解決方案,旨在幫助工程師在整個產品生命周期中更快地完成開發和部署,同時控制好風險。我們的客戶遍及全球通信、工業自動化、航空航天與國防、汽車、半導體和通用電子等市場。我們與客戶攜手,加速創新,創造一個安全互聯的世界。

-

工程師

+關注

關注

59文章

1572瀏覽量

68655 -

PCB設計

+關注

關注

394文章

4701瀏覽量

86360 -

總線

+關注

關注

10文章

2903瀏覽量

88402 -

信號完整性

+關注

關注

68文章

1417瀏覽量

95639 -

PCIe

+關注

關注

15文章

1262瀏覽量

83200 -

是德科技

+關注

關注

20文章

894瀏覽量

82030

原文標題:突破信號完整性分析瓶頸:3步輕松駕馭PCB設計

文章出處:【微信號:是德科技KEYSIGHT,微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

突破信號完整性分析瓶頸:3步輕松駕馭PCB設計 三個步驟解決信號完整性分析的瓶頸問題

突破信號完整性分析瓶頸:3步輕松駕馭PCB設計 三個步驟解決信號完整性分析的瓶頸問題

評論