什么是三態(tài)電路

一般來說,我們認(rèn)為CMOS數(shù)字電路的輸出的穩(wěn)定狀態(tài)只有2種,就是邏輯0和邏輯1,從模擬信號量來說,就是0V和VDD。

那么有些小伙伴會說了,實(shí)際上輸出狀態(tài)還有Z態(tài)和X態(tài)。

Z態(tài)表示沒有驅(qū)動時信號的輸出,又被表示為高阻狀態(tài)High-Z,在仿真波形上,喜歡用一條處于中間位置的線條表示,有的工具用黃色線條,有些工具用紅色線條。

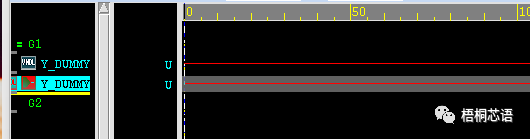

而X態(tài),則表示輸出狀態(tài)不是邏輯0,也不是邏輯1,在仿真波形上,往往用一種紅色塊表示。如下圖所示:

從仿真信號來看,這樣的描述是為了區(qū)分穩(wěn)定輸出的信號邏輯狀態(tài),但客觀世界里,并不存在X態(tài)以及Z態(tài)這兩種信號狀態(tài)。只是在不穩(wěn)定的情況下,由于外界不確定的驅(qū)動因素,會使得輸出狀態(tài)向邏輯0或邏輯1漂移。

一般來說如果想避免這種Z態(tài)或X態(tài),那么就必須確保信號有,且只有一個驅(qū)動源在驅(qū)動。(亞穩(wěn)態(tài)也是導(dǎo)致Z態(tài)或X態(tài)的一種原因,但在那個時候,其實(shí)就是存在多個驅(qū)動,或沒有驅(qū)動的情況)

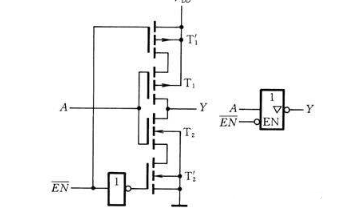

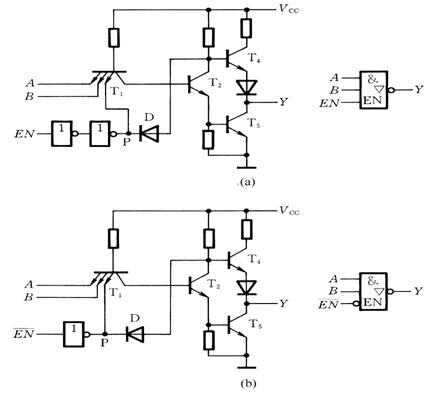

峰回路轉(zhuǎn),那么這里想說的三態(tài)電路,又是一個什么鬼呢?我們看下面這個電路結(jié)構(gòu)。

上圖所示,就是一種三態(tài)輸出電路,當(dāng)Enable為VDD的時候,輸出電壓Vout與A端輸入電壓保持一個邏輯電平轉(zhuǎn)換。但是當(dāng)Enable控制信號為0V,也就是邏輯0時,無論輸入電壓A端怎么變化,輸出反相器的PMOS和NMOS都處于關(guān)閉狀態(tài),Vout就沒有驅(qū)動了。

剛才我們說過,如果信號沒有驅(qū)動,就是輸出高阻態(tài)High-Z,那么Enable為邏輯0的時候,Vout就是High-Z。

這種可以輸出第三種邏輯狀態(tài)的電路,我們稱之為三態(tài)電路。在數(shù)字邏輯設(shè)計(jì)中,原則上只有IO電路上可以使用,常規(guī)的RTL設(shè)計(jì),是不允許使用的。

如何讓High-Z從不穩(wěn)定走向穩(wěn)定

既然High-Z是一種因?yàn)闆]有驅(qū)動而導(dǎo)致無法使用的不穩(wěn)定信號邏輯,那么又怎樣去使用呢?

因?yàn)槿龖B(tài)電路常被用于IO Buffer的電路中,因此一般來說,我們會在Vout輸出上加一個上拉電路或下拉電路。當(dāng)Enable無效時,Vout通過一個弱上拉或弱下拉連接到VDD或地上,使其穩(wěn)定到VDD或0V。

如下所示,是某工藝下數(shù)字邏輯IO Cell的電路示意圖,當(dāng)OEN為1'b1的時候,A端數(shù)據(jù)是無法送到P(即PAD)端的,但通過配置PUN為邏輯0的時候,則P端被拉到了VDD,即邏輯1上,確保了穩(wěn)定的輸出:

FPGA上如何使用三態(tài)電路作為IO

一般來說,ASIC設(shè)計(jì)時,有專門的IO Buffer可以實(shí)現(xiàn)三態(tài)IO電路,實(shí)例化在電路中即可。但FPGA沒有,可以使用以下Verilog HDL實(shí)現(xiàn):

注意這只適用于FPGA,同時要在IO約束文件里設(shè)置PULLUP或PULLDOWN可配置上拉或下拉。

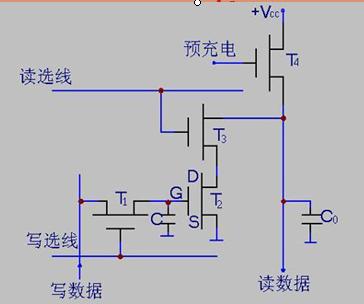

使用BUSKEEPER對三態(tài)輸出做保持

有些早期設(shè)計(jì)的片內(nèi)嵌入式存儲電路,其輸出口仍然會使用三態(tài)輸出,原本是為了降低功耗(還沒輸出時,關(guān)閉輸出驅(qū)動管),但這也導(dǎo)致輸出端出現(xiàn)High-Z,無法直接連接到數(shù)字邏輯上。

這個時候就可以在每個可能出現(xiàn)三態(tài)邏輯的輸出信號上,接一個叫做buskeeper的電路邏輯,有時候又叫busholder。

Buskeeper用了一對驅(qū)動力大體一致的反相器組成反饋,當(dāng)內(nèi)部關(guān)閉輸出后,原本在信號上的邏輯1或邏輯0,就可以被保持住。確保數(shù)字邏輯中不存在高阻或不定態(tài)。

注意驅(qū)動能力

無論上拉或下拉,我們都會說 弱上拉 ,或 弱下拉 ,這是什么原因呢?

我們看下面這個IO,當(dāng)輸出使能關(guān)閉后,DRVP以及DRVN都處于OFF狀態(tài),VDDPST通過上拉PMOS,PUMOS,為電容充電,使得PAD達(dá)到VDDPST的電壓值,也就是邏輯1。

如果打開輸出使能,并想輸出邏輯1,如下圖所示,因?yàn)轵?qū)動管DRVN關(guān)閉,因此VDDPST通過DRVP以及PUMOS同時向電容充電,時PAD達(dá)到邏輯1。這個還是比較好理解的。

但是如果我們想輸出邏輯0呢?由于上拉管PUMOS與驅(qū)動管DRVN同時打開,那么同時會有VDDPST通過PUMOS向電容充電,以及電容通過DRVN向地放電的兩條通路。如果想讓PAD達(dá)到邏輯0,那么必須是放電通路的能力遠(yuǎn)遠(yuǎn)大于充電通路。

由此可見,必須使用較大的上拉或下拉電阻,或者使用驅(qū)動能力較弱的上拉或下拉晶體管,才更可能使PAD在輸出邏輯0的時候,更容易接近于地電平。

所謂驅(qū)動力,其實(shí)就是電流,對于電阻來說,電流就是電壓與電阻的比值:

I=(VDDPST-VPAD)/R(I是驅(qū)動電流,VDDPST是IO的供電電壓,而VPAD是PAD上的電壓,理想結(jié)果是無限趨近于0V,R則是電阻的阻值)

由此可見,在假設(shè)VPAD無限接近于0,則希望電流越小(驅(qū)動力越小),則上拉或下拉電阻的阻值就需要越大。

而對于MOS來說,如果假設(shè)VPAD的電壓無限接近于VDDPST或0V,則上拉或下拉晶體管處于飽和狀態(tài),可以提供電流的公式為下圖中飽和區(qū)的計(jì)算方式:

根據(jù)公式可以看出,如果在一個特定工藝的芯片內(nèi),想減少電流,就是減小寬長比W/L的數(shù)值。

需要注意,因?yàn)镻MOS的遷移率只有NMOS大概一半的樣子,因此在設(shè)計(jì)電路時,下拉器件的選擇尤為重要。經(jīng)驗(yàn)不足的工程師,往往會在下拉驅(qū)動選擇上翻跟頭。

給大家一個問題思考,如果芯片內(nèi)的下拉驅(qū)動能力比較強(qiáng),后期芯片無法輸出穩(wěn)定的邏輯1,我們能不能通過板級設(shè)計(jì)解決這個問題呢?

電平適配電路

我們一般都認(rèn)為IO的輸出電壓就是芯片供電的Post-Drive電壓,如果驅(qū)動芯片A的Post-Drive電壓VDDPSTA是2.5V,則VOH為2.5V,但接收芯片B的Post-Drive電壓VDDPSTB是3.3V,VIL為2.7V。如何讓接收信號穩(wěn)定的接收到驅(qū)動邏輯電平呢?

這里可以巧用三態(tài)IO,當(dāng)CHIPA要輸出邏輯1的時候,不是通過驅(qū)動管輸出邏輯1,而是輸出一個High-Z狀態(tài),這個時候PAD上的信號就沒有驅(qū)動了。在片外增加一個上拉電阻,并連接到VDDPSTB上,則此時PAD上的電壓VPAD就會因?yàn)閂DDPSTB通過板級上拉電阻向電容充電而上升到VDDPSTB上,并穩(wěn)定為CHIPB提供邏輯1。

但也要注意一個問題,就是如果VDDPSTB比VDDPSTA高的太多,那么就要注意會不會因?yàn)閂DDPSTB到地的電壓過大,或者VDDPSTB到VDDPSTA的電壓差過大燒壞了DRVN或DRVP。

通過上拉電阻輸出邏輯1,或者通過下拉電阻輸出邏輯0的三態(tài)IO Buffer,在GPIO以及I2C等通訊接口上是經(jīng)常被用到的。具體電路,具體分析。

-

上拉電阻

+關(guān)注

關(guān)注

5文章

363瀏覽量

30734 -

VDD

+關(guān)注

關(guān)注

1文章

312瀏覽量

33551 -

三態(tài)電路

+關(guān)注

關(guān)注

0文章

4瀏覽量

5592 -

FPGA開發(fā)板

+關(guān)注

關(guān)注

10文章

123瀏覽量

31599 -

CMOS數(shù)字電路

+關(guān)注

關(guān)注

0文章

3瀏覽量

6170

發(fā)布評論請先 登錄

相關(guān)推薦

什么是三態(tài)門和OC門?

高阻態(tài)與三態(tài)門的電路原理分析

三態(tài)單片機(jī)IO的三態(tài)是指什么

三態(tài)電路在FPGA應(yīng)用設(shè)計(jì)中的分析

什么是三態(tài)門? 三態(tài)邏輯與非門電路以及三態(tài)門電路

三態(tài)門邏輯電路圖大全(三款三態(tài)門邏輯電路圖)

三態(tài)門有哪三態(tài)_三態(tài)門有什么特點(diǎn)

什么是三態(tài)電路?三態(tài)電路及其使用

什么是三態(tài)電路?三態(tài)電路及其使用

評論