編 者 按

關(guān)于仿真里的后門訪問,之前的文章《三分鐘教會(huì)你SpinalHDL仿真中的后門讀寫》中有做過介紹,其針對(duì)的都是針對(duì)以SpinalHDL中的代碼進(jìn)行的后門訪問。今天來看看當(dāng)封裝了Verilog BlackBox時(shí),在SpinalHDL仿真中如何進(jìn)行后門訪問Verilog代碼。

BlackBox代碼封裝

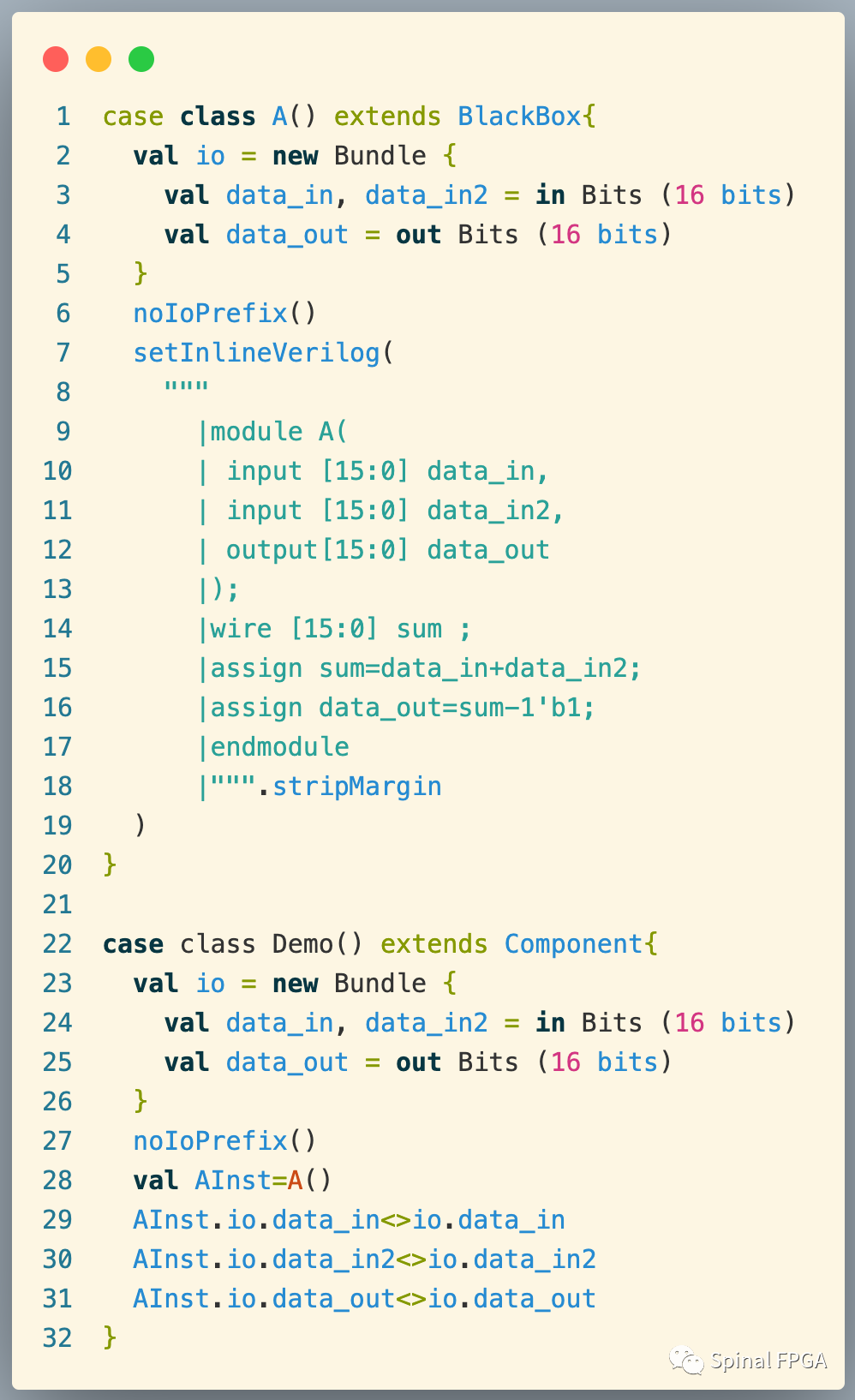

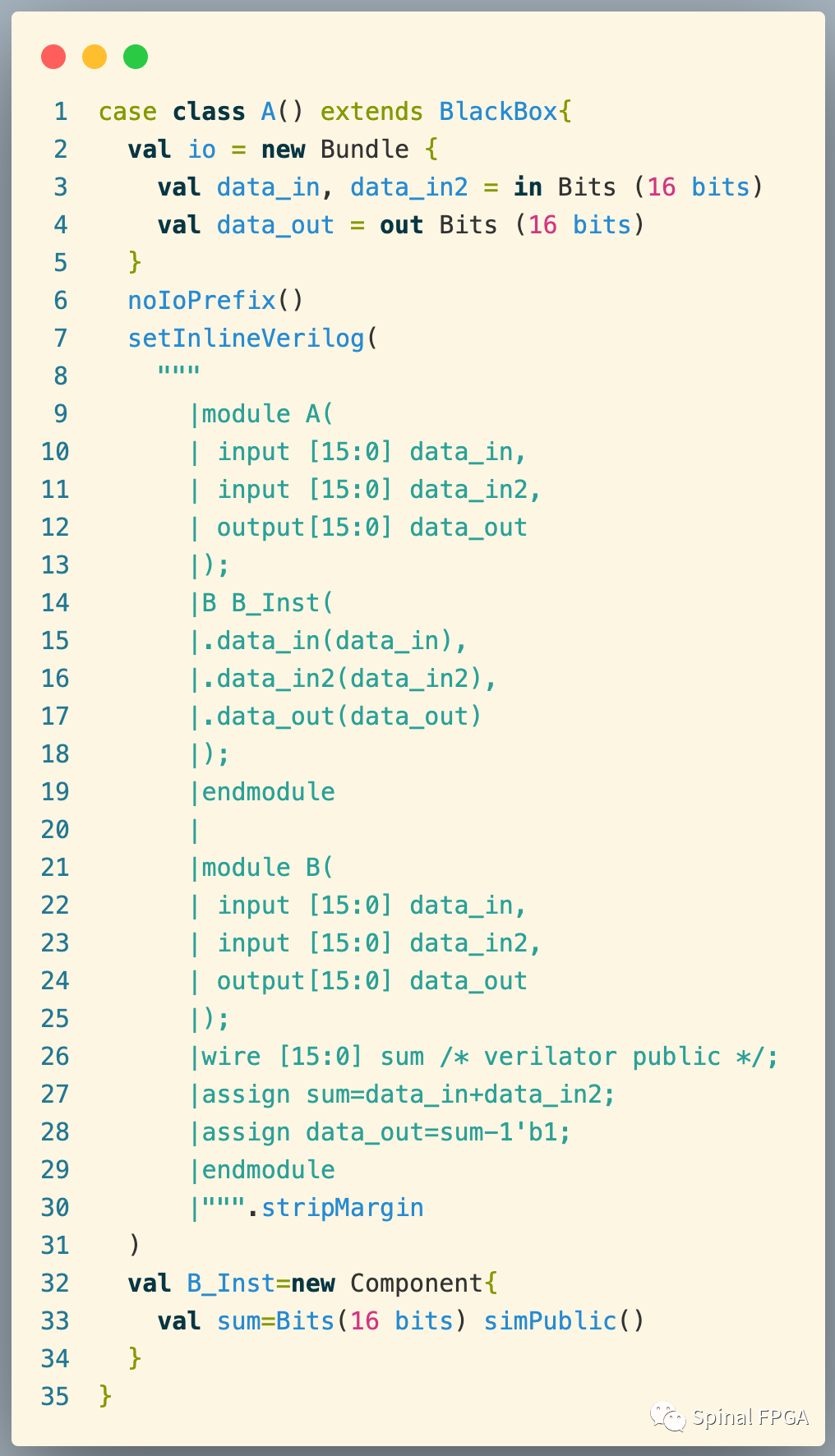

考慮下面的BlackBox代碼封裝:

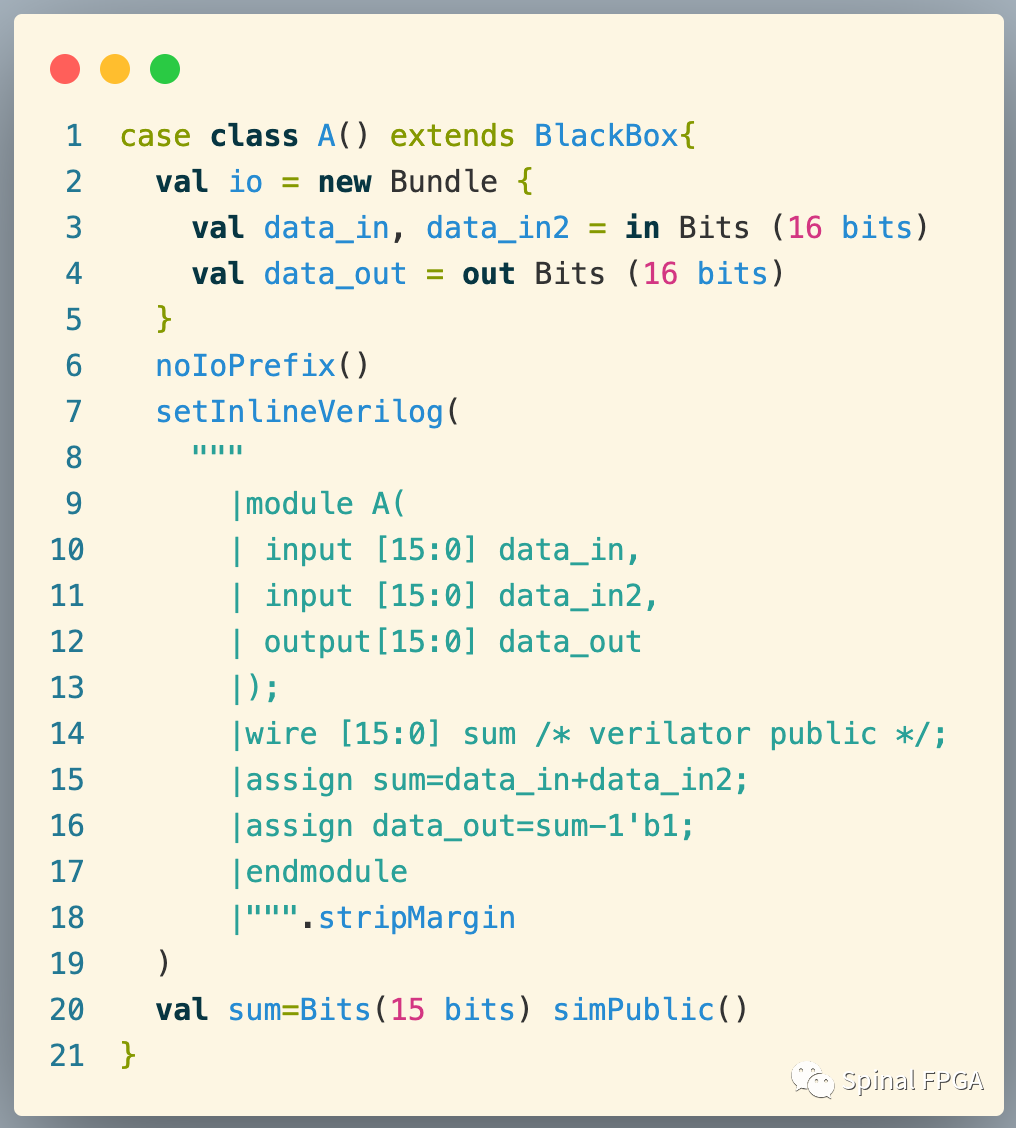

這里我們封裝了一個(gè)BlackBox A,在Demo中進(jìn)行例化。如果我們?cè)诜抡鏁r(shí)如果想要后門訪問模塊A中的sum,那么直接訪問肯定是不行的,這里就需要對(duì)BlackBox A稍進(jìn)行修改:

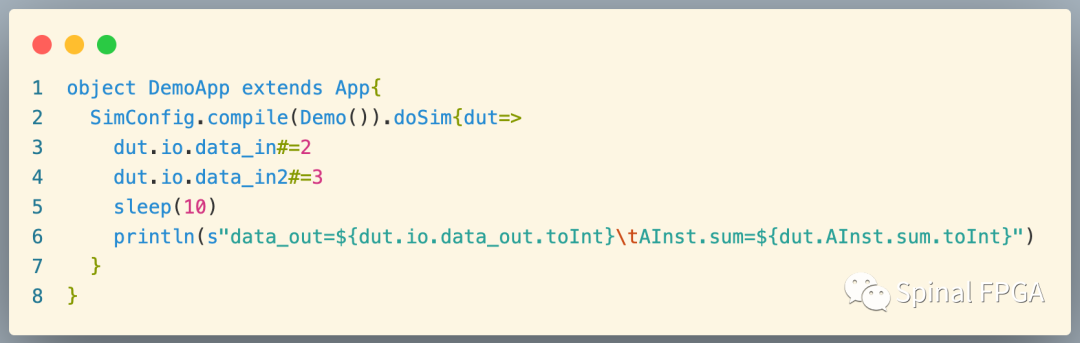

這里需要在A中例化一個(gè)sum變量并標(biāo)注為simPublic,同時(shí)在RTL代碼中就sum需添加/* verilator public */(注意是添加在分號(hào)前)。這樣我們可以在仿真中訪問A中的sum:

仿真中可以正常訪問A中的sum:

[Progress] Verilator compilation done in 4112.984 ms

[Progress] Start Demo test simulation with seed 129114326

data_out=4AInst.sum=5

多層blackbox

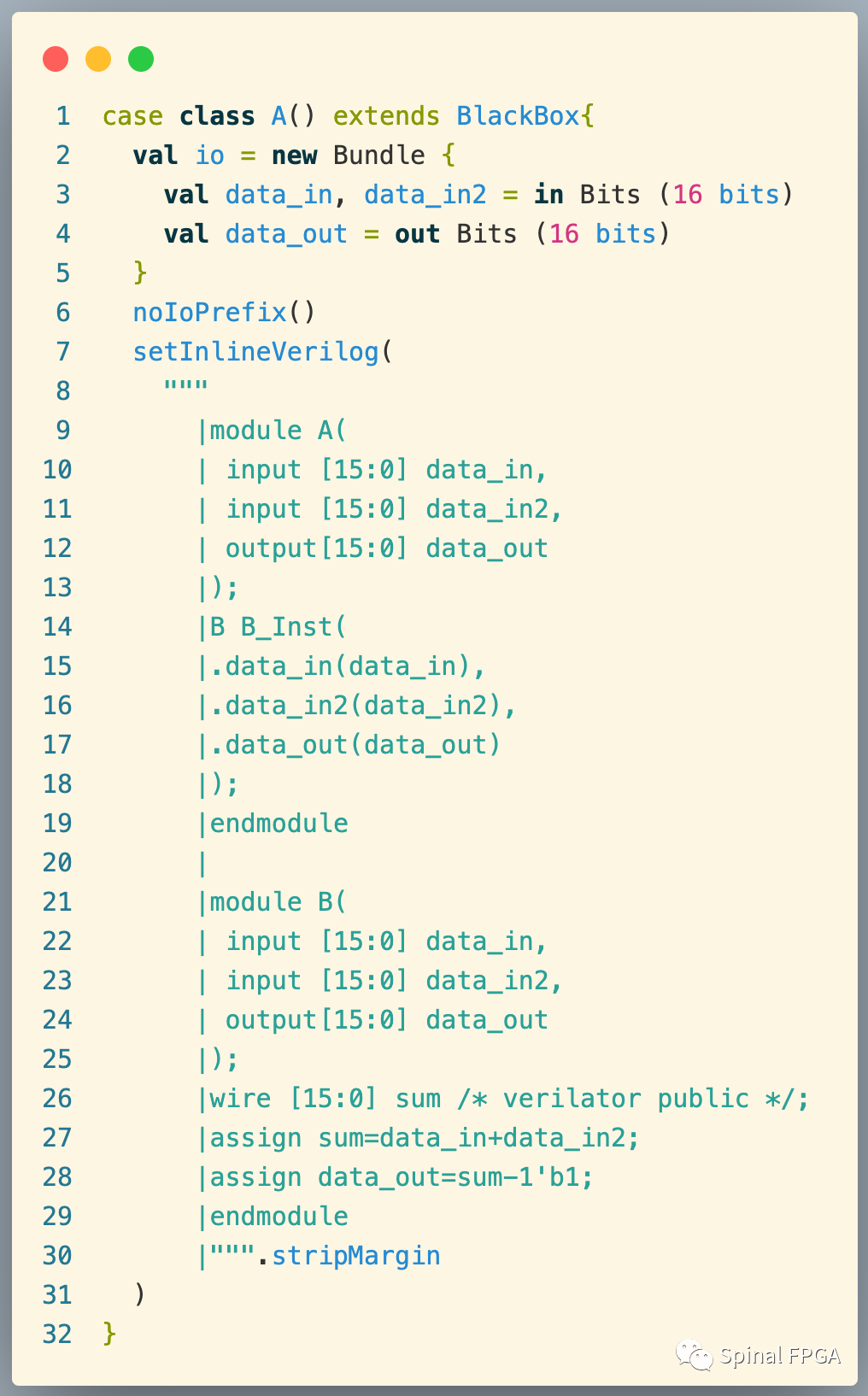

考慮下面的BlackBox:

在BlackBox A中其封裝的模塊A中有例化了模塊B,如果我們想要訪問模塊B中的sum,那么除了要在sum行添加/* verilator public */外還需要對(duì)BlackBox A添加待訪問sum的層次結(jié)構(gòu):

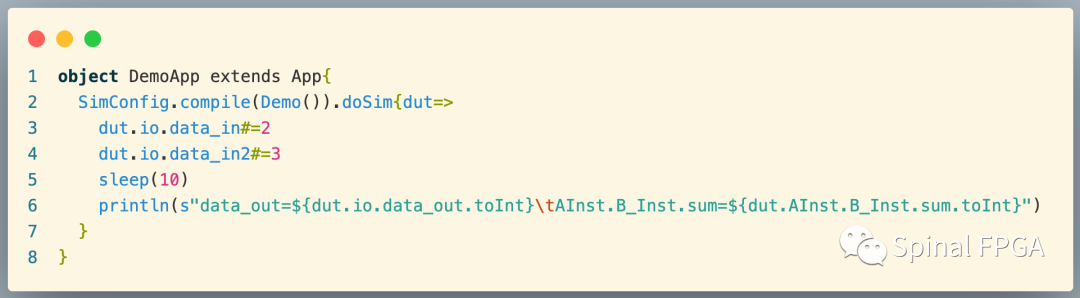

在仿真時(shí)可以訪問B_Inst中的sum變量:

[Progress] Start Demo test simulation with seed 574035638

data_out=4AInst.B_Inst.sum=5

[Done] Simulation done in 5.223 ms

寫在最后

這里的仿真均采用的是Verilator,關(guān)于VCS小伙伴們可以自行探索。

審核編輯:湯梓紅

-

封裝

+關(guān)注

關(guān)注

127文章

7992瀏覽量

143400 -

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133986 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110390 -

HDL

+關(guān)注

關(guān)注

8文章

328瀏覽量

47468 -

代碼

+關(guān)注

關(guān)注

30文章

4825瀏覽量

69041

原文標(biāo)題:Verilog代碼封裝后門訪問

文章出處:【微信號(hào):Spinal FPGA,微信公眾號(hào):Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Verilog代碼封裝后門訪問

Verilog代碼封裝后門訪問

評(píng)論