點(diǎn)擊上方藍(lán)字關(guān)注我們

一、前言

FPGA以擅長(zhǎng)高速并行數(shù)據(jù)處理而聞名,從有線/無(wú)線通信到圖像處理中各種DSP算法,再到現(xiàn)今火爆的AI應(yīng)用,都離不開卷積、濾波、變換等基本的數(shù)學(xué)運(yùn)算。但由于FPGA的硬件結(jié)構(gòu)和開發(fā)特性使得其對(duì)很多算法不友好,之前本人零散地總結(jié)和轉(zhuǎn)載了些基本的數(shù)學(xué)運(yùn)算在FPGA中的實(shí)現(xiàn)方式,今天做一個(gè)系統(tǒng)的總結(jié)歸納。

二、FPGA中的加減乘除

1.硬件資源

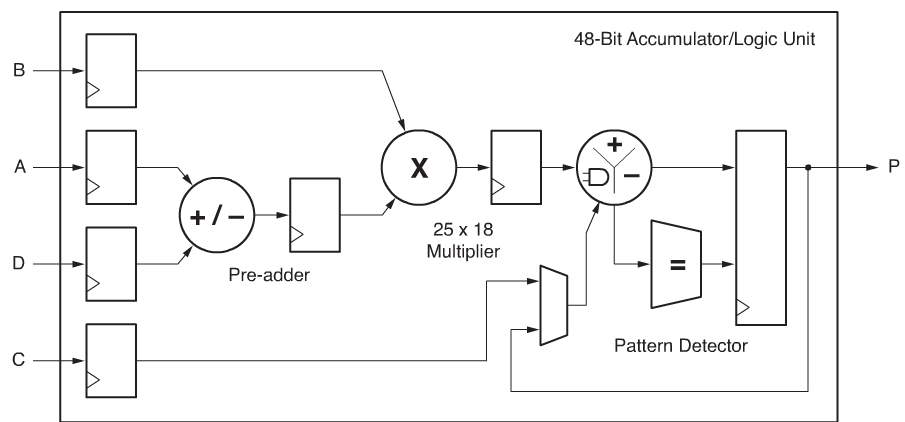

Xilinx 7系列的FPGA中有DSP Slice ,叫做“DSP48E1”這一專用硬件資源,這是一個(gè)功能強(qiáng)大的計(jì)算單元,單就用于基本運(yùn)算的部分有加減單元和乘法器。詳見參考文獻(xiàn)1.

因此可以直接用HDL語(yǔ)言中的加、減、乘符號(hào)實(shí)現(xiàn)變量與常量間運(yùn)算操作以及變量與變量間操作。而四則運(yùn)算中的除法沒有基本的邏輯計(jì)算單元可以對(duì)應(yīng),因此計(jì)算除法需要調(diào)用除法器IP核。

2.確認(rèn)數(shù)據(jù)的表示范圍

有符號(hào)數(shù):(補(bǔ)碼)-2^(N-1) ~ 2^(N-1)-1 如N = 8,則表示范圍是:-128 ~ 127.

無(wú)符號(hào)數(shù):0~2^N-1 如N = 8,則表示范圍是:0~255.

定點(diǎn)數(shù):2Q13 范圍是:-4~4-2^(-13) 精度是:2^(-13)

3.結(jié)果有效位寬

首先討論結(jié)果位寬問題。在FPGA中往往采用定點(diǎn)運(yùn)算替代浮點(diǎn)運(yùn)算來(lái)降低硬件資源占用率和計(jì)算延遲,其中的精髓就是精度與資源的權(quán)衡。若按照保留計(jì)算結(jié)果的全部精度,N bit數(shù)與Mbit數(shù)相加結(jié)果需要N+1bit(N>M)。N bit數(shù)與M bit數(shù)相乘之積需要N+M bit。而減法可以轉(zhuǎn)化為加法,除法則轉(zhuǎn)換為乘法和加減法的組合。如果操作數(shù)是定點(diǎn)小數(shù),則在滿足以上準(zhǔn)則的前提下,A與B相加(A小數(shù)點(diǎn)位數(shù)>B小數(shù)點(diǎn)位數(shù)),結(jié)果小數(shù)點(diǎn)位數(shù)與A相同;A與B相乘(小數(shù)點(diǎn)位數(shù)分別為p和q),結(jié)果小數(shù)點(diǎn)位數(shù)是p+q。

4.定點(diǎn)運(yùn)算步驟

然而(話鋒一轉(zhuǎn)),在大多數(shù)場(chǎng)合下,不需要以上這么多位來(lái)保留計(jì)算結(jié)果,因?yàn)槲覀冊(cè)谶M(jìn)行數(shù)學(xué)運(yùn)算時(shí),已經(jīng)知道輸入數(shù)據(jù)的大致范圍,一個(gè)數(shù)除以1000和除以1結(jié)果數(shù)據(jù)所需最小位寬能一樣么?加減運(yùn)算的操作步驟是先對(duì)齊小數(shù)點(diǎn)位數(shù),后加減。而乘法是先計(jì)算后取小數(shù)點(diǎn)。這實(shí)際上與十進(jìn)制運(yùn)算一致,我們看看具體的計(jì)算步驟:

整數(shù)之間加減以及乘法的統(tǒng)一步驟:預(yù)估結(jié)果位寬N --> 按照結(jié)果位寬擴(kuò)展操作數(shù)符號(hào)位以防止溢出 --> 運(yùn)算取低N位。

定點(diǎn)小數(shù)加減運(yùn)算步驟:預(yù)估結(jié)果位寬N --> 得到結(jié)果小數(shù)點(diǎn)后位數(shù) --> 對(duì)齊操作數(shù)整數(shù)位和小數(shù)位,確定擴(kuò)展位寬M(M≥N) --> 加減運(yùn)算取低M位。

定點(diǎn)小數(shù)乘法運(yùn)算步驟:預(yù)估結(jié)果位寬N --> 得到結(jié)果小數(shù)點(diǎn)后位數(shù) --> 擴(kuò)展操作數(shù)位寬 --> 相乘取低N位

5. 變量與常量運(yùn)算化簡(jiǎn)

以上討論的均是兩變量之間的運(yùn)算規(guī)則,當(dāng)然結(jié)果位寬及格式準(zhǔn)則是適用的。變量與常量的運(yùn)算的優(yōu)勢(shì)在于,可以將乘除法轉(zhuǎn)換成加減以及移位運(yùn)算實(shí)現(xiàn),從而降低計(jì)算復(fù)雜度和延遲。當(dāng)常數(shù)項(xiàng)C為2的整數(shù)次冪(C = 2^p),則乘C等于變量左移p位,除以C等于變量右移p位。幾個(gè)在書中看到的幾個(gè)簡(jiǎn)單示例:A*16 = A <<4 A*20 = A<<4 + A<<2. A除以2 = A >>1A除以3 = A*(0.25+0.0625+0.0156) = A>>2+A>>4+A>>6A除以5 = A*(0.125+0.0625+0.0156) = A>>3 + A>>4 + A>>6.其中乘法完全等價(jià)對(duì)應(yīng)的移位相加操作,而除法的移位代替會(huì)損失精度。

三、如何計(jì)算特殊函數(shù)

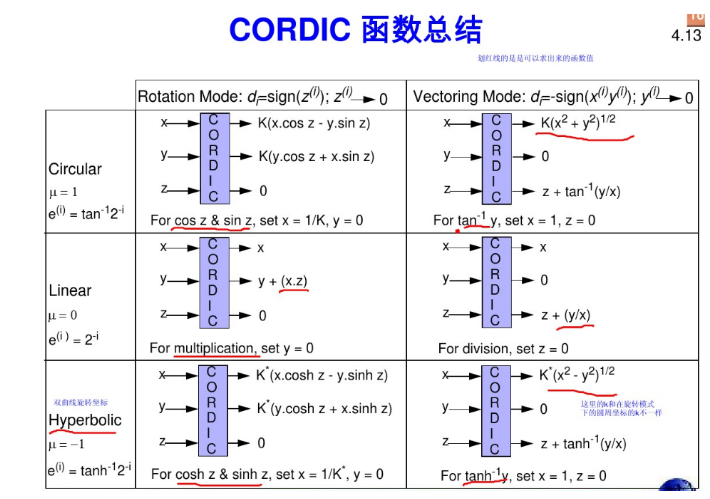

FPGA內(nèi)部的DSP Slice可以直接進(jìn)行最基本的加法和乘法運(yùn)算,但是對(duì)于其他比如對(duì)數(shù)、指數(shù)、三角函數(shù)、開根號(hào)等特殊函數(shù)就無(wú)能為力了。這時(shí)需要借助算法對(duì)這些特殊函數(shù)進(jìn)行變換和簡(jiǎn)化。FPGA實(shí)現(xiàn)復(fù)雜函數(shù)的常用手段一個(gè)是級(jí)數(shù)展開,再一個(gè)就是CORDIC算法。關(guān)于CORDIC的理論知識(shí)和具體內(nèi)容詳見參考文獻(xiàn)2,這里主要闡述CORDIC的IP核調(diào)用以及應(yīng)用示例。CORDIC算法就是通過(guò)一定的手段,將很多復(fù)雜的特殊函數(shù)變?yōu)橄嗉右莆贿\(yùn)算,這一點(diǎn)對(duì)于硬件芯片實(shí)現(xiàn)來(lái)說(shuō)非常友好。CORDIC分為旋轉(zhuǎn)模式和矢量模式,配合圓周坐標(biāo)、線性坐標(biāo)和雙曲線坐標(biāo)會(huì)有六種組合,具體見下表:

從表中發(fā)現(xiàn),基本的乘

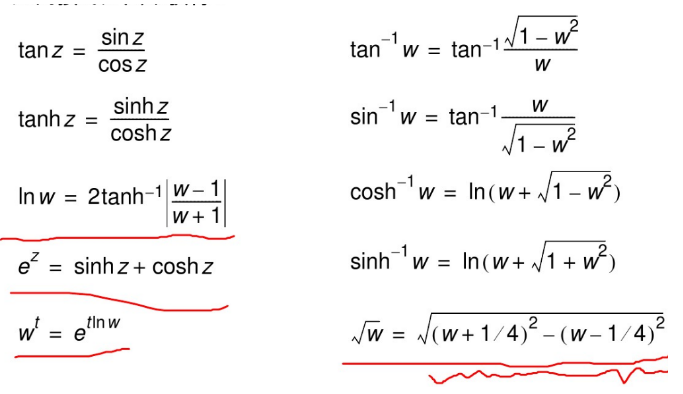

除法、三角函數(shù)、反三角函數(shù)、雙曲函數(shù)、反雙曲函數(shù)、開根號(hào)都能夠直接求得,那其他函數(shù)怎么辦?

常見的函數(shù)計(jì)算需求基本都能滿足,雖上述變換式對(duì)自變量定義域有限制,但同樣可以分析輸入數(shù)據(jù)的取值范圍并利用簡(jiǎn)單的數(shù)學(xué)變換得到想要的結(jié)果。Xilinx同時(shí)提供了浮點(diǎn)IP核以及CORDIC IP核,前者調(diào)用簡(jiǎn)單但占用資源大,延遲高,因此利用CORDIC算法計(jì)算函數(shù)是個(gè)較好的選擇。

四、CORDIC計(jì)算e^x Demo

1. 算法仿真分析

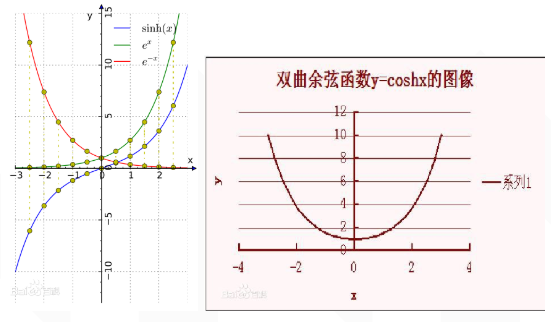

要計(jì)算e^x數(shù)值需要讓CORDIC工作在雙曲坐標(biāo)的旋轉(zhuǎn)模式下,通過(guò)e^x = sinhx+coshx關(guān)系式間接求得。首先看下sinh和cosh函數(shù)的曲線,有個(gè)直觀認(rèn)識(shí)。

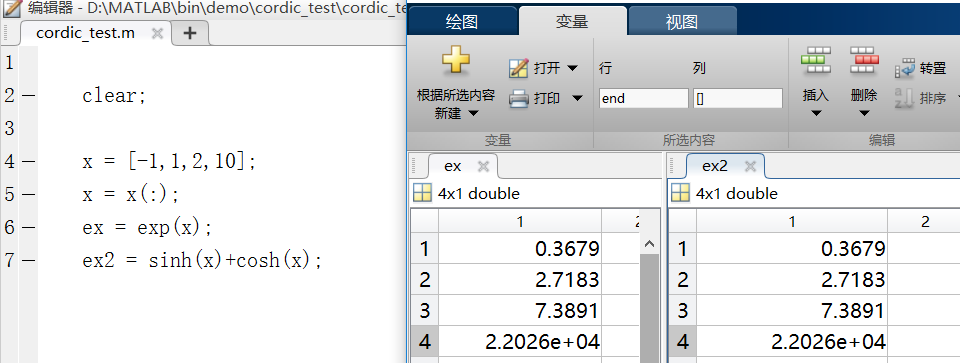

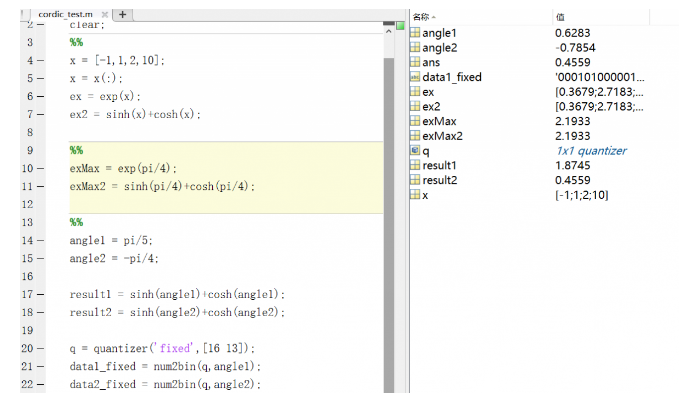

我們用MATLAB毫不費(fèi)力地驗(yàn)證一下公式正確性:

在設(shè)計(jì)后也同樣要借助MATLAB進(jìn)行仿真驗(yàn)證。

2. CORDIC IP核

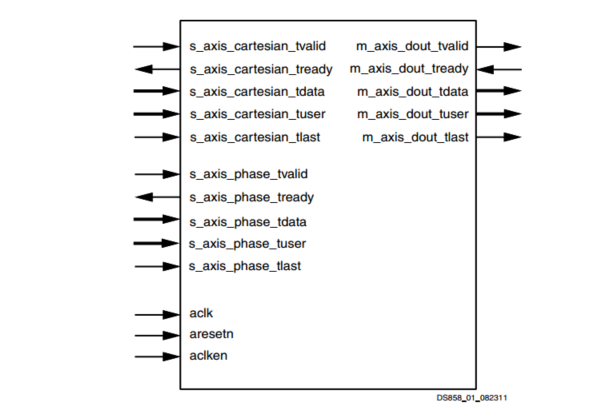

現(xiàn)在通過(guò)查看user guide得知CORDIC IP核的接口及主要特性。

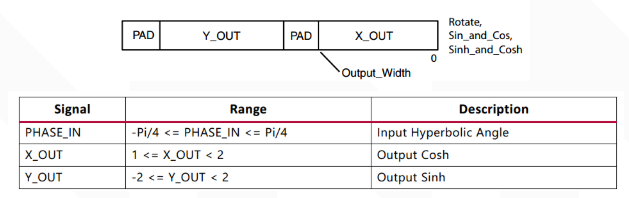

接口包括輸入笛卡爾數(shù)據(jù)輸入通道、相位輸入通道、全局信號(hào)以及數(shù)據(jù)輸出通道。該IP核有兩種結(jié)構(gòu):串行和并行,可根據(jù)數(shù)據(jù)吞吐量需求選擇,并行結(jié)構(gòu)可以每個(gè)時(shí)鐘輸出一個(gè)計(jì)算結(jié)果。如果計(jì)算sinh和cosh,要向phase通道輸入相位信息,X_OUT是cosh(phase),Y_OUT是sinh(phase).輸入phase必須滿足數(shù)據(jù)范圍,否則出現(xiàn)不可預(yù)計(jì)結(jié)果。輸出幀結(jié)構(gòu)及數(shù)據(jù)范圍如下:

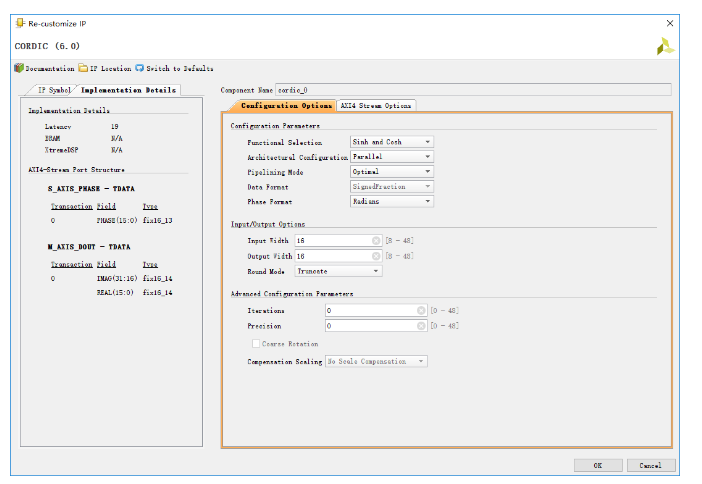

其中輸入數(shù)據(jù)格式為2QN,輸出則是1QN。由于均是有符號(hào)數(shù),也就是輸入整數(shù)部分3bit,輸出整數(shù)部分2bit。接下來(lái)對(duì)IP核進(jìn)行配置,重點(diǎn)是第一頁(yè),此處將其配置為計(jì)算sinh和cosh模式,采用并行優(yōu)化的流水線結(jié)構(gòu)。相位以角度為單位,輸入輸出位寬設(shè)置成16bit。

3.HDL代碼設(shè)計(jì)及仿真驗(yàn)證

設(shè)計(jì)代碼:

`timescale 1ns / 1ps

module cordic_ex#(parameter DIN_W = 16,

DOUT_W = 16)

(

input clk,

input [DIN_W-1:0] din,//2Q13

input din_vld,

output reg [DOUT_W+1-1:0] dout = 0,//2Q14

output reg dout_vld = 0

);

wire [DOUT_W*2-1 : 0] m_axis_dout_tdata;

wire m_axis_dout_tvalid;

wire signed [DOUT_W-1:0] sinh,cosh;

// ex = sinhx + coshx <1Q14+1Q14 = 2Q14>

always @(posedge clk)begin

dout <= sinh + cosh;

end

assign sinh = m_axis_dout_tdata[DOUT_W*2-1 -:DOUT_W];

assign cosh = m_axis_dout_tdata[DOUT_W-1 -:DOUT_W];

always @(posedge clk)begin

if(m_axis_dout_tvalid)begin

dout_vld <= 1'b1;

end

else

dout_vld <= 0;

end

cordic_0 cordic_cosh_sinh (

.aclk(clk), // input wire aclk

.s_axis_phase_tvalid(din_vld), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(din), // input wire [15 : 0] s_axis_phase_tdata

.m_axis_dout_tvalid(m_axis_dout_tvalid), // output wire m_axis_dout_tvalid

.m_axis_dout_tdata(m_axis_dout_tdata) // output wire [31 : 0] m_axis_dout_tdata

);

endmodule

cordic_ex

用MATLAB產(chǎn)生兩組數(shù)據(jù),并將角度值定點(diǎn)化后作為設(shè)計(jì)模塊數(shù)據(jù)激勵(lì):

testbench:

`timescale 1ns / 1ps

module cordic_ex_tb();

parameter CYC = 20;

reg clk;

reg [16-1:0] din;

reg din_vld;

wire signed [17-1:0] dout;

wire dout_vld;

cordic_ex#(.DIN_W(16),

.DOUT_W(16))

uut(

.clk (clk) ,

.din (din) ,//2Q13

.din_vld (din_vld) ,

.dout (dout) ,//2Q14

.dout_vld (dout_vld)

);

initial begin

clk = 1;

forever #(CYC/2) clk = ~clk;

end

initial begin

#1;

din = 0;

din_vld = 0;

#(CYC*10);

din_vld = 1;

din = 16'b0001010000011011;//pi * 1/5

#(CYC*1);

din = 16'b1110011011011110;//-pi * 1/4

#5;

$stop;

end

endmodule

cordic_ex_tb

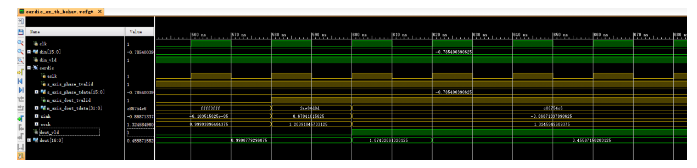

仿真結(jié)果:

仿真波形表明,計(jì)算結(jié)果與MATLAB浮點(diǎn)運(yùn)算相近,滿足一般計(jì)算需求。若想提高精度,可以增加CORDIC輸出數(shù)據(jù)位寬。

有你想看的精彩 至芯科技-FPGA就業(yè)培訓(xùn)來(lái)襲!你的選擇開啟你的高薪之路!7月12號(hào)北京中心開課、歡迎咨詢! 如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī) 基于FPGA的電子按鍵密碼鎖設(shè)計(jì)

掃碼加微信邀請(qǐng)您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:利用FPGA進(jìn)行基本運(yùn)算及特殊函數(shù)定點(diǎn)運(yùn)算

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605993

原文標(biāo)題:利用FPGA進(jìn)行基本運(yùn)算及特殊函數(shù)定點(diǎn)運(yùn)算

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

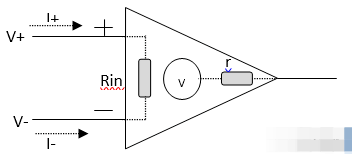

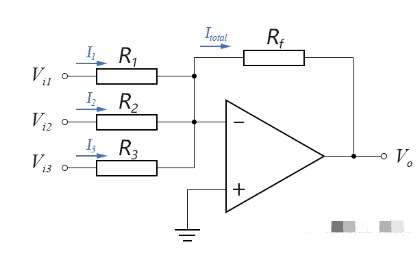

如何使用運(yùn)算放大器進(jìn)行模擬信號(hào)處理

FPGA中的浮點(diǎn)四則運(yùn)算是什么

FPGA中浮點(diǎn)四則運(yùn)算的實(shí)現(xiàn)過(guò)程

基于FPGA的計(jì)算器設(shè)計(jì)

MATLAB(4)--MATLAB基本運(yùn)算

c語(yǔ)言從右到左的運(yùn)算符有哪些

cpu的運(yùn)算器和控制器的作用是什么

FPGA設(shè)計(jì)經(jīng)驗(yàn)之圖像處理

請(qǐng)問stm8如何進(jìn)行floa和long運(yùn)算?

優(yōu)秀的Verilog/FPGA開源項(xiàng)目-浮點(diǎn)運(yùn)算器(FPU)介紹

關(guān)于比例運(yùn)算電路的疑惑

運(yùn)算放大器的工作原理和基本電路 使用運(yùn)算放大器的電路設(shè)計(jì)

利用FPGA進(jìn)行基本運(yùn)算及特殊函數(shù)定點(diǎn)運(yùn)算

利用FPGA進(jìn)行基本運(yùn)算及特殊函數(shù)定點(diǎn)運(yùn)算

評(píng)論