如何減少GPIO數(shù)量?

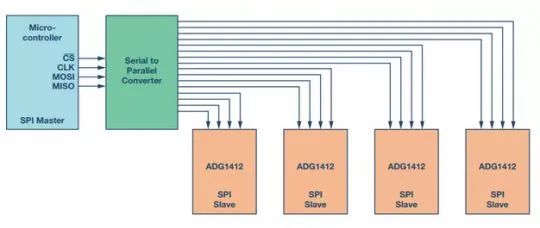

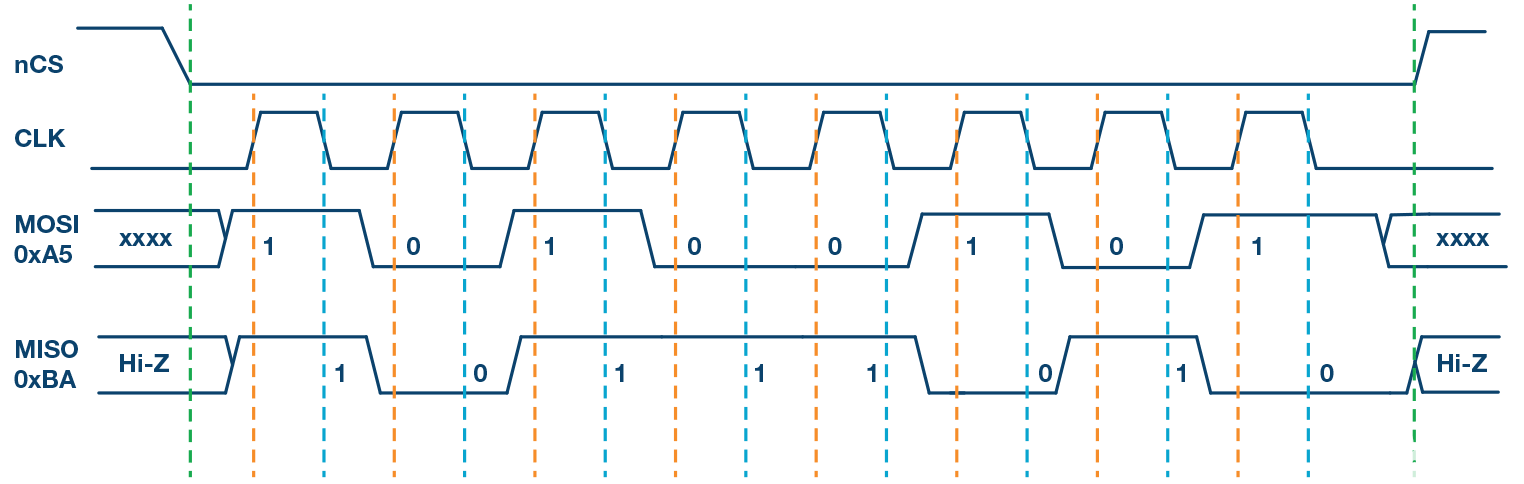

一種方法是使用串行轉(zhuǎn)并行轉(zhuǎn)換器,如圖所示。該器件輸出的并行信號(hào)可連接到開(kāi)關(guān)控制輸入,器件可通過(guò)串行接口SPI配置。此方法的缺點(diǎn)是外加器件會(huì)導(dǎo)致物料清單增加。

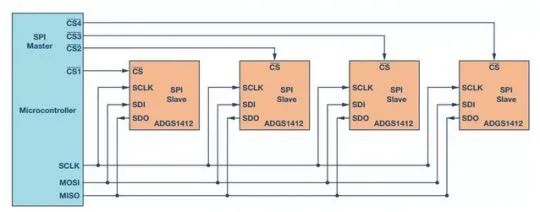

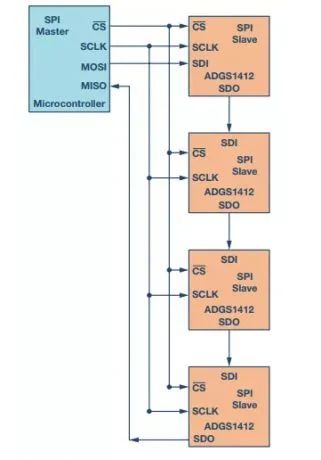

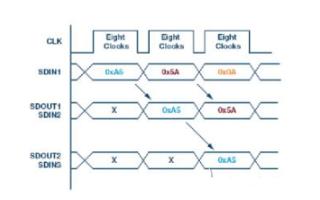

另一種方法是使用SPI控制的開(kāi)關(guān)。此方法的優(yōu)點(diǎn)是可減少所需GPIO的數(shù)量,并且還能消除外加串行轉(zhuǎn)并行轉(zhuǎn)換器的開(kāi)銷。如圖所示,不需要16個(gè)微控制器GPIO,只需要7個(gè)微控制器GPIO就可以向4個(gè)ADGS1412提供SPI信號(hào)。開(kāi)關(guān)可采用菊花鏈配置,以進(jìn)一步優(yōu)化GPIO數(shù)量。在菊花鏈配置中,無(wú)論系統(tǒng)使用多少開(kāi)關(guān),都只使用主機(jī)(微控制器)的四個(gè)GPIO。

圖用于說(shuō)明目的。ADGS1412數(shù)據(jù)手冊(cè)建議在SDO引腳上使用一個(gè)上拉電阻。為簡(jiǎn)單起見(jiàn),此示例使用了四個(gè)開(kāi)關(guān)。隨著系統(tǒng)中開(kāi)關(guān)數(shù)量的增加,電路板簡(jiǎn)單和節(jié)省空間的優(yōu)點(diǎn)很重要。

在6層電路板上放置8個(gè)四通道SPST開(kāi)關(guān),采用4×8交叉點(diǎn)配置時(shí),ADI 公司支持 SPI 的開(kāi)關(guān)可節(jié)省20%的總電路板空間。

SPI協(xié)議的優(yōu)缺點(diǎn)

SPI 的優(yōu)點(diǎn)在于它有著比 I2C 更高的吞吐量,不被最大時(shí)鐘速度所限制,可實(shí)現(xiàn)潛在的高速、極為簡(jiǎn)單的硬件接口,外圍電路使用的上拉電阻是比 I2C

協(xié)議更少的,這意味著它具有比I2C的功耗更低、從機(jī)的時(shí)鐘來(lái)源來(lái)自主機(jī)設(shè)備,無(wú)需新增精密振蕩器、從機(jī)不需要唯一的地址、相對(duì)于并行接口而言,使用的引腳數(shù)目大大減少等優(yōu)點(diǎn)。

但同時(shí)有著一定的缺點(diǎn),例如SPI沒(méi)有帶內(nèi)尋址、當(dāng)使用多個(gè)不同模式的從機(jī)設(shè)備時(shí),主機(jī)設(shè)備切換模式時(shí)重新初始化,會(huì)使得訪問(wèn)從機(jī)設(shè)備速度變慢、SPI從機(jī)設(shè)備沒(méi)有硬件流控,只能通過(guò)主機(jī)自主的延遲下個(gè)時(shí)鐘周期到來(lái)的時(shí)間、僅能在短距離通信等缺點(diǎn)。但能在避免SPI的缺點(diǎn)的方向來(lái)應(yīng)用SPI的話,SPI的優(yōu)點(diǎn)讓它遠(yuǎn)遠(yuǎn)優(yōu)于其他協(xié)議。

-

通信

+關(guān)注

關(guān)注

18文章

6072瀏覽量

136427 -

SPI

+關(guān)注

關(guān)注

17文章

1722瀏覽量

92130 -

GPIO

+關(guān)注

關(guān)注

16文章

1216瀏覽量

52381

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

通信協(xié)議是指什么?串行通信和并行通信的優(yōu)缺點(diǎn)分別有哪些

SPI是什么?SPI接口有哪些優(yōu)缺點(diǎn)

ARM架構(gòu)優(yōu)缺點(diǎn)是什么?

LwIP的優(yōu)缺點(diǎn)是什么

ASCII和hex十六進(jìn)制的優(yōu)缺點(diǎn)是什么?

Net模塊中的通信傳輸協(xié)議有何優(yōu)缺點(diǎn)

SPI接口簡(jiǎn)介 如何減少系統(tǒng)電路板設(shè)計(jì)中的數(shù)字GPIO數(shù)量

SPI接口如何幫助減少系統(tǒng)板設(shè)計(jì)中的數(shù)字GPIO數(shù)量

SPI與I2C的異同及優(yōu)缺點(diǎn)

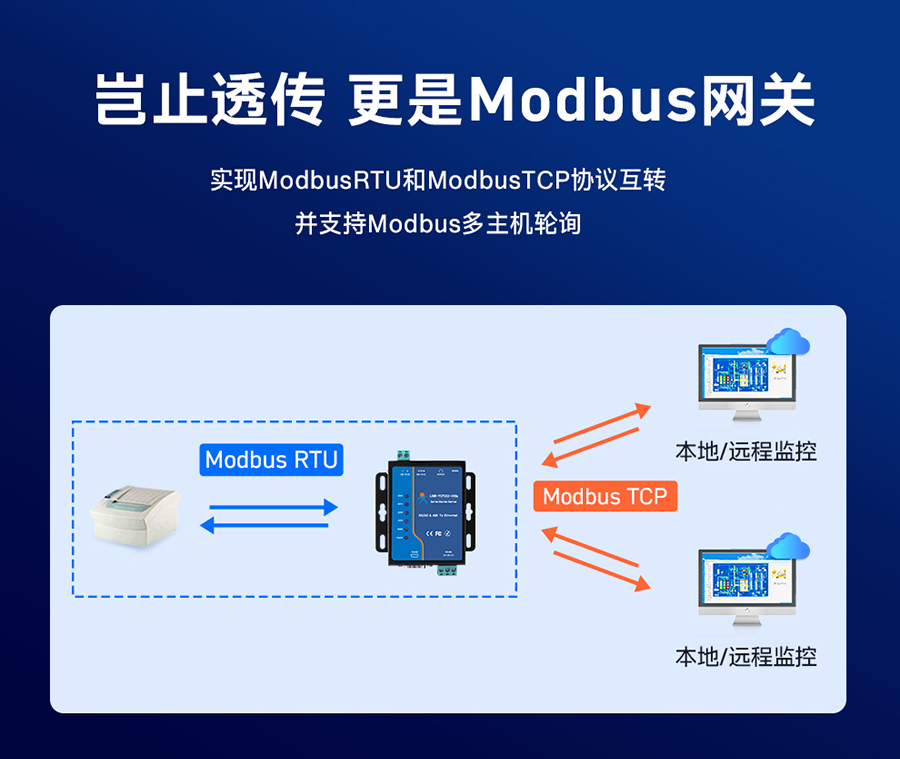

Modbus協(xié)議的工作原理、優(yōu)缺點(diǎn)及應(yīng)用

SPI協(xié)議優(yōu)缺點(diǎn) 如何減少GPIO數(shù)量

SPI協(xié)議優(yōu)缺點(diǎn) 如何減少GPIO數(shù)量

評(píng)論