PCIe接口全稱PCI Express,由PCI-SIG組織發布的用于替代PCI總路線的新一代高速串行總線與接口。PCIe接口版本經歷PCIe1.0、PCIe2.0、PCIe3.0,目前主流應用的PCIe接口為PCIe2.0。

PCIe作為高速差分串行接口用于替代PCI單端并行接口,在進行物理層信號測試時,不同于PCI利用同步時鐘(33MHz)進行數據讀寫,PCIe通過高達2.5Gbps的速率對信號進行收發操作,硬件測試時主要關注其參考時鐘(100MHz)和差分收發信號(2.5Gbps或5Gbps)。

PCIe接口硬件特性

PCIe規范非常復雜,規格分為基本標準(Base)和CEM標準(Card Electromechanical),前者主要描述PCIe的基本結構、協議、鏈路層、物理層以及軟件接口,適用于所有PCIe接口,后者重點關注PCIe接口在PCI桌面/服務器中的應用策略,包括各種類型的插卡的定義與使用等,兩個規范互有關聯,要理解芯片級互連的硬件(電氣)特性要求,需要深入分析兩個規范。

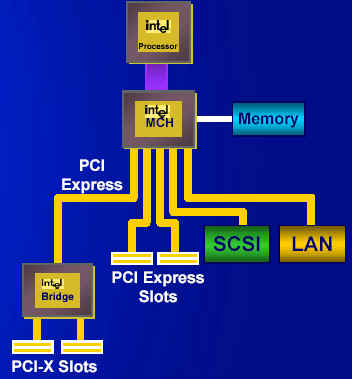

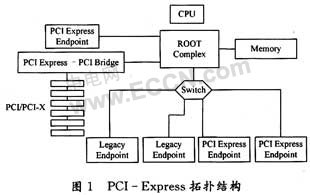

PCIe基本拓撲結構

PCIe CEM標準規范根據PCIe器件的位置將PCIe分成三種拓撲結構:

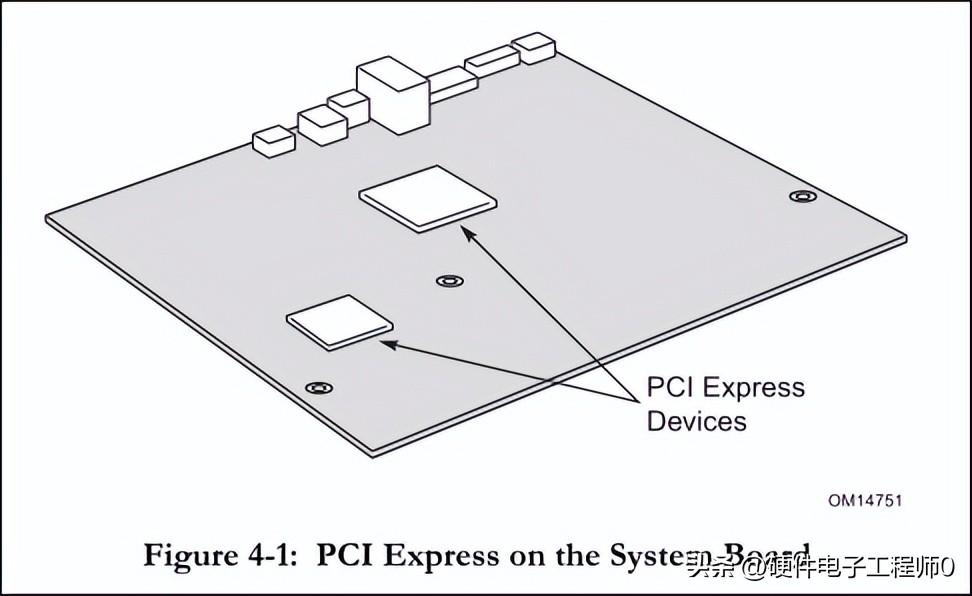

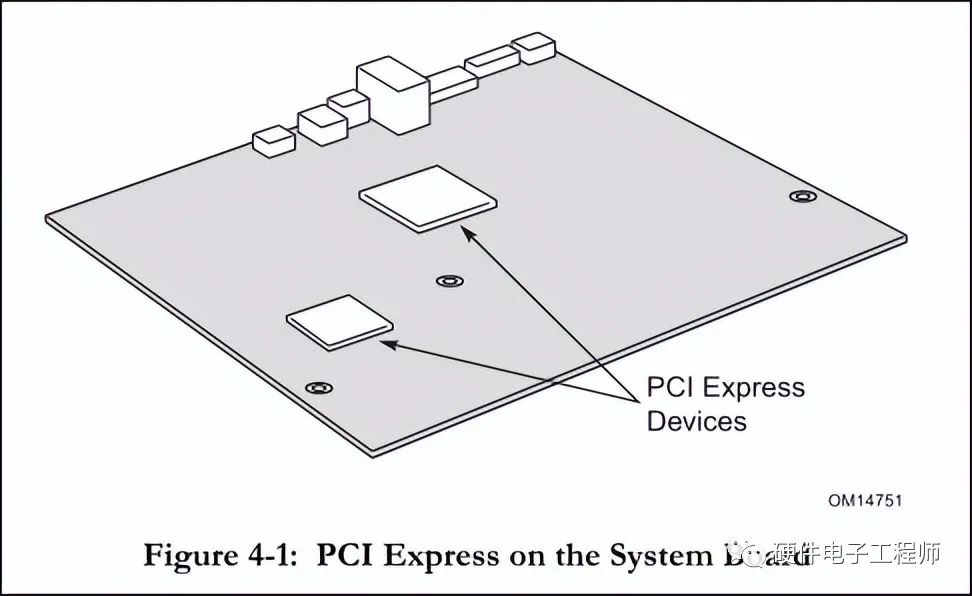

芯片級互連,PCIe器件在同一系統單板上;

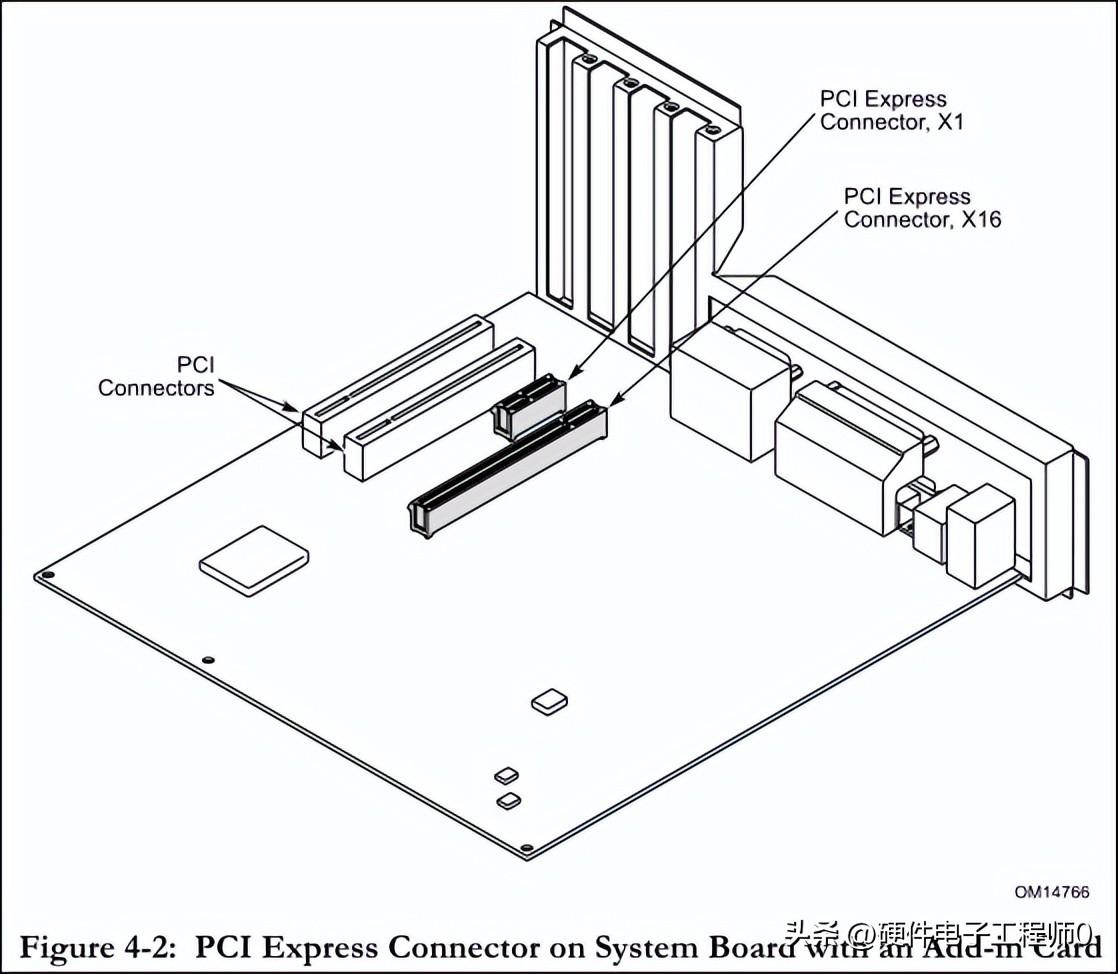

插卡級互連,PCIe器件通過插卡與系統板插座互連,系統板和插卡上各有一個PCIe器件;

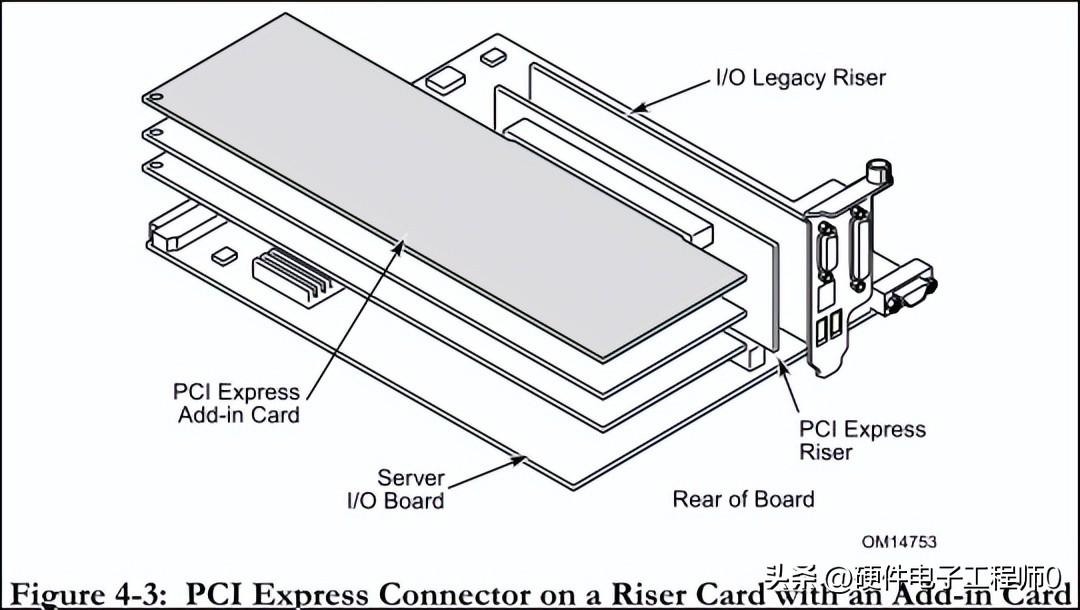

背板級互連,PCIe器件分別在兩種插卡,通過背板(或系統板)上插座完成PCIe互連。

圖2.1?1、芯片級互連

圖2.1?2、插卡級互連

圖2.1?3、背板級互連

其中,插卡級互連與背板級互連多用于PC或服務器的主板,PCIe CEM規范對其硬件電氣特性描述非常詳細,且主流的高端示波器廠家都提供了一致性測試夾具和軟件,這里不作描述。

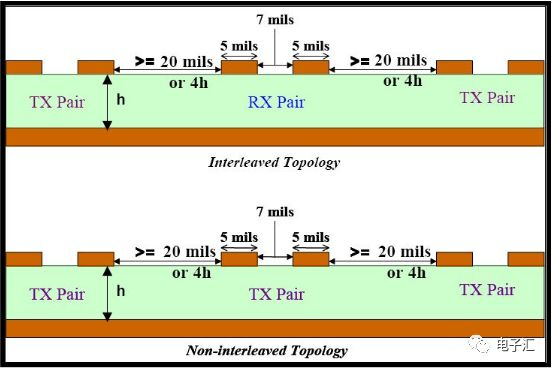

芯片級互連PCIe電氣特性

芯片級PCIe互連在通信產品中應用極為廣泛,目前幾乎完全替代PCI接口,成為了芯片互連的標準接口。芯片級PCIe接口通過是1 lane的差分串行線連接,主要信號包括復位、參考時鐘Refclk以及收發差分串行SerDes信號,復位信號較為簡單,PCIe規范沒有特殊要求,本文重點討論Refclk與SerDes信號要求與測試。

參考時鐘Refclk±

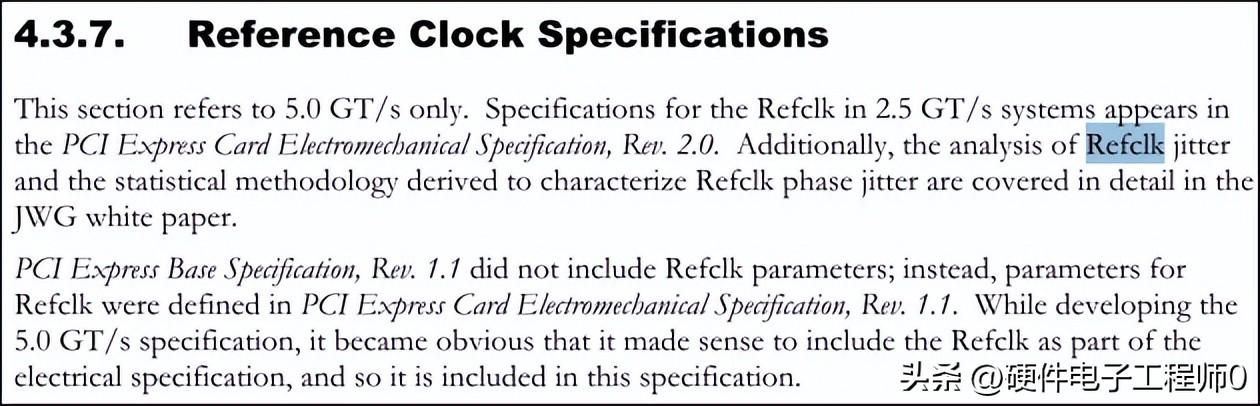

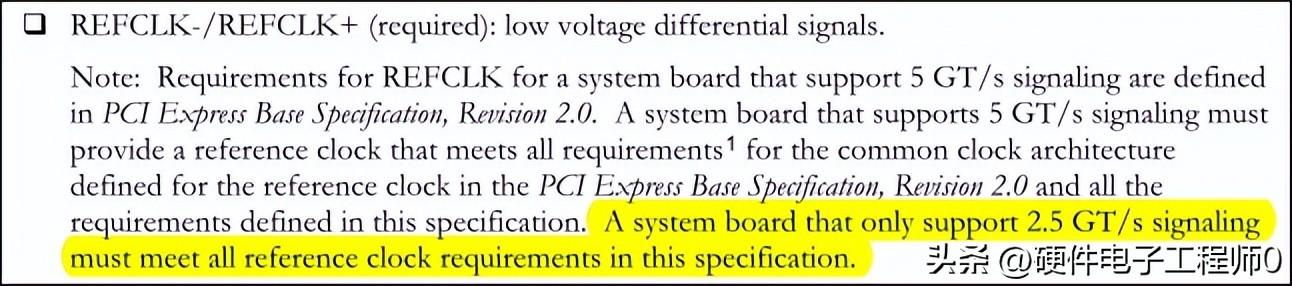

關于PCIe參考時鐘, PCIe Base 2.1規范中沒有對Refclk的電氣特性有明確說明,只是在4.3.7章節說明對于2.5GT/s系統的時鐘參考《PCE Express Card Electromechanical Specification, Rev.2.0》。

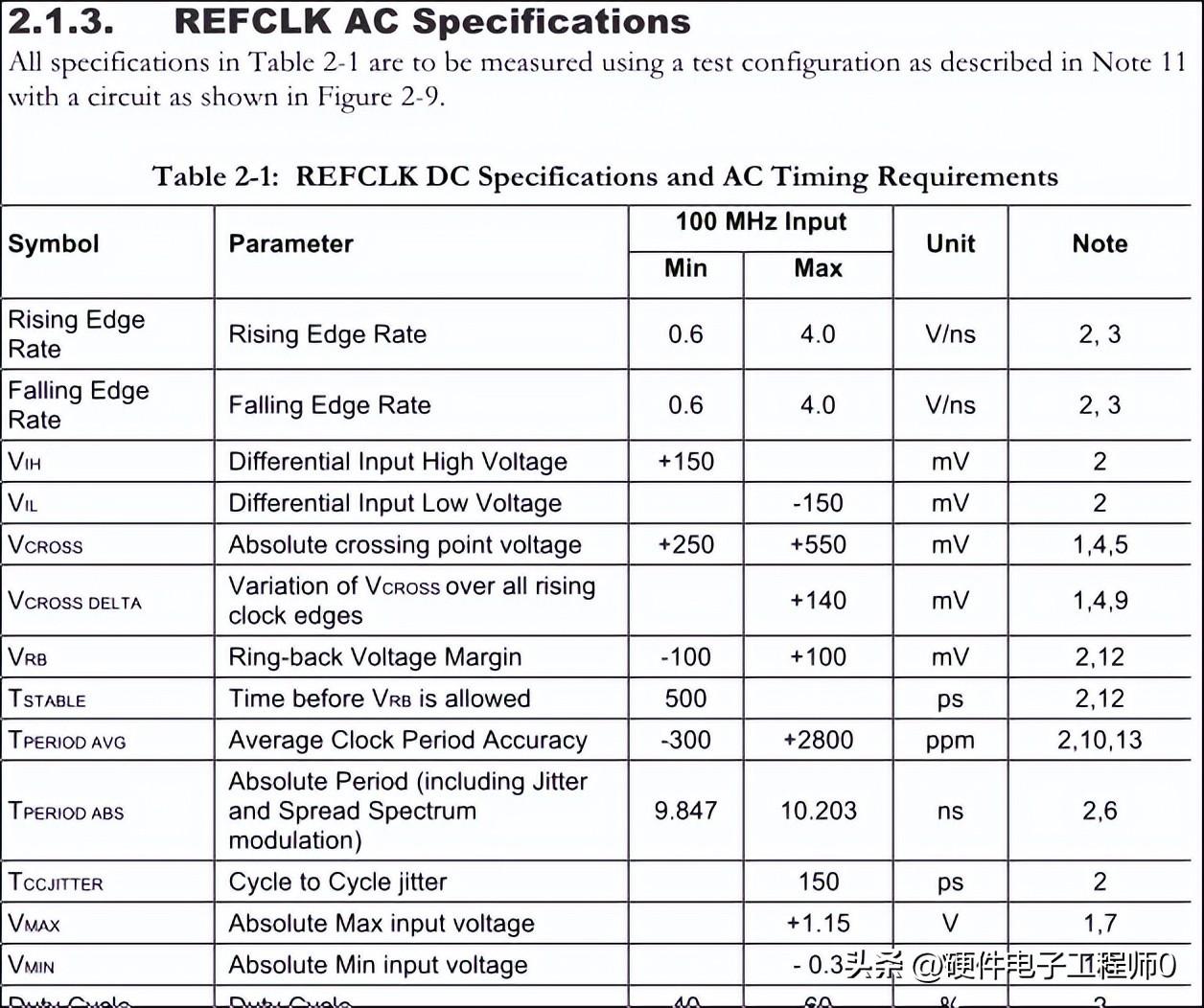

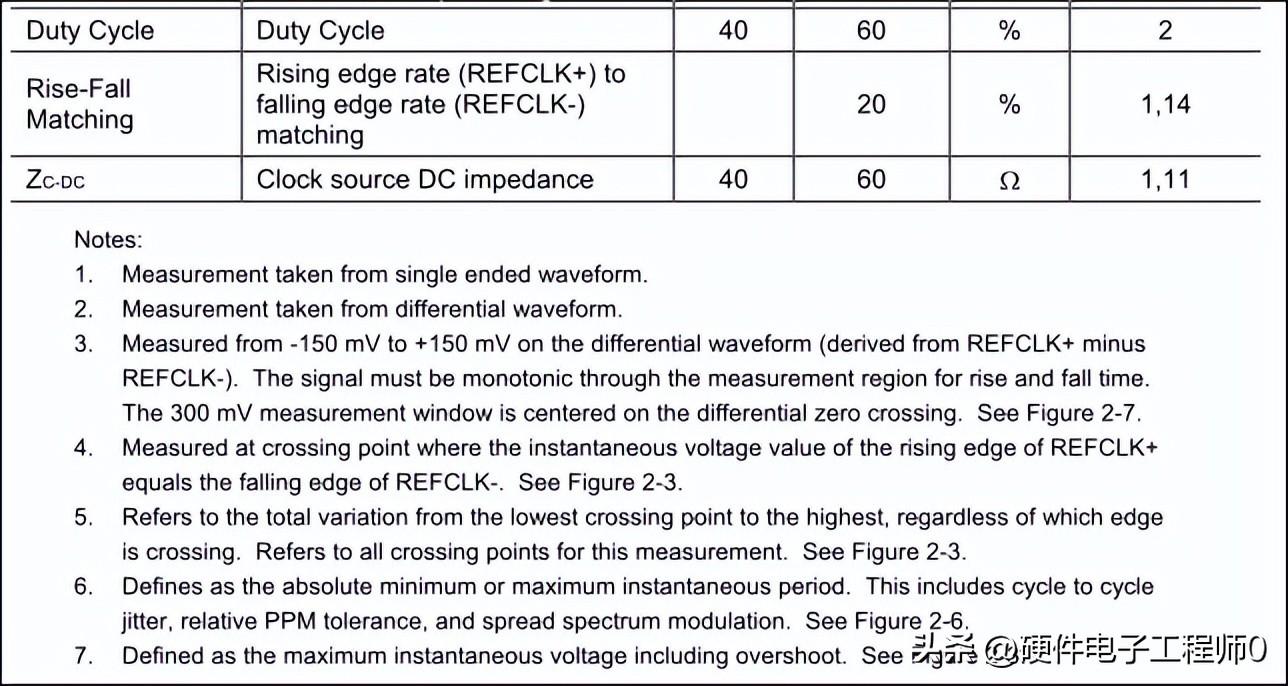

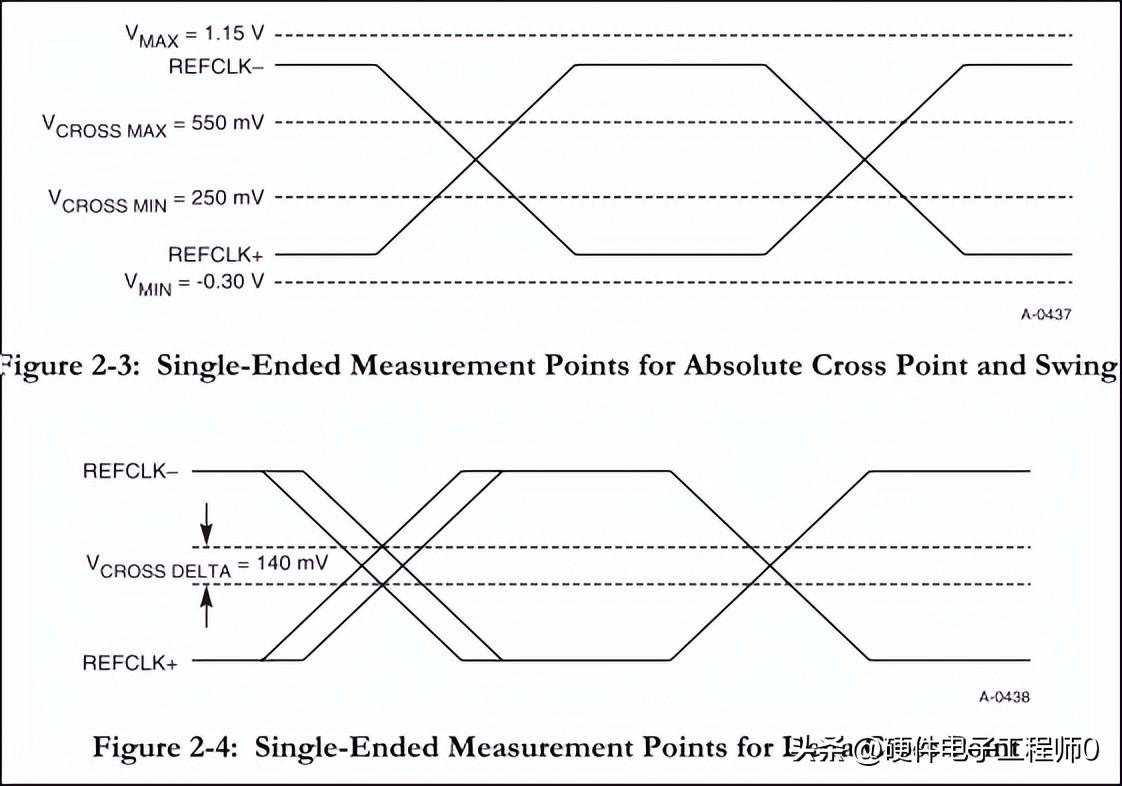

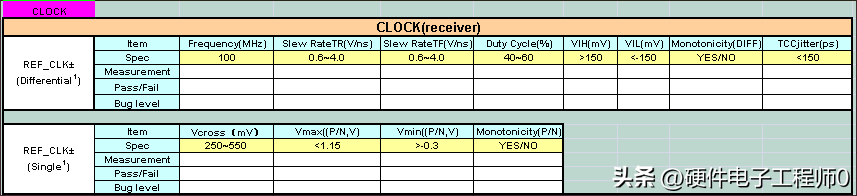

查看PCIe card 2.0,對差分時鐘Refclk±有明確的電氣特性要求,如下所示。

從規范的要求來看,對輸入參考時鐘重點關注時鐘頻率(周期)、占空比、上升/下降沿、差分輸入高低電平、邊沿單調性、單端交叉點電平以及周期間抖動等指標。

對于PCIe參考時鐘的使用,一般也有兩結構Common-clock bus與 Source synchronous bus,前者是通過晶振或差分時鐘驅動器同時給PCIe的主(master)從(slave)器件提供參考時鐘,后者是同主器件驅動時鐘給從器件接收。對于common-clock模式,主從器件的參考時鐘都要測試,PCIe接口中的參考時鐘只是作為基準時鐘使用,對差分信號沒有同步要求,所以不需要測試主從時鐘的時延skew,對source syschronous模式,只需要在從器件測試參考時鐘的接收端即可。

高速串行差分信號RXD±與TXD±

PCIe2.X支持5GT/s和2.5GT/s兩種速率,對于板內芯片級互連來說,驅動端(Transimitter)信號質量不是最重要的,重點關注接收端(Receiver)信號的電氣特性要求。

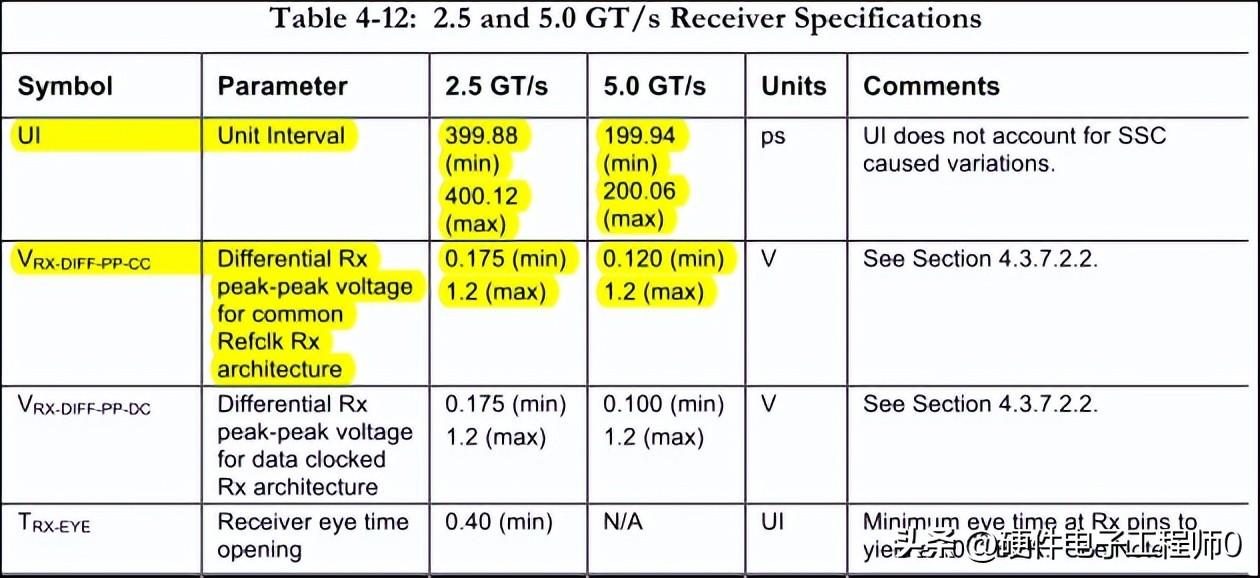

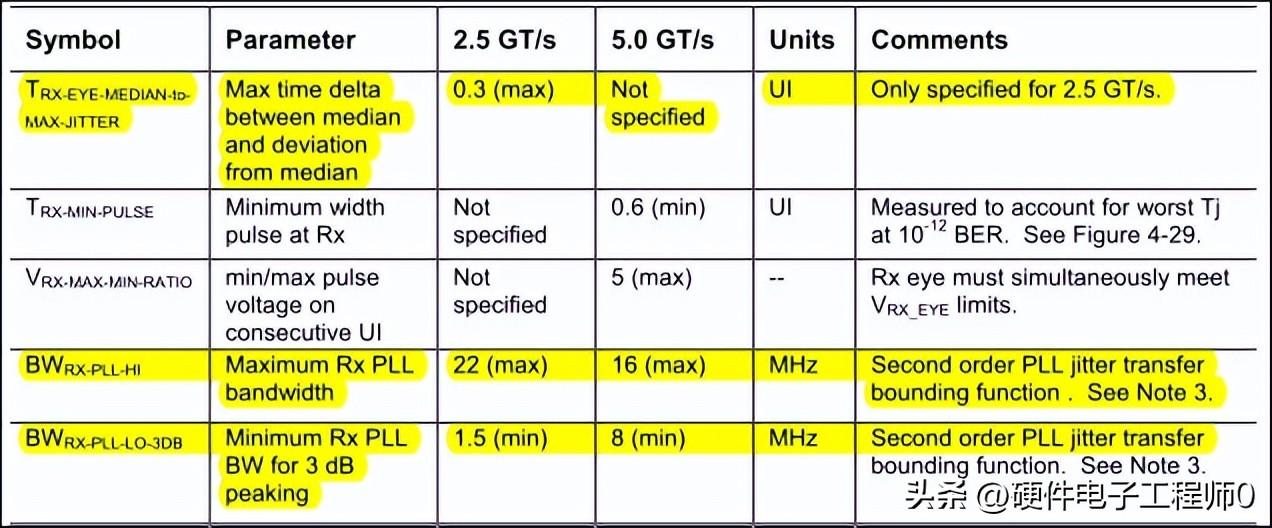

PCIe Base 2.1中第4.3.4章節對Receiver的電氣特性有了明確要求。

從規范得出,Receiver重點關注差分信號眼圖和抖動,對應VRX-DIFF-PP-CC和TRX-EYE-MEDIAN-to-MAX-JITTER,同時,測試時需要設計Rx PLL的帶寬。

PCIe接口硬件測試

根據上述章節對芯片級PCIe硬件電氣特性的描述,PCIe硬件測試主要包括PCIe參考時鐘測試和PCIe接收端信號測試。

PCIe參考時鐘測試

PCIe參考時鐘Refclk±為差分信號,分單端測試和差分測試,前者使用兩個有源單端探頭同時測試參考時鐘的正負端,測量交叉點電壓VCROSS,同進觀察邊沿單調性;后者利用差分探頭測試差分時鐘的正負端,測量項包括頻率、上升/下降沿斜率、差分高低電平、點空比、邊沿單調性、時鐘抖動等。具體測量項見下表所示。

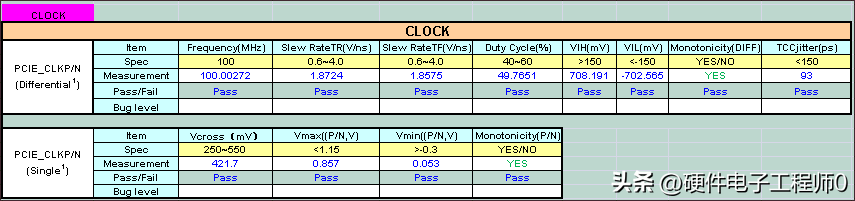

表3.1?1、PCIe參考時鐘特性測試數據

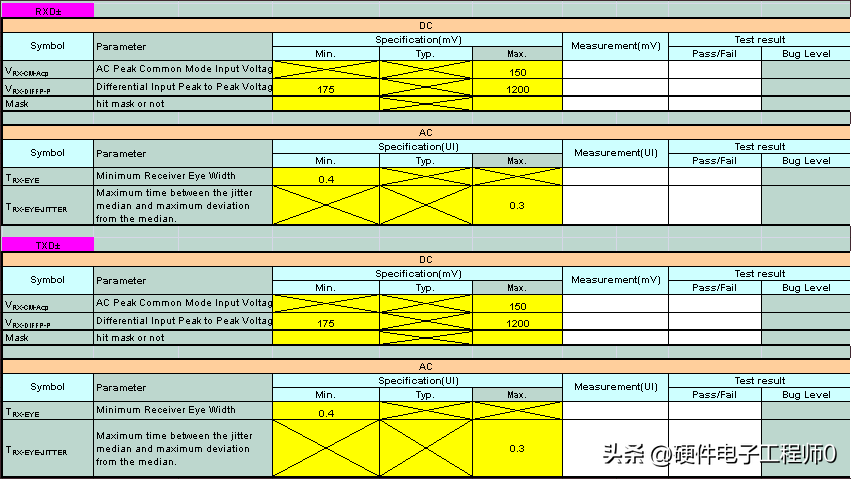

PCIe接收端信號測試

PCIe串行數據信號測試,只測試信號的接收端(RXD在master端測試,TXD在slave端測試),測試點盡量靠近芯片引腳處。因PCIe規范對數據交叉電壓沒有要求,數據信號主要是測試差分信號,單端不作測試。測試內容分為眼圖和抖動,測試時注意示波器PLL帶寬的設置。

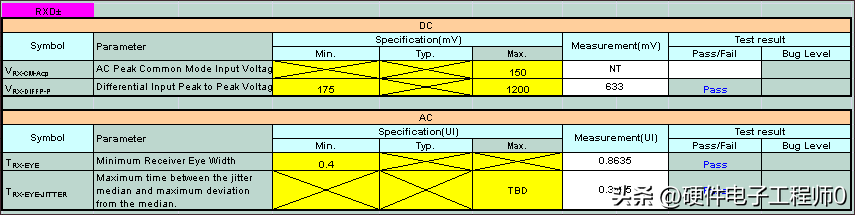

表3.2?1、PCIe數據測試數據

PCIe硬件測試案例

以某通信產品為例,測試其WIFI與CPU互連的PCIe接口信號,測試結果如下。

表3.3?1、 PCIe時鐘測試數據

表3.3?2、 PCIe時鐘測試數據

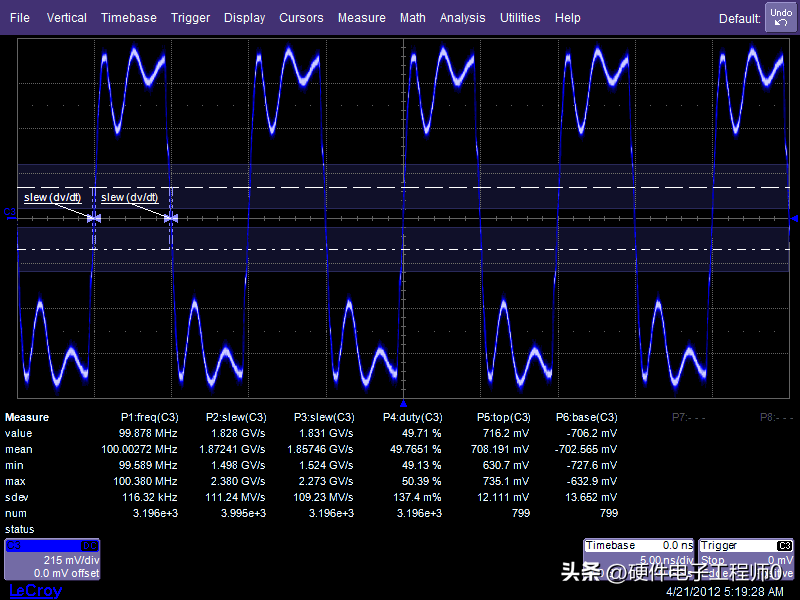

圖3.3?1、PCIe參考時鐘測試波形

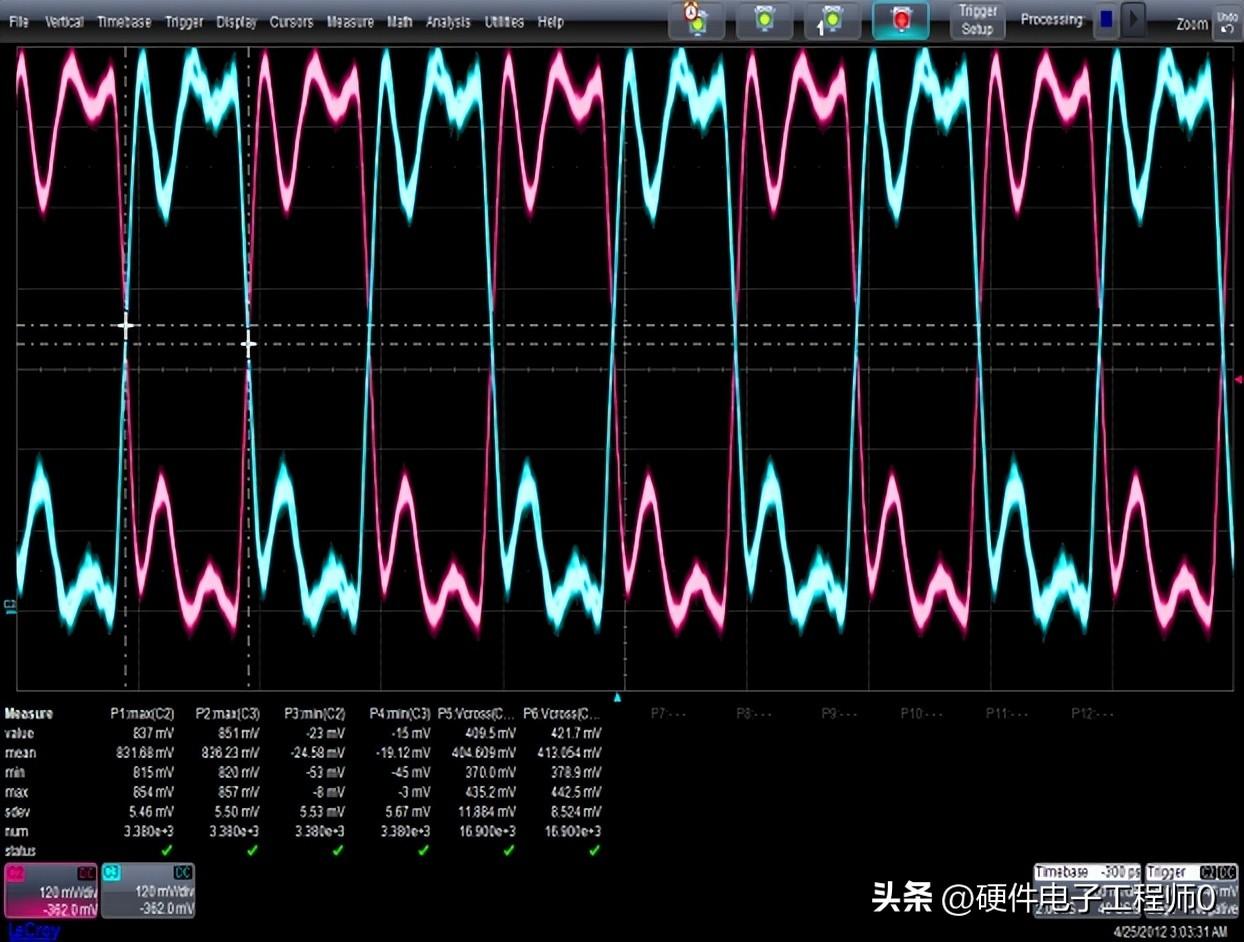

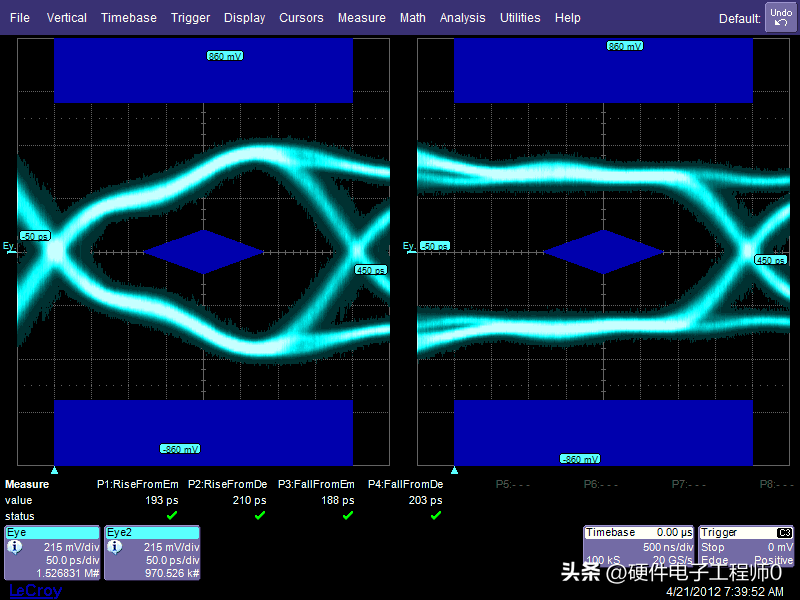

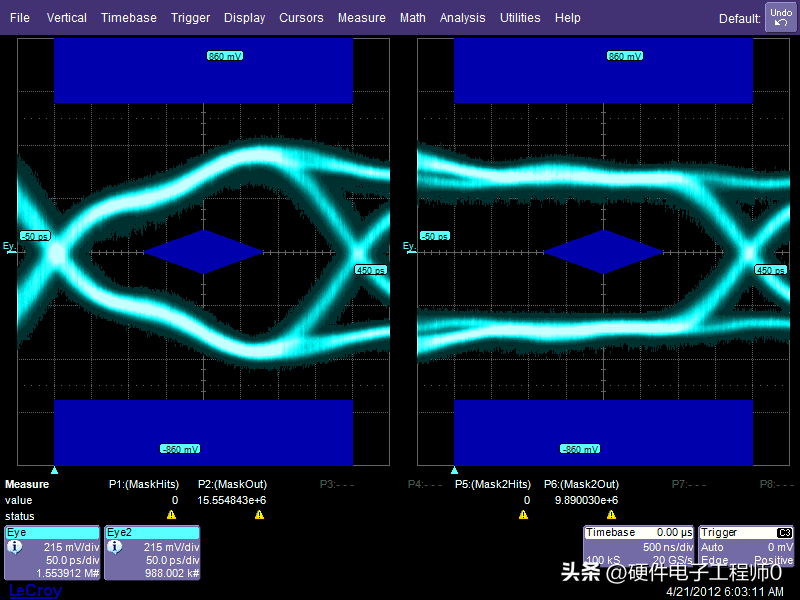

圖3.3?2、PCIe接收端RXD測試眼圖

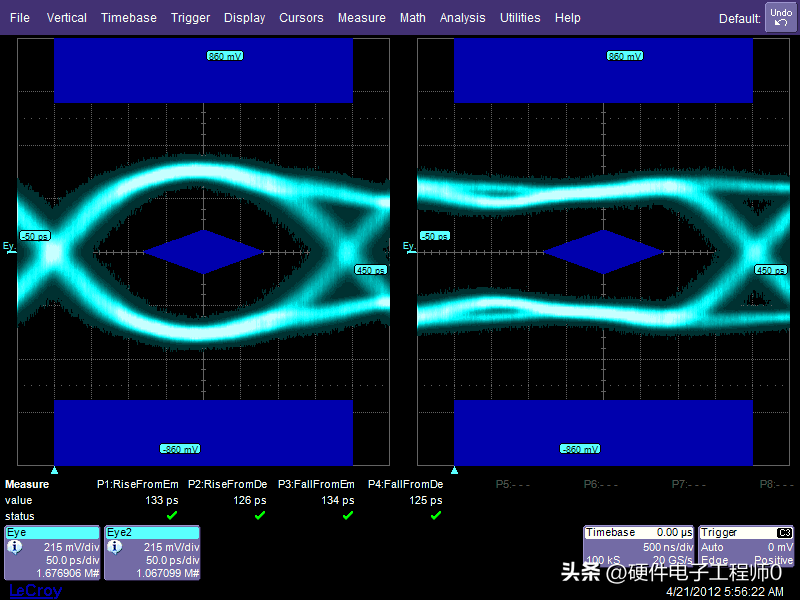

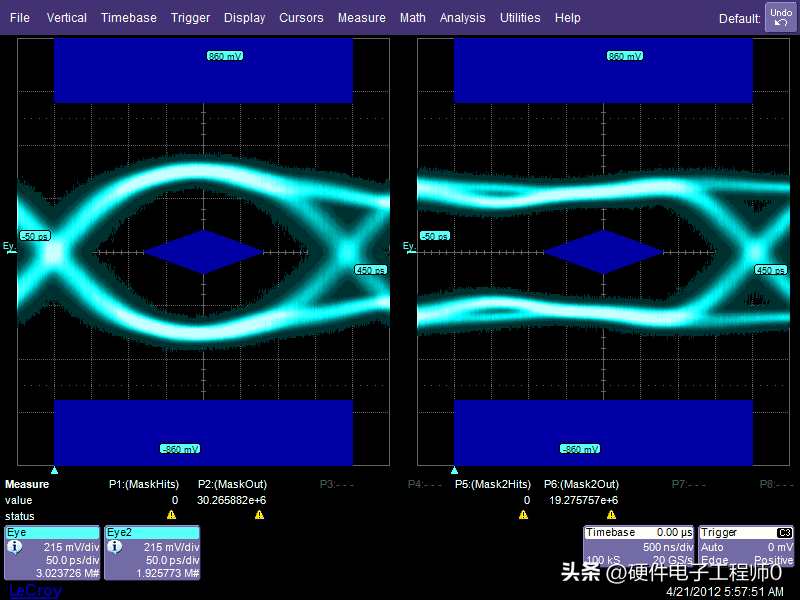

圖3.3?3、PCIe接收端TXD測試眼圖

審核編輯:劉清

-

示波器

+關注

關注

113文章

6282瀏覽量

185838 -

高電平

+關注

關注

6文章

154瀏覽量

21499 -

時鐘驅動器

+關注

關注

0文章

34瀏覽量

13883 -

PCIe接口

+關注

關注

0文章

121瀏覽量

9788

發布評論請先 登錄

相關推薦

如何進行PCI-Express的一致性測試和分析

基于PCI-Express的高速數據交換設計及應用

如何對PCI-Express總線的SSC(擴頻時鐘)進行驗證

pci express總線概念

PCI Express插槽,什么是PCI Express插槽

基于Virtex5的PCI-Express總線接口設計

PCI-Express插槽

從PCI、PCI-X到PCI-Express之間的連接

【科普】一文讀懂PCI-Express硬件接口

【科普】一文讀懂PCI-Express硬件接口

評論