提起芯片,大家應(yīng)該都不陌生。芯片,也就是IC(Integrated Circuit集成電路)作為一項(xiàng)高科技產(chǎn)業(yè),是當(dāng)今世界上各個(gè)國(guó)家都大力發(fā)展研究的產(chǎn)業(yè)。IC產(chǎn)業(yè)主要包含IC設(shè)計(jì)業(yè)、IC制造業(yè)以及IC封裝測(cè)試業(yè)三個(gè)部分,通過(guò)本文我們將帶大家認(rèn)識(shí)一下IC封測(cè)中的芯片封裝技術(shù)。

02何謂芯片封裝

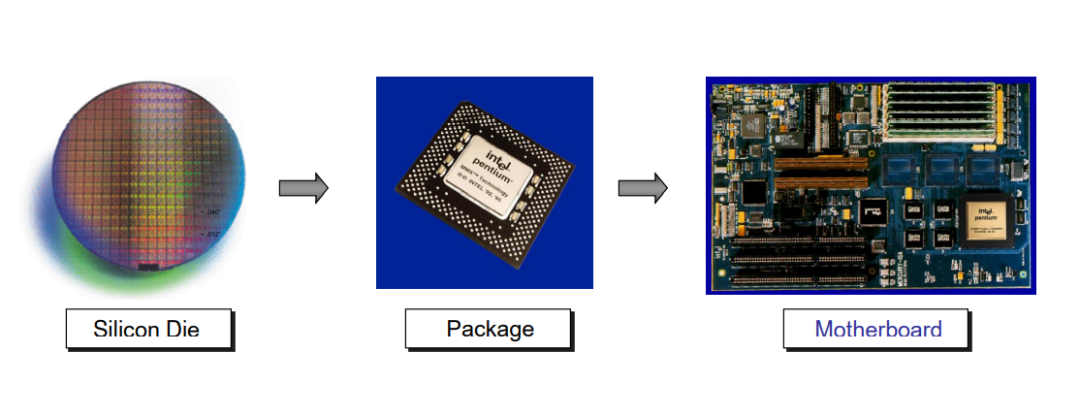

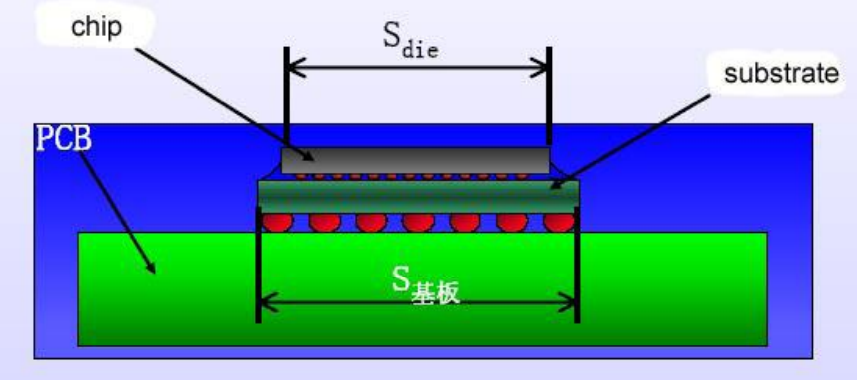

圖 1 芯片封裝的定位

生活中說(shuō)起封裝,可能就是把東西放進(jìn)箱子,然后用膠帶封口,箱子起到的最大作用也就是儲(chǔ)存,將箱子里面與箱子外面分隔開(kāi)來(lái)。但在芯片封裝中,“箱子”可有著更大的作用。安裝集成電路芯片用的外殼,它不僅起著安放、固定、密封、保護(hù)芯片和增強(qiáng)導(dǎo)熱性能的作用,而且還是溝通芯片內(nèi)部世界與外部電路的橋梁——芯片上的接點(diǎn)用導(dǎo)線(xiàn)連接到封裝外殼的引腳上,這些引腳又通過(guò)印刷電路板上的導(dǎo)線(xiàn)與其他器件建立連接。

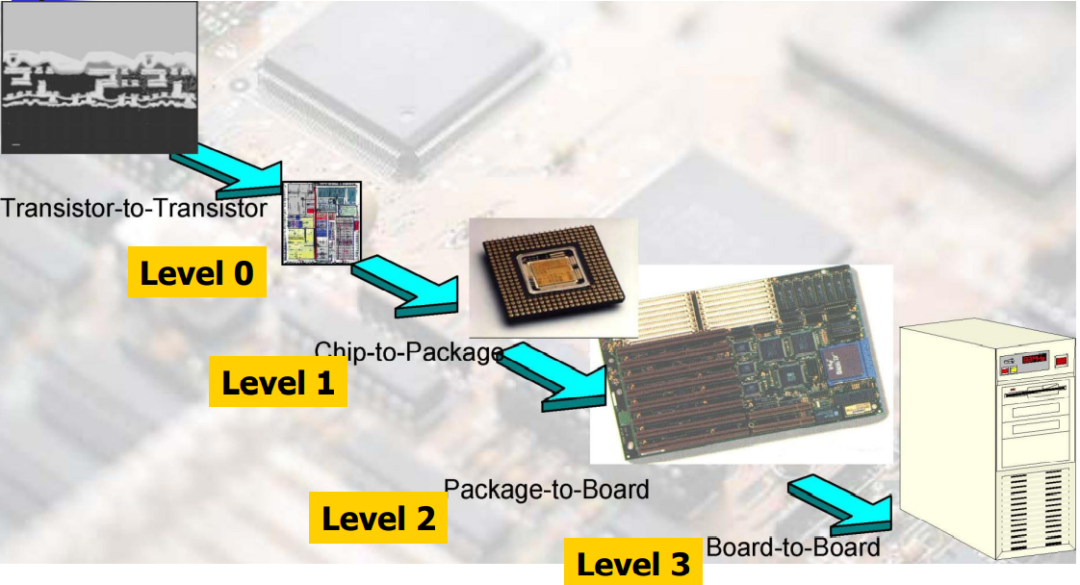

從由硅晶圓制作出來(lái)的各級(jí)芯片開(kāi)始,芯片的封裝可以分為三個(gè)層次,即用封裝外殼將芯片封裝成單芯片組件(Single Chip Module,簡(jiǎn)稱(chēng)SCM)和多芯片組件(MCM)的一級(jí)封裝,也稱(chēng)為片級(jí)封裝;將一級(jí)封裝和其他元器件一同組裝到印刷電路板(PWB)(或其它基板)上的二級(jí)封裝,也稱(chēng)為板級(jí)封裝;以及再將二級(jí)封裝插裝到母板上的三級(jí)封裝,也稱(chēng)為系統(tǒng)級(jí)封裝。

圖 2 芯片封裝分級(jí)(圖片來(lái)源老師課件)

其實(shí),在一、二、三級(jí)封裝與IC芯片之間還有一個(gè)步驟,被稱(chēng)為零級(jí)封裝,其主要作用就是通過(guò)互連技術(shù)將IC芯片焊區(qū)與各級(jí)封裝的焊區(qū)連接起來(lái),也就是讓芯片能夠通過(guò)外殼與外界產(chǎn)生交流,零級(jí)封裝也被稱(chēng)為芯片互連級(jí)。

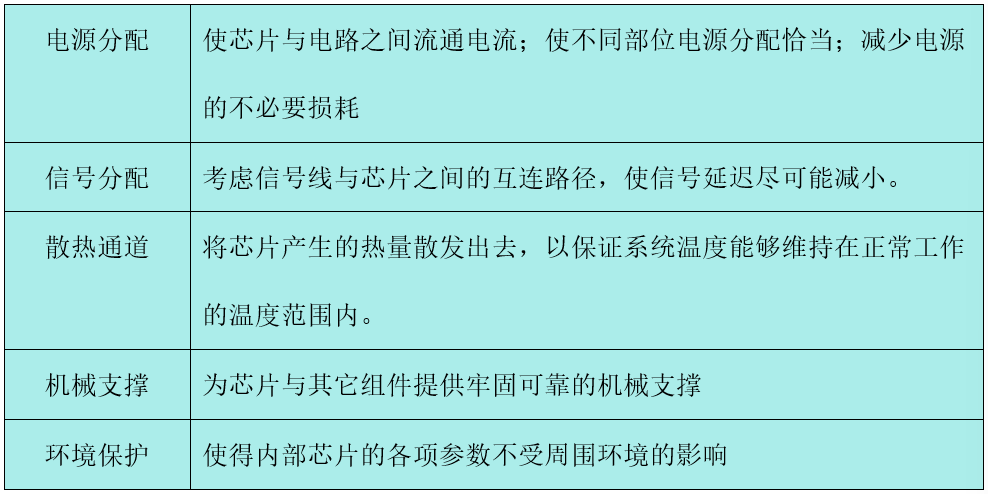

03芯片封裝的功能

表 1 芯片封裝的五大功能

04芯片封裝的幾種技術(shù)

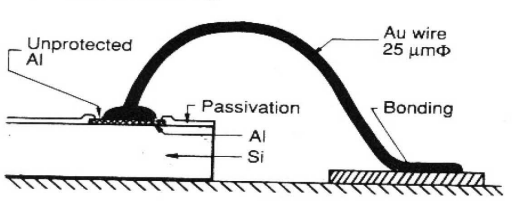

4.1 芯片互連技術(shù)

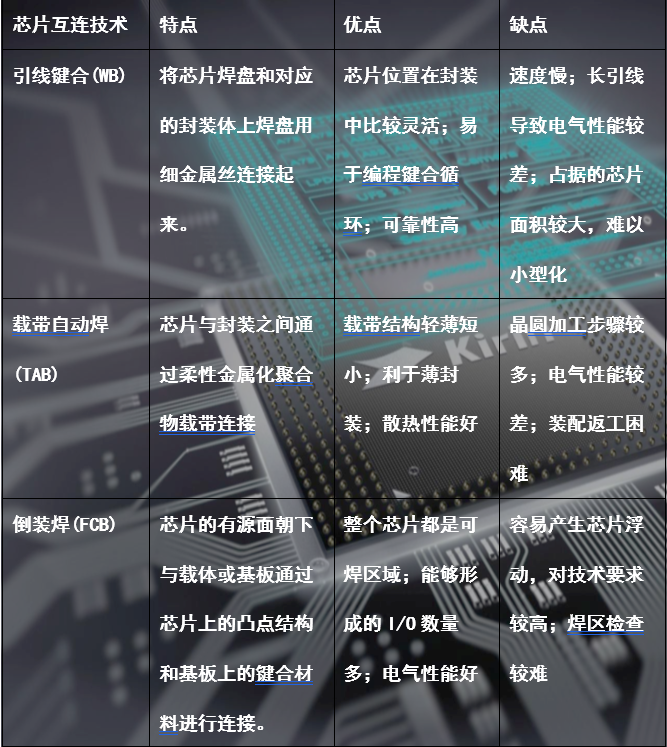

芯片互連技術(shù)來(lái)自與我們上文提到的零級(jí)封裝,這是芯片與封裝外殼以及外界環(huán)境建立聯(lián)系的關(guān)鍵技術(shù)。芯片互連技術(shù)主要有三種:引線(xiàn)鍵合、載帶自動(dòng)焊以及倒裝焊。

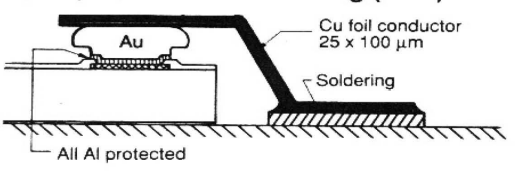

(a) 引線(xiàn)鍵合

(b) 載帶自動(dòng)焊

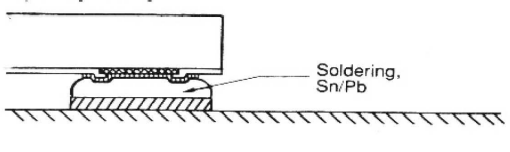

(c) 倒裝焊

表 2 三種芯片互連技術(shù)對(duì)比

4.2 BGA封裝技術(shù)

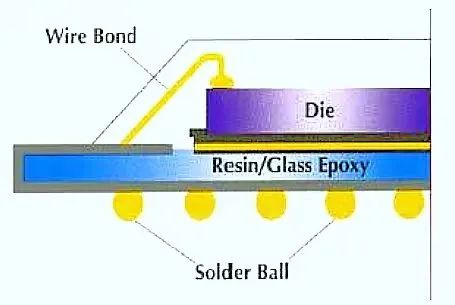

BGA(Ball Grid Array):球柵陣列。它是在基板的下邊按面陣方式引出球形引腳,在基板上面貼裝大規(guī)模集成電路芯片,是大規(guī)模集成電路芯片常用的一種表面貼裝型封裝形式。

優(yōu)點(diǎn):BGA封裝的封裝尺可以做的更小,同時(shí)也更節(jié)省PCB板的布線(xiàn)面積。

缺點(diǎn):電路板的彎曲應(yīng)力導(dǎo)致潛在的可靠性問(wèn)題,BGA封裝更容易受到壓力

4.3 CSP封裝技術(shù)

CSP(Chip Size Package),即芯片尺寸封裝。是指封裝尺寸不超過(guò)裸芯片1.2倍的一種先進(jìn)的封裝形式(美國(guó)JEDEC標(biāo)準(zhǔn))。CSP技術(shù)是在對(duì)現(xiàn)有的芯片封裝技術(shù),其是對(duì)成熟的BGA封裝技術(shù)做進(jìn)一步技術(shù)提升的過(guò)程中,不斷將各種封裝尺寸進(jìn)一步小型化而產(chǎn)生的一種封裝技術(shù)。

優(yōu)點(diǎn):體積小;可容納引腳數(shù)多;電性能良好;散熱性能好

圖 5 CSP結(jié)構(gòu)示意圖(圖片來(lái)源網(wǎng)絡(luò))

05未來(lái)封裝技術(shù)的展望

現(xiàn)在,IC產(chǎn)業(yè)中芯片的封裝與測(cè)試已經(jīng)與IC設(shè)計(jì)和IC制造一起成為了密不可分又相對(duì)獨(dú)立的三大產(chǎn)業(yè),往往設(shè)計(jì)制造出的同一塊芯片卻要采用各種不同的封裝形式與結(jié)構(gòu),在未來(lái)芯片封裝又將如何發(fā)展呢?在這一部分將為大家介紹未來(lái)封裝產(chǎn)業(yè)的發(fā)展趨勢(shì)以及幾種先進(jìn)的可能占據(jù)未來(lái)市場(chǎng)的封裝技術(shù)。

5.1 未來(lái)封裝技術(shù)的幾大趨勢(shì)

(1) 由有封裝向少封裝和無(wú)封裝發(fā)展

(2) 無(wú)源器件走向集成化

(3) 3D封裝技術(shù)

5.2 圓片級(jí)封裝(WLP)技術(shù)

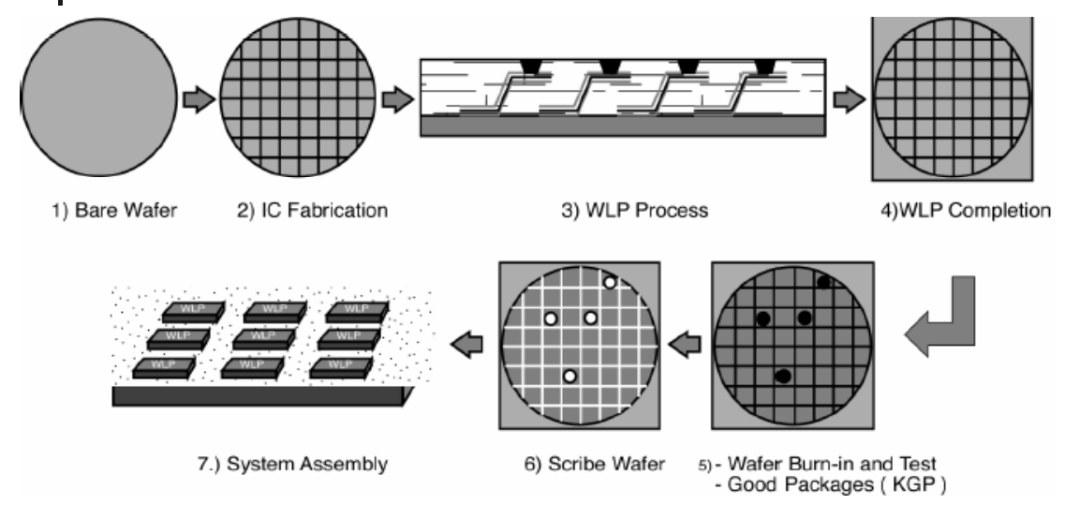

圖 6 WLP技術(shù)流程(圖片來(lái)源老師課件)

WLP是Wafer Level Packaging的縮寫(xiě)。圓片級(jí)封裝, 就是在硅片上依照類(lèi)似半導(dǎo)體前段的工藝, 通過(guò)薄膜、光刻、電鍍、干濕法蝕刻等工藝來(lái)完成封裝和測(cè)試, 最后進(jìn)行切割, 制造出單個(gè)封裝成品。

優(yōu)勢(shì):封裝工藝簡(jiǎn)化以及封裝尺寸小。

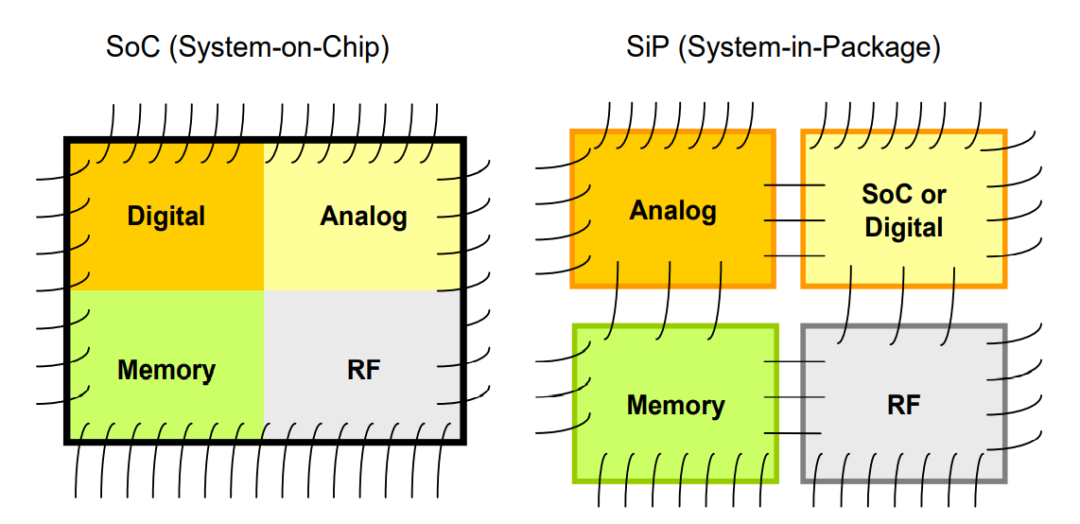

5.3 SOC & SIP

SoC是System on Chip的縮寫(xiě),稱(chēng)為系統(tǒng)級(jí)芯片,也有稱(chēng)片上系統(tǒng),主要就是將一個(gè)系統(tǒng)能夠?qū)崿F(xiàn)其功能需要的各個(gè)模塊集成到一個(gè)芯片上去。這意味著在單個(gè)芯片上,就能完成一個(gè)電子系統(tǒng)的功能。

圖 7 SOC與SIP對(duì)比示意圖(圖片來(lái)源網(wǎng)絡(luò))

SIP是System in a Packaging的縮寫(xiě),只得是將幾個(gè)實(shí)現(xiàn)不同模塊功能的芯片放到一個(gè)封裝中去。

5.4 SOP

圖 8 SOP的地位(圖片自制)

SoP是System-on-package的縮寫(xiě),是被提出來(lái)作為整合系統(tǒng)的概念,希望將數(shù)字、模擬、射頻、微機(jī)電、光學(xué)電路或次系統(tǒng)都整合在封裝上,除了提高系統(tǒng)整合程度外,同時(shí)亦保有可接受的成本效益。SOP的另一個(gè)優(yōu)點(diǎn)是與SOC及SIP兼容,SOC與SIP均可視為SOP的次系統(tǒng),一起被整合在封裝上。

審核編輯:彭菁

-

芯片

+關(guān)注

關(guān)注

456文章

51170瀏覽量

427244 -

集成電路

+關(guān)注

關(guān)注

5392文章

11622瀏覽量

363177 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

553瀏覽量

68037 -

IC封測(cè)

+關(guān)注

關(guān)注

1文章

18瀏覽量

12323

原文標(biāo)題:一文搞懂芯片封裝工藝

文章出處:【微信號(hào):DT-Semiconductor,微信公眾號(hào):DT半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

多芯片整合封測(cè)技術(shù)--多芯片模塊(MCM)的問(wèn)題

多芯片整合封測(cè)技術(shù)--種用先進(jìn)封裝技術(shù)讓系統(tǒng)芯片與內(nèi)存達(dá)到高速傳輸

集成電路封裝技術(shù)專(zhuān)題 通知

芯片封裝技術(shù)介紹

半導(dǎo)體封測(cè)行業(yè)競(jìng)爭(zhēng)情況

貿(mào)易戰(zhàn)浪潮中IC封測(cè)產(chǎn)業(yè)并購(gòu)重組與先進(jìn)封裝技術(shù)發(fā)展方向如何?

淺談芯片封測(cè)及標(biāo)準(zhǔn)芯片封裝工藝

何謂芯片封裝 芯片封裝的幾種技術(shù) 未來(lái)封裝技術(shù)的展望

什么是芯片封測(cè)技術(shù) 芯片設(shè)計(jì)制造封裝測(cè)試全流程

ic封裝測(cè)試是做什么?ic封測(cè)是什么意思?芯片封測(cè)是什么?

什么是芯片封測(cè)?半導(dǎo)體測(cè)試封裝用到什么材料?

封裝和封測(cè)的區(qū)別

芯片封裝IC載板

芯片封測(cè)架構(gòu)和芯片封測(cè)流程

IC封測(cè)中的芯片封裝技術(shù)

IC封測(cè)中的芯片封裝技術(shù)

評(píng)論