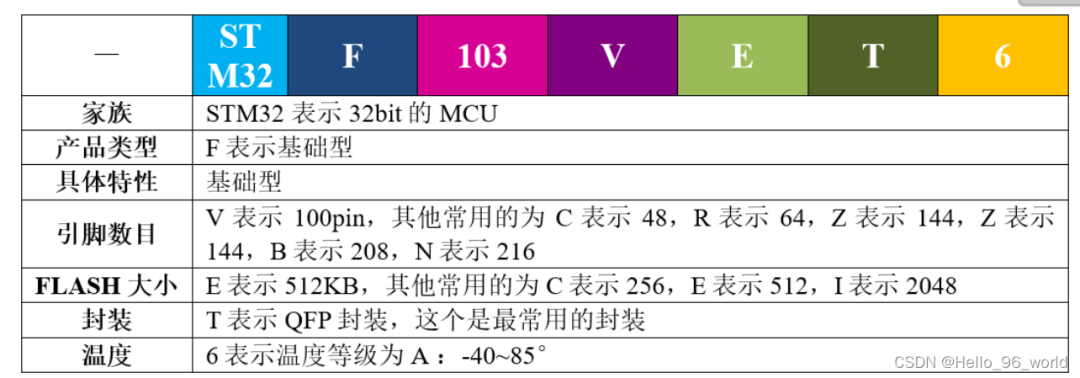

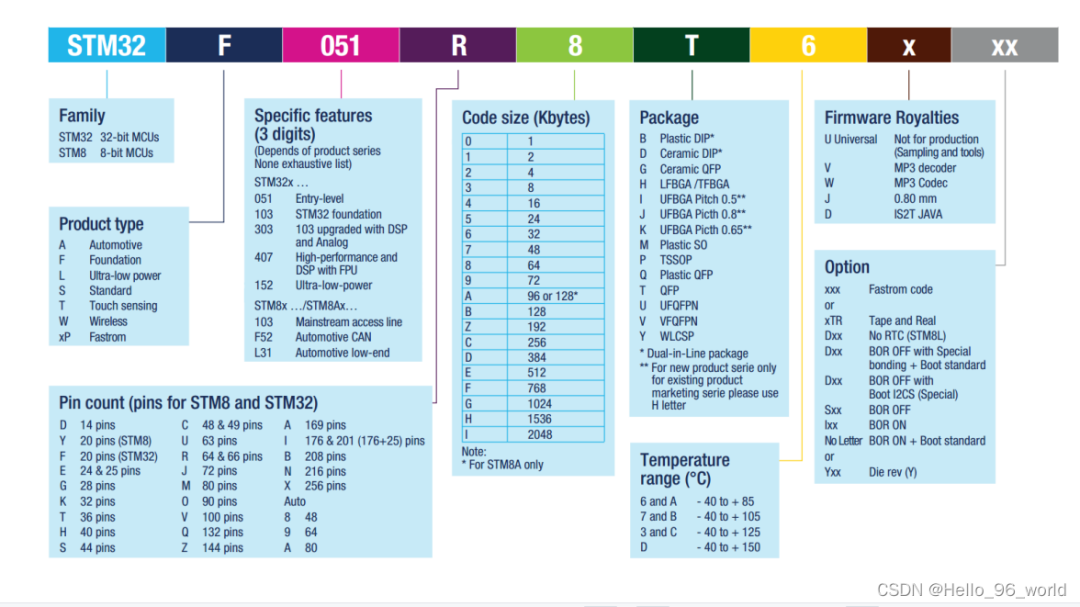

【認(rèn)識(shí)STM32】

?F1 代表了基礎(chǔ)型,基于

?F1 代表了基礎(chǔ)型,基于

Cortex-M3 內(nèi)核,主頻為72MHZ,F(xiàn)4 代表了高性能,基于 Cortex-M4 內(nèi)核,主頻 180M。

【GPIO外設(shè)】

一、GPIO的八種工作模式

1、上拉輸入:IO口在無輸入的情況下,保持高電平。

2、下拉輸入:IO口在無輸入的情況下,保持低電平。

3、浮空輸入:浮空輸入狀態(tài)下,IO的電平狀態(tài)是不確定的,完全由外部輸入決定,如果在該引腳懸空的情況下,讀取該端口的電平是不確定的。

4、模擬輸入:輸入信號(hào)不經(jīng)施密特觸發(fā)器直接接入,輸入信號(hào)為模擬量而非數(shù)字量,其余輸入方式輸入數(shù)字量。

5、推挽輸出:可以輸出高、低電平,連接數(shù)字器件;推挽結(jié)構(gòu)一般是指兩個(gè)三極管分別受兩個(gè)互補(bǔ)信號(hào)的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止。高低電平由IC的電源決定。導(dǎo)通損耗小、效率高。輸出既可以向負(fù)載灌電流,也可以從負(fù)載抽取電流。推拉式輸出級(jí)既提高電路的負(fù)載能力,又提高開關(guān)速度。

6、開漏輸出:輸出端相當(dāng)于三極管的集電極,要得到高電平狀態(tài)需要上拉電阻才行。適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20mA以內(nèi))。開漏形式的電路有以下幾個(gè)特點(diǎn):

(1)利用外部電路的驅(qū)動(dòng)能力,減少IC內(nèi)部的驅(qū)動(dòng)。當(dāng)IC內(nèi)部MOSFET導(dǎo)通時(shí),驅(qū)動(dòng)電流是從外部的VCC流經(jīng)上拉電阻、MOSFET到GND。IC內(nèi)部僅需很小的柵極驅(qū)動(dòng)電流。

(2)一般來說,開漏是用來連接不同電平的器件,匹配電平用的,因?yàn)殚_漏引腳不連接外部的上拉電阻時(shí),只能輸出低電平,如果需要同時(shí)具備輸出高電平的功能,則需要接上拉電阻,很好的一個(gè)優(yōu)點(diǎn)是通過改變上拉電源的電壓,便可以改變傳輸電平。比如加上上拉電阻就可以提供TTL/CMOS電平輸出等。(上拉電阻的阻值決定了邏輯電平轉(zhuǎn)換的速度。阻值越大,速度越低功耗越小,所以負(fù)載電阻的選擇要兼顧功耗和速度。)

(3)開漏輸出提供了靈活的輸出方式,但是也有其弱點(diǎn),就是帶來上升沿的延時(shí)。因?yàn)樯仙厥峭ㄟ^外接上拉無源電阻對(duì)負(fù)載充電,所以當(dāng)電阻選擇小時(shí)延時(shí)就小,但功耗大;反之延時(shí)大功耗小。所以如果對(duì)延時(shí)有要求,則建議用下降沿輸出。

(4)可以將多個(gè)開漏輸出連接到一條線上。通過一只上拉電阻,在不增加任何器件的情況下,形成“與邏輯”關(guān)系,即“線與”。可以簡單的理解為:在所有引腳連在一起時(shí),外接一上拉電阻,如果有一個(gè)引腳輸出為邏輯0,相當(dāng)于接地,與之并聯(lián)的回路“相當(dāng)于被一根導(dǎo)線短路”,所以外電路邏輯電平便為0,只有都為高電平時(shí),與的結(jié)果才為邏輯1。

7、復(fù)用推挽輸出:此時(shí)IO受內(nèi)部外設(shè)控制,比如定時(shí)器的PWM,比如SPI的MOSI,MISO等。而普通的推挽輸出,則IO受ODR控制。

8、復(fù)用開漏輸出:參考復(fù)用推挽。

二、總結(jié)在STM32中選用IO模式

1、浮空輸入GPIO_IN_FLOATING ——浮空輸入,可以做KEY識(shí)別,RX1。

2、帶上拉輸入GPIO_IPU——IO內(nèi)部上拉電阻輸入。

3、帶下拉輸入GPIO_IPD—— IO內(nèi)部下拉電阻輸入。

4、模擬輸入GPIO_AIN ——應(yīng)用ADC模擬輸入,或者低功耗下省電。

5、開漏輸出GPIO_OUT_OD ——IO輸出0接GND,IO輸出1,懸空,需要外接上拉電阻,才能實(shí)現(xiàn)輸出高電平。當(dāng)輸出為1時(shí),IO口的狀態(tài)由上拉電阻拉高電平,但由于是開漏輸出模式,這樣IO口也就可以由外部電路改變?yōu)榈碗娖交虿蛔儭?梢宰xIO輸入電平變化,實(shí)現(xiàn)C51的IO雙向功能。

6、推挽輸出GPIO_OUT_PP ——IO輸出0-接GND, IO輸出1 -接VCC,讀輸入值是未知的。

7、復(fù)用功能的推挽輸出GPIO_AF_PP ——片內(nèi)外設(shè)功能(I2C的SCL,SDA)。

8、復(fù)用功能的開漏輸出GPIO_AF_OD——片內(nèi)外設(shè)功能(TX1,MOSI,MISO.SCK.SS)。

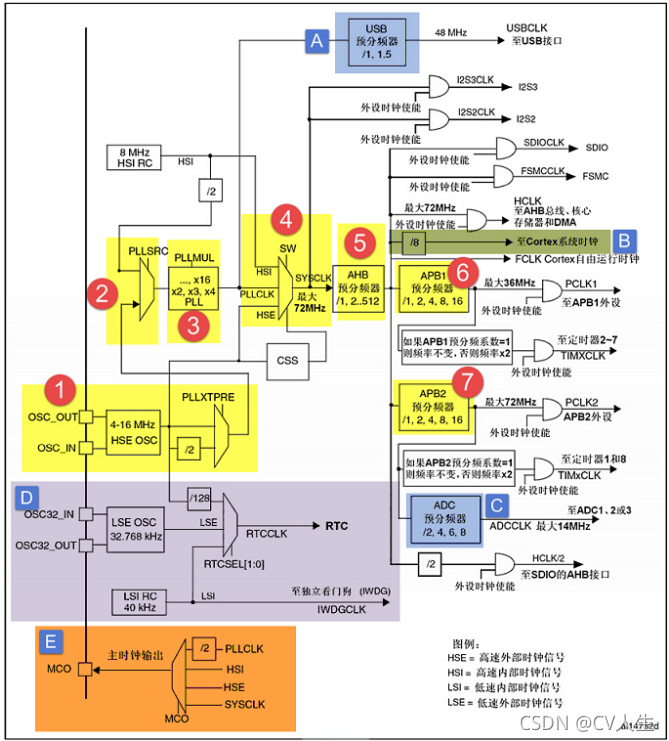

【RCC時(shí)鐘】

RCC時(shí)鐘的主要作用:設(shè)置系統(tǒng)時(shí)鐘 SYSCLK 、設(shè)置 AHB 分頻因子(決定 HCLK 等于多少)、設(shè)置 APB2 分頻因子(決定 PCLK2 等于多少)、設(shè)置 APB1 分頻因子(決定 PCLK1 等于多少)、設(shè)置各個(gè)外設(shè)的分頻因子;控制 AHB 、 APB2 和 APB1 這三條總線時(shí)鐘的開啟、控制每個(gè)外設(shè)的時(shí)鐘的開啟。對(duì)于 SYSCLK、HCLK、PCLK2、PCLK1 這四個(gè)時(shí)鐘的配置一般是:PCLK2 = HCLK = SYSCLK=PLLCLK = 72M, PCLK1=HCLK/2 = 36M。(以stm32f103vet6為例)

使用HSE時(shí),設(shè)置系統(tǒng)時(shí)鐘的步驟

* 1、開啟HSE ,并等待 HSE 穩(wěn)定

* 2、設(shè)置 AHB、APB2、APB1的預(yù)分頻因子

* 3、設(shè)置PLL的時(shí)鐘來源,和PLL的倍頻因子,設(shè)置各種頻率主要就是在這里設(shè)置

* 4、開啟PLL,并等待PLL穩(wěn)定

* 5、把PLLCK切換為系統(tǒng)時(shí)鐘SYSCLK

* 6、讀取時(shí)鐘切換狀態(tài)位,確保PLLCLK被選為系統(tǒng)時(shí)鐘

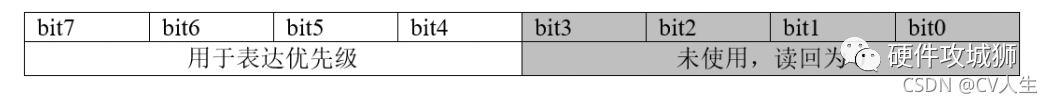

【NVIC是嵌套向量中斷控制器】

一、優(yōu)先級(jí)定義

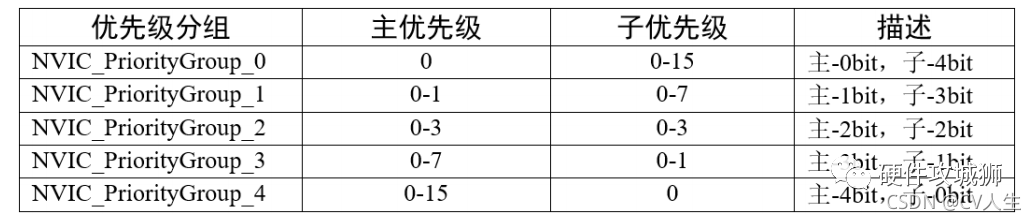

在 NVIC 有一個(gè)專門的寄存器:中斷優(yōu)先級(jí)寄存器 NVIC_IPRx,用來配置外部中斷的優(yōu)先級(jí),IPR 寬度為 8bit,原則上每個(gè)外部中斷可配置的優(yōu)先級(jí)為 0~255,數(shù)值越小,優(yōu)先級(jí)越高。但是絕大多數(shù) CM3 芯片都會(huì)精簡設(shè)計(jì),以致實(shí)際上支持的優(yōu)先級(jí)數(shù)減少,在 F103 中,只使用了高 4bit,用于表達(dá)優(yōu)先級(jí)的這 4bit,又被分組成搶占優(yōu)先級(jí)和子優(yōu)先級(jí)。如果有多個(gè)中斷同時(shí)響應(yīng),搶占 優(yōu)先級(jí)高的就會(huì)搶占搶占優(yōu)先級(jí)低的優(yōu)先得到執(zhí)行,如果搶占優(yōu)先級(jí)相同,就比較子優(yōu)先級(jí)。如果搶占優(yōu)先級(jí)和子優(yōu)先級(jí)都相同的話,就比較他們的硬件中斷編號(hào),編號(hào)越小,優(yōu)先級(jí)越高。

二、優(yōu)先級(jí)分組

優(yōu)先級(jí)的分組由內(nèi)核外設(shè) SCB 的應(yīng)用程序中斷及復(fù)位控制寄存器 AIRCR 的 PRIGROUP[10:8] 位 決定,F(xiàn)103 分為了 5 組,具體如下:主優(yōu)先級(jí) = 搶占優(yōu)先級(jí)。

【EXTI外部中斷/事件控制器】

EXTI(External interrupt/event controller)—外部中斷/事件控制器,管理了控制器的 20 個(gè)中斷/事 件線。每個(gè)中斷/事件線都對(duì)應(yīng)有一個(gè)邊沿檢測器,可以實(shí)現(xiàn)輸入信號(hào)的上升沿檢測和下降沿的檢測。EXTI 可以實(shí)現(xiàn)對(duì)每個(gè)中斷/事件線進(jìn)行單獨(dú)配置,可以單獨(dú)配置為中斷或者事件,以及觸 發(fā)事件的屬性。

【SysTick系統(tǒng)定時(shí)器】

SysTick—系統(tǒng)定時(shí)器是屬于 CM3 內(nèi)核中的一個(gè)外設(shè),內(nèi)嵌在 NVIC 中。系統(tǒng)定時(shí)器是一個(gè) 24bit 的向下遞減的計(jì)數(shù)器,計(jì)數(shù)器每計(jì)數(shù)一次的時(shí)間為 1/SYSCLK,一般我們?cè)O(shè)置系統(tǒng)時(shí)鐘 SYSCLK 等于 72M。當(dāng)重裝載數(shù)值寄存器的值遞減到 0 的時(shí)候,系統(tǒng)定時(shí)器就產(chǎn)生一次中斷,以此循環(huán)往 復(fù)。

【通訊的基本概念】

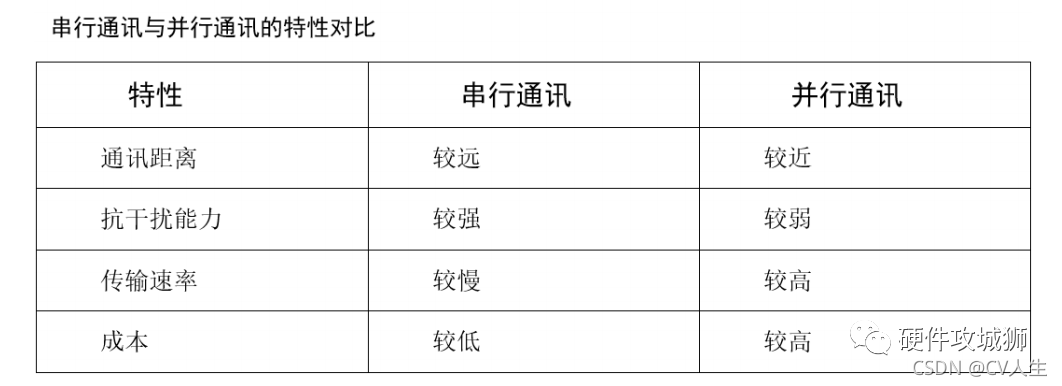

一、串行通訊與并行通訊

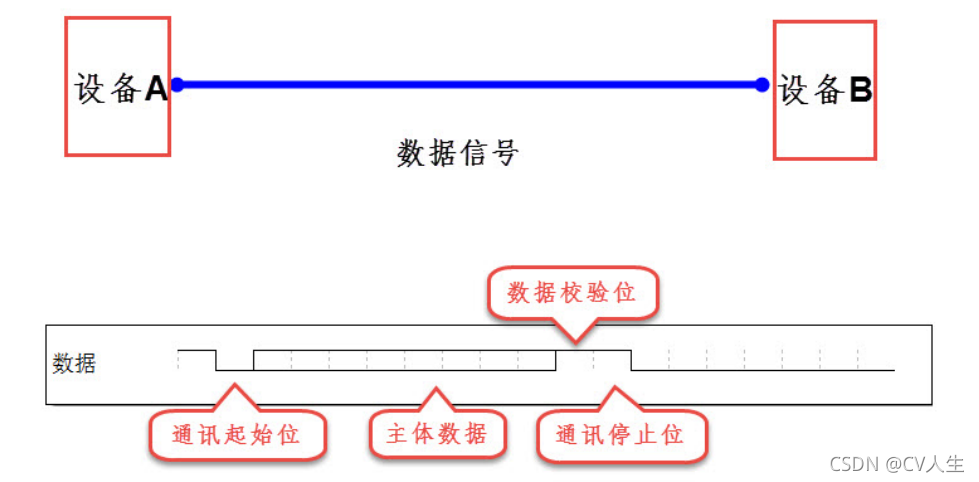

按數(shù)據(jù)傳送的方式,通訊可分為串行通訊與并行通訊,串行通訊是指設(shè)備之間通過少量數(shù)據(jù)信號(hào)線 (一般是 8 根以下),地線以及控制信號(hào)線,按數(shù)據(jù)位形式一位一位地傳輸數(shù)據(jù)的通訊方式。而并行通訊一般是指使用 8、16、32 及 64 根或更多的數(shù)據(jù)線進(jìn)行傳輸?shù)耐ㄓ嵎绞健?/p>

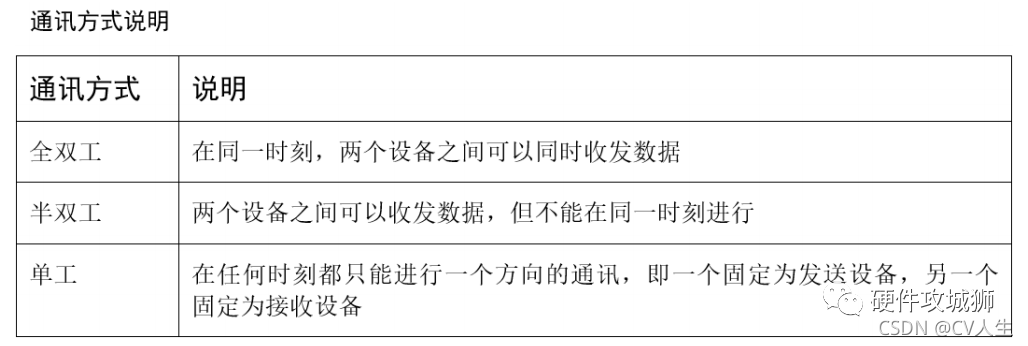

二、全雙工、半雙工及單工通訊

根據(jù)數(shù)據(jù)通訊的方向,通訊又分為全雙工、半雙工及單工通訊,它們主要以信道的方向來區(qū)。

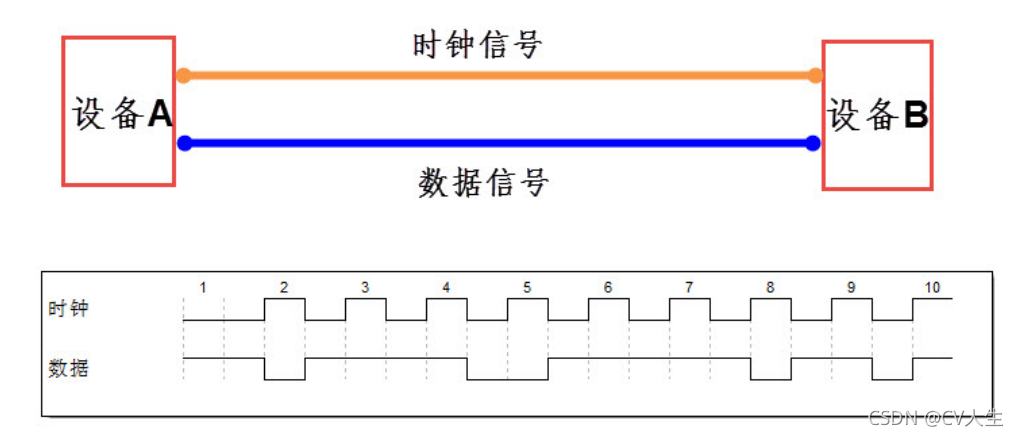

三、同步通訊與異步通訊

根據(jù)通訊的數(shù)據(jù)同步方式,又分為同步和異步兩種,可以根據(jù)通訊過程中是否有使用到時(shí)鐘信號(hào)。

在同步通訊中,收發(fā)設(shè)備雙方會(huì)使用一根信號(hào)線表示時(shí)鐘信號(hào),在時(shí)鐘信號(hào)的驅(qū)動(dòng)下雙方進(jìn)行協(xié) 調(diào),同步數(shù)據(jù),見圖同步通訊 。通訊中通常雙方會(huì)統(tǒng)一規(guī)定在時(shí)鐘信號(hào)的上升沿或下降沿對(duì)數(shù) 據(jù)線進(jìn)行采樣。

在異步通訊中不使用時(shí)鐘信號(hào)進(jìn)行數(shù)據(jù)同步,它們直接在數(shù)據(jù)信號(hào)中穿插一些同步用的信號(hào)位, 或者把主體數(shù)據(jù)進(jìn)行打包,以數(shù)據(jù)幀的格式傳輸數(shù)據(jù),見圖某種異步通訊 ,某些通訊中還需要雙方約定數(shù)據(jù)的傳輸速率,以便更好地同步。

在同步通訊中,數(shù)據(jù)信號(hào)所傳輸?shù)膬?nèi)容絕大部分就是有效數(shù)據(jù),而異步通訊中會(huì)包含有幀的各種標(biāo)識(shí)符,所以同步通訊的效率更高,但是同步通訊雙方的時(shí)鐘允許誤差較小,而異步通訊雙方的時(shí)鐘允許誤差較大。

四、通訊速率

衡量通訊性能的一個(gè)非常重要的參數(shù)就是通訊速率,通常以比特率 (Bitrate) 來表示,即每秒鐘傳輸?shù)亩M(jìn)制位數(shù),單位為比特每秒 (bit/s)。容易與比特率混淆的概念是“波特率”(Baudrate),它表示每秒鐘傳輸了多少個(gè)碼元。通訊中常用時(shí)間間隔相同的符號(hào)來表示一個(gè)二進(jìn)制數(shù)字,這樣的信號(hào)稱為碼元。

例:常見的通訊傳輸中,用 0V 表示數(shù)字 0,5V 表示數(shù)字 1,那么一個(gè)碼元可以表示兩種狀態(tài) 0 和 1,所以一個(gè)碼元等于一個(gè)二進(jìn)制比特位,此時(shí)波特率的大小與比特率一致;如果在通訊傳輸中,有 0V、2V、4V 以及 6V 分別表示二進(jìn)制數(shù) 00、01、10、11,那么每個(gè)碼元可以表示四種狀態(tài),即兩個(gè)二進(jìn)制比特位,所以碼元數(shù)是二進(jìn)制比特位數(shù)的一半,這個(gè)時(shí)候的波特率為比特率的一半。因?yàn)楹芏喑R姷耐ㄓ嵵幸粋€(gè)碼元都是表示兩種狀態(tài),人們常常直接以波特率來表示比特率。

【串口通訊】

一、物理層:

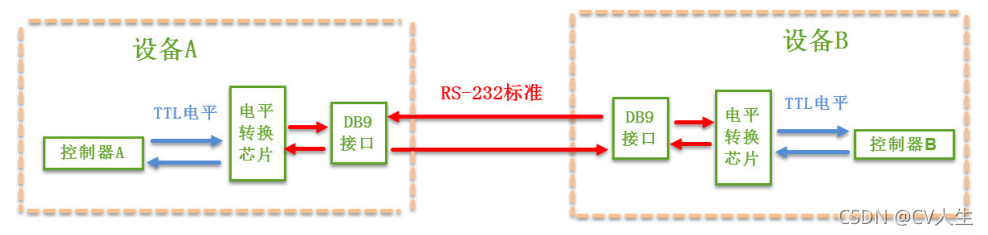

串口通訊的物理層有很多標(biāo)準(zhǔn)及變種,我們主要講解 RS-232 標(biāo)準(zhǔn)。

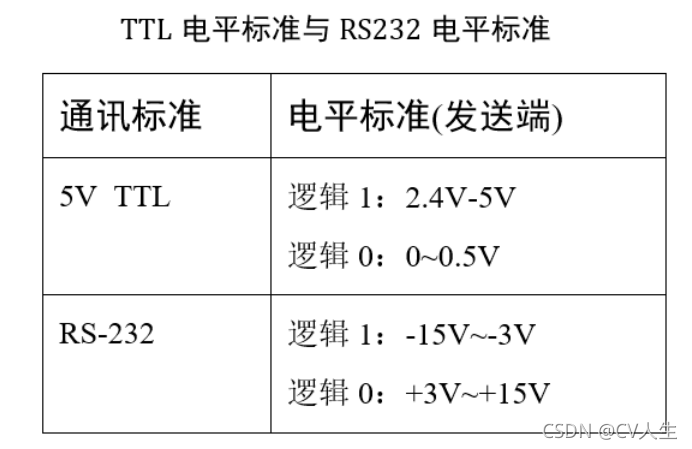

根據(jù)通訊使用的電平標(biāo)準(zhǔn)不同,串口通訊可分為 TTL 標(biāo)準(zhǔn)及 RS-232 標(biāo)準(zhǔn)。

TTL 的電平標(biāo)準(zhǔn),理想狀態(tài)下,使用 5V 表示二進(jìn)制邏輯 1,使用 0V 表示邏輯 0;而為了增加串口通訊的遠(yuǎn)距離傳輸及抗干擾能力,它使用-15V 表示邏輯 1,+15V 表示邏輯 0,即RS232。

因?yàn)榭刂破饕话闶褂?TTL 電平標(biāo)準(zhǔn),所以常常會(huì)使用 MA3232 芯片對(duì) TTL 及 RS-232 電平的信號(hào)進(jìn)行互相轉(zhuǎn)換。

在目前的其它工業(yè)控制使用的串口通訊中,一般只使用 RXD、TXD 以及 GND 三條信號(hào)線,直接傳輸數(shù)據(jù)信號(hào),而 RTS、CTS、DSR、DTR 及 DCD 信號(hào)都被裁剪掉了。

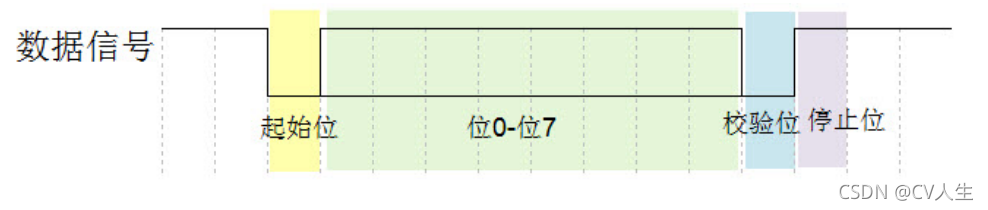

二、協(xié)議層

串口通訊的數(shù)據(jù)包由發(fā)送設(shè)備通過自身的 TXD 接口傳輸?shù)浇邮赵O(shè)備的 RXD 接口。在串口通訊的協(xié)議層中,規(guī)定了數(shù)據(jù)包的內(nèi)容,它由啟始位、主體數(shù)據(jù)、校驗(yàn)位以及停止位組成,通訊雙方的數(shù)據(jù)包格式要約定一致才能正常收發(fā)數(shù)據(jù)。

波特率:串口異步通訊,異步通訊中由于沒有時(shí)鐘信號(hào) (如前面講解的 DB9 接口中是 沒有時(shí)鐘信號(hào)的),所以兩個(gè)通訊設(shè)備之間需要約定好波特率,即每個(gè)碼元的長度,以便對(duì)信號(hào) 進(jìn)行解碼,圖串口數(shù)據(jù)包的基本組成 中用虛線分開的每一格就是代表一個(gè)碼元。常見的波特率為 4800、9600,115200 等。

通訊的起始和停止信號(hào):串口通訊的一個(gè)數(shù)據(jù)包從起始信號(hào)開始,直到停止信號(hào)結(jié)束。數(shù)據(jù)包的起始信號(hào)由一個(gè)邏輯 0 的數(shù)據(jù)位表示,而數(shù)據(jù)包的停止信號(hào)可由 0.5、1、1.5 或 2 個(gè)邏輯 1 的數(shù)據(jù)位表示。

有效數(shù)據(jù):在數(shù)據(jù)包的起始位之后緊接著的就是要傳輸?shù)闹黧w數(shù)據(jù)內(nèi)容,也稱為有效數(shù)據(jù),有效數(shù)據(jù)的長度常被約定為 5、6、7 或 8 位長。

數(shù)據(jù)校驗(yàn):在有效數(shù)據(jù)之后,有一個(gè)可選的數(shù)據(jù)校驗(yàn)位。由于數(shù)據(jù)通信相對(duì)更容易受到外部干擾導(dǎo)致傳輸數(shù)據(jù)出現(xiàn)偏差,可以在傳輸過程加上校驗(yàn)位來解決這個(gè)問題。校驗(yàn)方法有奇校驗(yàn) (odd)、偶校驗(yàn) (even)、0 校驗(yàn) (space)、1 校驗(yàn) (mark) 以及無校驗(yàn) (noparity)。

【I2C】

I2C 通訊協(xié)議 (Inter - Integrated Circuit) 是由 Phiilps 公司開發(fā)的,由于它引腳少,硬件實(shí)現(xiàn)簡單, 可擴(kuò)展性強(qiáng),不需要 USART、CAN 等通訊協(xié)議的外部收發(fā)設(shè)備。

一、物理層

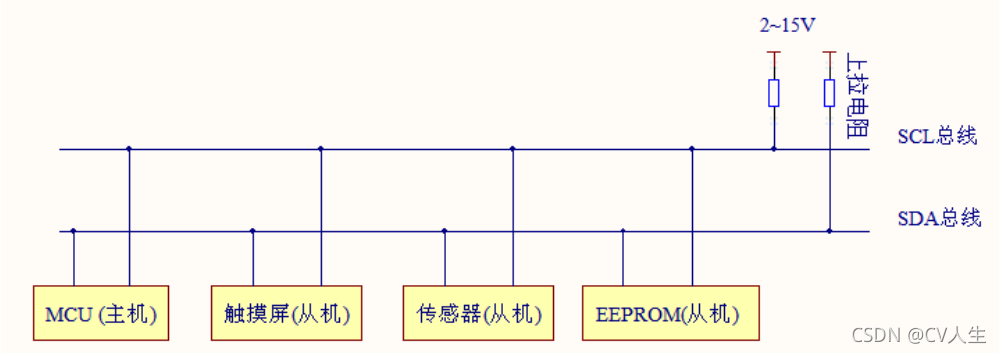

1、I2C 通訊設(shè)備之間的常用連接方式:

它的物理層有如下特點(diǎn):

(1) 它是一個(gè)支持設(shè)備的總線。“總線”指多個(gè)設(shè)備共用的信號(hào)線。在一個(gè) I2C 通訊總線中,可連接多個(gè) I2C 通訊設(shè)備,支持多個(gè)通訊主機(jī)及多個(gè)通訊從機(jī)。

(2) 一個(gè) I2C 總線只使用兩條總線線路,一條雙向串行數(shù)據(jù)線 (SDA) ,一條串行時(shí)鐘線 (SCL)。數(shù) 據(jù)線即用來表示數(shù)據(jù),時(shí)鐘線用于數(shù)據(jù)收發(fā)同步。

(3) 每個(gè)連接到總線的設(shè)備都有一個(gè)獨(dú)立的地址,主機(jī)可以利用這個(gè)地址進(jìn)行不同設(shè)備之間的訪問。

(4) 總線通過上拉電阻接到電源。當(dāng) I2C 設(shè)備空閑時(shí),會(huì)輸出高阻態(tài),而當(dāng)所有設(shè)備都空閑,都 輸出高阻態(tài)時(shí),由上拉電阻把總線拉成高電平。

(5) 多個(gè)主機(jī)同時(shí)使用總線時(shí),為了防止數(shù)據(jù)沖突,會(huì)利用仲裁方式?jīng)Q定由哪個(gè)設(shè)備占用總線。

(6) 具有三種傳輸模式:標(biāo)準(zhǔn)模式傳輸速率為 100kbit/s ,快速模式為 400kbit/s ,高速模式下可達(dá) 3.4Mbit/s,但目前大多 I2C 設(shè)備尚不支持高速模式。

(7) 連接到相同總線的 IC 數(shù)量受到總線的最大電容 400pF 限制。

二、協(xié)議層

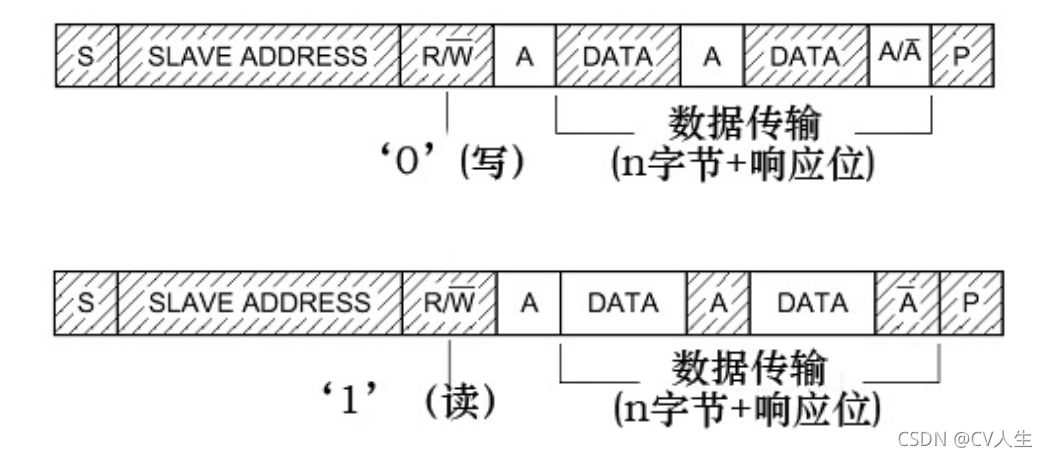

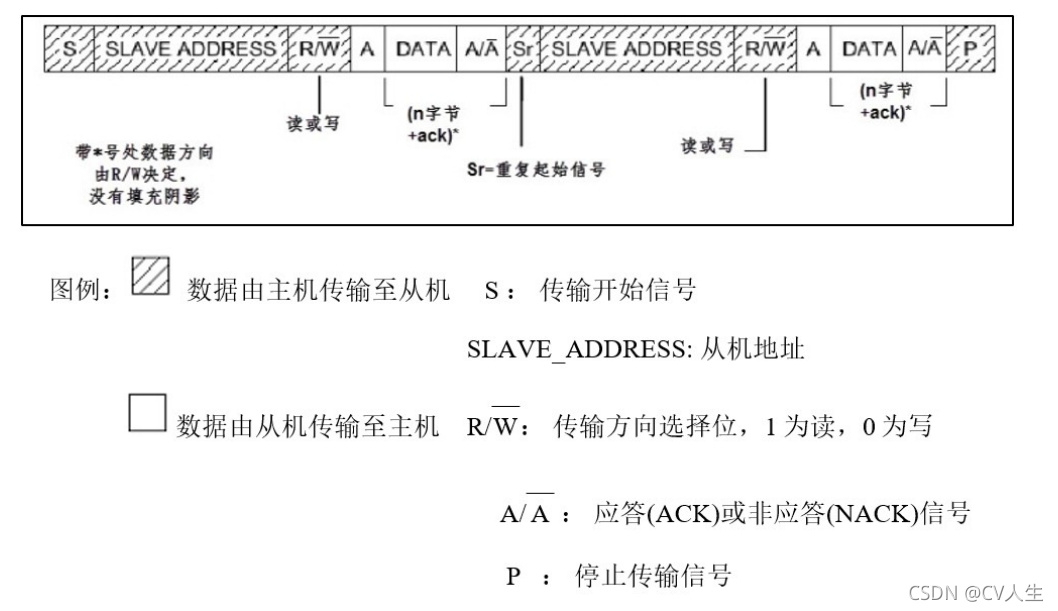

1、I2C 基本讀寫過程

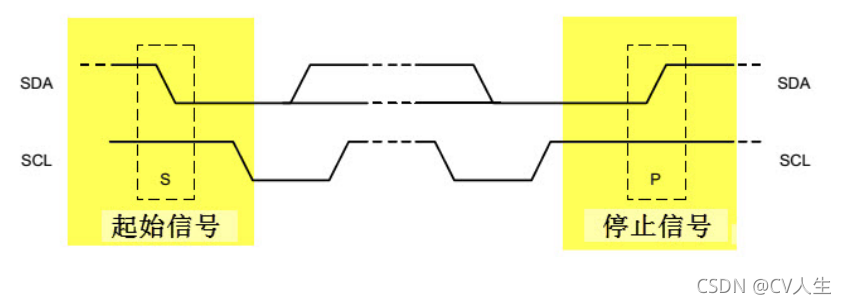

2、通訊的起始和停止信號(hào)

當(dāng) SCL 線是高電平時(shí) SDA 線從高電平向低電平切換,這個(gè)情況表示通訊的起始。當(dāng) SCL 是高電平時(shí) SDA 線由低電平向高電平切換,表示通訊的停止。起始和停止信號(hào)一般由主機(jī)產(chǎn)生。

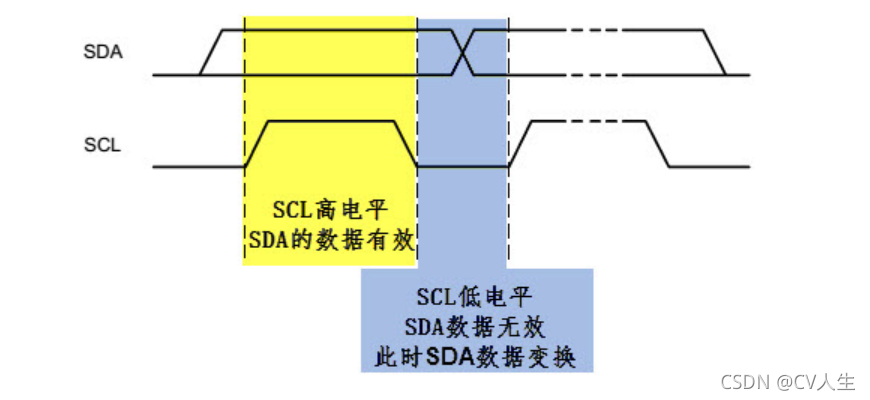

2、 數(shù)據(jù)有效性

SDA 數(shù)據(jù)線在 SCL 的每個(gè)時(shí)鐘周期傳輸一位數(shù)據(jù)。傳輸時(shí),SCL 為高電平的時(shí)候 SDA 表示的數(shù)據(jù)有效,即此時(shí)的 SDA 為高電平時(shí)表示數(shù)據(jù)“1”,為低電平時(shí)表示數(shù)據(jù)“0”。當(dāng) SCL 為低電平時(shí),SDA的數(shù)據(jù)無效,一般在這個(gè)時(shí)候 SDA 進(jìn)行電平切換,為下一次表示數(shù)據(jù)做好準(zhǔn)備。

每次數(shù)據(jù)傳輸都以字節(jié)為單位,每次傳輸?shù)淖止?jié)數(shù)不受限制。

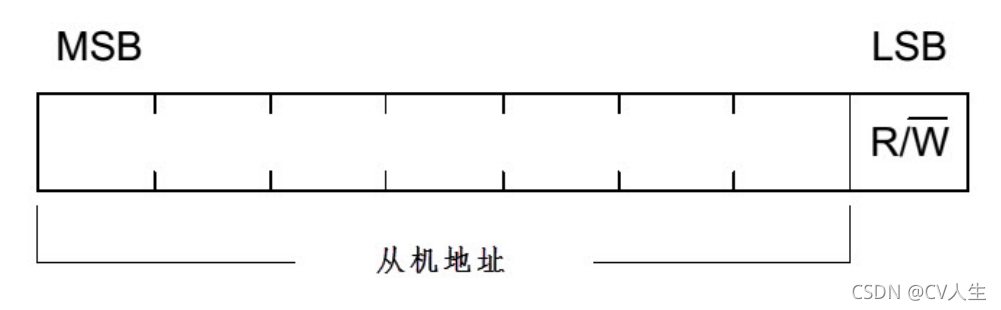

3、地址及數(shù)據(jù)方向

I2C 協(xié)議規(guī)定設(shè)備地址可以是 7 位或 10 位,實(shí)際中 7 位的地址應(yīng)用比較廣泛。緊跟設(shè)備地址的一個(gè)數(shù)據(jù)位用來表示數(shù)據(jù)傳輸方向,它是數(shù)據(jù)方向位 (R/),第 8 位或第 11 位。數(shù)據(jù)方向位為“1”時(shí)表示主機(jī)由從機(jī)讀數(shù)據(jù),該位為“0”時(shí)表示主機(jī)向從機(jī)寫數(shù)據(jù)。

讀數(shù)據(jù)方向時(shí),主機(jī)會(huì)釋放對(duì) SDA 信號(hào)線的控制,由從機(jī)控制 SDA 信號(hào)線,主機(jī)接收信號(hào),寫 數(shù)據(jù)方向時(shí),SDA 由主機(jī)控制,從機(jī)接收信號(hào)。

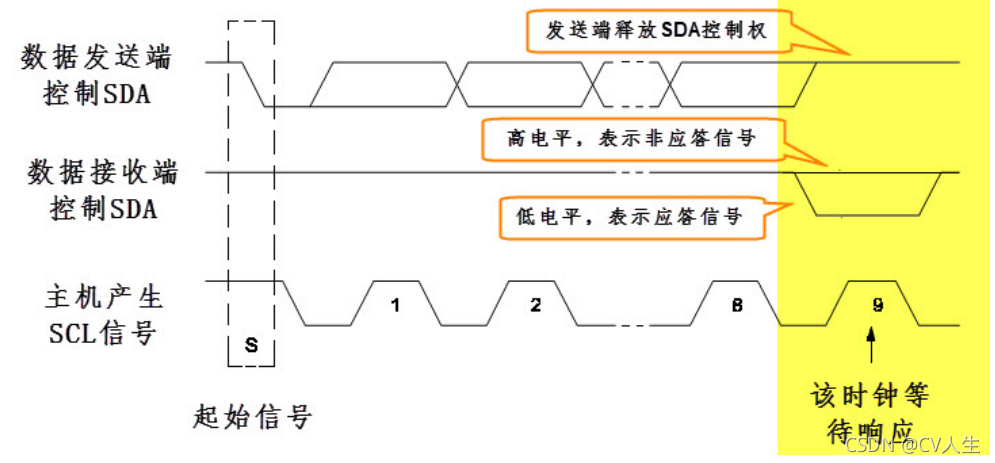

4、響應(yīng)

作為數(shù)據(jù)接收端時(shí),當(dāng)設(shè)備 (無論主從機(jī)) 接收到 I2C 傳輸?shù)囊粋€(gè)字節(jié)數(shù)據(jù)或地址后,若希望對(duì)方繼續(xù)發(fā)送數(shù)據(jù),則需要向?qū)Ψ桨l(fā)送“應(yīng)答 (ACK)”信號(hào),發(fā)送方會(huì)繼續(xù)發(fā)送下一個(gè)數(shù)據(jù);若接收端 希望結(jié)束數(shù)據(jù)傳輸,則向?qū)Ψ桨l(fā)送“非應(yīng)答 (NACK)”信號(hào),發(fā)送方接收到該信號(hào)后會(huì)產(chǎn)生一個(gè) 停止信號(hào),結(jié)束信號(hào)傳輸。

傳輸時(shí)主機(jī)產(chǎn)生時(shí)鐘,在第 9 個(gè)時(shí)鐘時(shí),數(shù)據(jù)發(fā)送端會(huì)釋放 SDA 的控制權(quán),由數(shù)據(jù)接收端控制 SDA,若 SDA 為高電平,表示非應(yīng)答信號(hào) (NACK),低電平表示應(yīng)答信號(hào) (ACK)。

【SPI】

SPI 協(xié)議是由摩托羅拉公司提出的通訊協(xié)議 (Serial Peripheral Interface),即串行外圍設(shè)備接口,是 一種高速全雙工的通信總線。它被廣泛地使用在 ADC、LCD 等設(shè)備與 MCU 間,要求通訊速率 較高的場合。

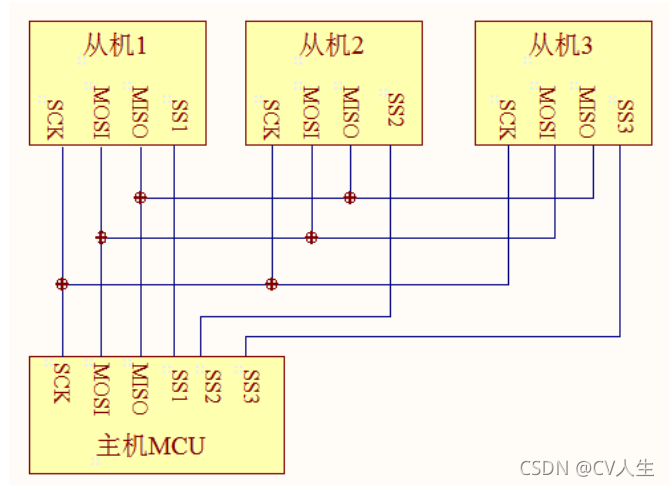

一、SPI物理層

SPI 通訊設(shè)備之間的常用連接方式:SPI 通訊使用 3 條總線及片選線,3 條總線分別為 SCK、MOSI、MISO,片選線NSS。(SPI 通訊以 NSS 線置低電平為開始信號(hào),以 NSS 線被拉高作為結(jié)束信號(hào))

二、協(xié)議層

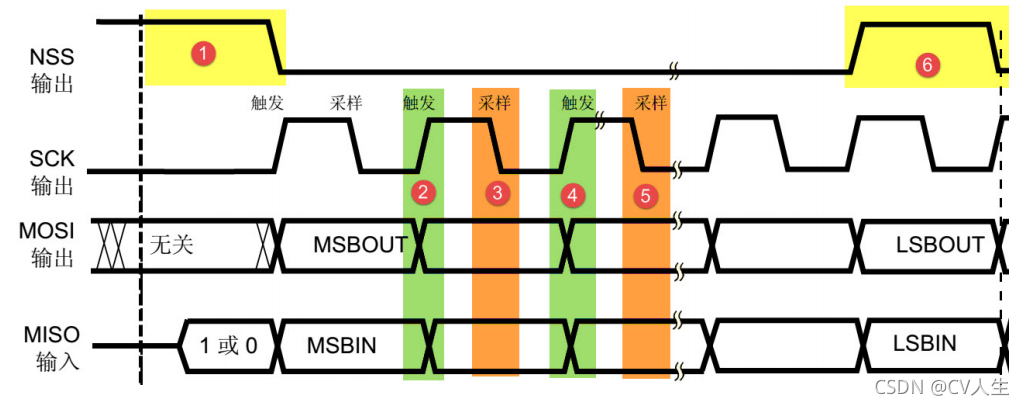

1、SPI 通訊的通訊時(shí)序

2、通訊的起始和停止信號(hào)

NSS 信號(hào)線由高變低,是 SPI 通訊的起始信號(hào)。NSS 是每個(gè)從機(jī)各自獨(dú)占的信號(hào)線,當(dāng)從機(jī)在自己的 NSS 線檢測到起始信號(hào)后,就知道自己被主機(jī)選中了,開始準(zhǔn)備與主機(jī)通訊。NSS 信號(hào)由低變高,是 SPI 通訊的停止信號(hào),表示本次通訊結(jié)束,從機(jī)的選中狀態(tài)被取消。

3、數(shù)據(jù)有效性

MOSI 及 MISO 的數(shù)據(jù)在 SCK 的上升沿期間變化輸出,在 SCK 的下降沿時(shí)被采樣。即在 SCK 的下降沿時(shí)刻,MOSI 及 MISO 的數(shù)據(jù)有效,高電平時(shí)表示數(shù)據(jù)“1”,為低電平時(shí)表示數(shù)據(jù)“0”。在其它時(shí)刻,數(shù)據(jù)無效,MOSI 及 MISO 為下一次表示數(shù)據(jù)做準(zhǔn)備。

SPI 每次數(shù)據(jù)傳輸可以 8 位或 16 位為單位,每次傳輸?shù)膯挝粩?shù)不受限制。

數(shù)據(jù)傳輸時(shí),MSB先行或 LSB 先行并沒有作硬性規(guī)定,但要保證兩個(gè) SPI 通訊設(shè)備之間使用同樣的協(xié)定,一般都會(huì)采用圖 SPI 通訊時(shí)序 中的 MSB 先行模式。

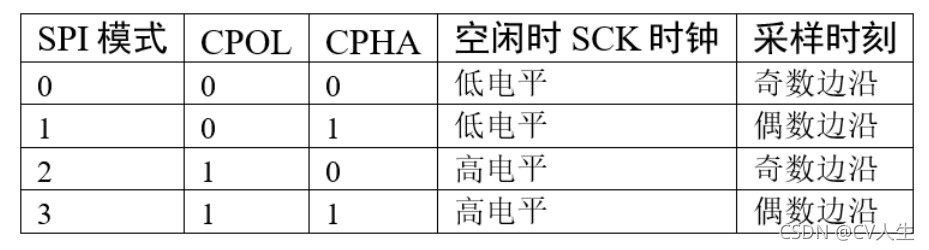

4、CPOL/CPHA 及通訊模式

時(shí)鐘極性 CPOL 是指 SPI 通訊設(shè)備處于空閑狀態(tài)時(shí),SCK 信號(hào)線的電平信號(hào) (即 SPI 通訊開始前、 NSS 線為高電平時(shí) SCK 的狀態(tài))。CPOL=0 時(shí),SCK 在空閑狀態(tài)時(shí)為低電平,CPOL=1 時(shí),則相反。

時(shí)鐘相位 CPHA 是指數(shù)據(jù)的采樣的時(shí)刻,當(dāng) CPHA=0 時(shí),MOSI 或 MISO 數(shù)據(jù)線上的信號(hào)將會(huì)在 SCK 時(shí)鐘線的“奇數(shù)邊沿”被采樣。當(dāng) CPHA=1 時(shí),數(shù)據(jù)線在 SCK 的“偶數(shù)邊沿”采樣。

由 CPOL 及 CPHA 的不同狀態(tài),SPI 分成了四種模式,見表 SPI 的四種模式 ,主機(jī)與從機(jī)需要工 作在相同的模式下才可以正常通訊,實(shí)際中采用較多的是“模式 0”與“模式 3”

【DMA直接存儲(chǔ)區(qū)訪問】

DMA(Direct Memory Access)—直接存儲(chǔ)器存取,是單片機(jī)的一個(gè)外設(shè),它的主要功能是用來搬數(shù) 據(jù),但是不需要占用 CPU,即在傳輸數(shù)據(jù)的時(shí)候,CPU 可以干其他的事情,好像是多線程一樣。數(shù)據(jù)傳輸支持從外設(shè)到存儲(chǔ)器或者存儲(chǔ)器到存儲(chǔ)器。

DMA 控制器包含了 DMA1 和 DMA2,其中 DMA1 有 7 個(gè)通道,DMA2 有 5 個(gè)通道,這里的通道 可以理解為傳輸數(shù)據(jù)的一種管道。要注意的是 DMA2 只存在于大容量的單片機(jī)中。

【常用存儲(chǔ)器】

一、存儲(chǔ)器種類

存儲(chǔ)器按其存儲(chǔ)介質(zhì)特性主要分為“易失性存儲(chǔ)器”和“非易失性存儲(chǔ)器”兩大類。其中的“易失/非易失”是指存儲(chǔ)器斷電后,它存儲(chǔ)的數(shù)據(jù)內(nèi)容是否會(huì)丟失的特性。

二、易失性存儲(chǔ)器——RAM 存儲(chǔ)器

RAM 是“Random Access Memory”的縮寫,被譯為隨機(jī)存儲(chǔ)器。所謂“隨機(jī)存取”,指的是當(dāng)存 儲(chǔ)器中的消息被讀取或?qū)懭霑r(shí),所需要的時(shí)間與這段信息所在的位置無關(guān)。

1、DRAM動(dòng)態(tài)隨機(jī)存儲(chǔ)器

DRAM 的存儲(chǔ)單元以電容的電荷來表示數(shù)據(jù),有電荷代表 1,無電荷代表 0。但時(shí)間一長,代表 1 的電容會(huì)放電,代表 0 的電容會(huì)吸收電荷,因此它需要定期刷新操作,這就是“動(dòng)態(tài) (Dynamic)”一詞所形容的特性。

2、SRAM靜態(tài)隨機(jī)存儲(chǔ)器

靜態(tài)隨機(jī)存儲(chǔ)器 SRAM 的存儲(chǔ)單元以鎖存器來存儲(chǔ)數(shù)據(jù),見圖 SRAM 存儲(chǔ)單元 。這種電路結(jié)構(gòu) 不需要定時(shí)刷新充電,就能保持狀態(tài) (當(dāng)然,如果斷電了,數(shù)據(jù)還是會(huì)丟失的),所以這種存儲(chǔ)器 被稱為“靜態(tài) (Static)”RAM。

三、非易失性存儲(chǔ)器

1、ROM 存儲(chǔ)器:ROM 是“Read Only Memory”的縮寫,意為只能讀的存儲(chǔ)器。由于技術(shù)的發(fā)展,后來設(shè)計(jì)出了可以方便寫入數(shù)據(jù)的 ROM,而這個(gè)“Read Only Memory”的名稱被沿用下來了。

MASK ROM:MASK(掩膜) ROM 就是正宗的“Read Only Memory”,存儲(chǔ)在它內(nèi)部的數(shù)據(jù)是在出廠時(shí)使用特殊工藝固化的,生產(chǎn)后就不可修改,其主要優(yōu)勢(shì)是大批量生產(chǎn)時(shí)成本低。

OTPROM:OTPROM(One Time Programable ROM) 是一次可編程存儲(chǔ)器。這種存儲(chǔ)器出廠時(shí)內(nèi)部并沒有資料,用戶可以使用專用的編程器將自己的資料寫入,但只能寫入一次,被寫入過后,它的內(nèi)容也不可再修改。

EPROM:EPROM(Erasable Programmable ROM) 是可重復(fù)擦寫的存儲(chǔ)器,它解決了 PROM 芯片只能寫入一次的問題。這種存儲(chǔ)器使用紫外線照射芯片內(nèi)部擦除數(shù)據(jù),擦除和寫入都要專用的設(shè)備。現(xiàn)在這種存儲(chǔ)器基本淘汰,被 EEPROM 取代。

EEPROM:EEPROM(Electrically Erasable Programmable ROM) 是電可擦除存儲(chǔ)器。EEPROM 可以重復(fù)擦寫,它的擦除和寫入都是直接使用電路控制,不需要再使用外部設(shè)備來擦寫。而且可以按字節(jié)為單位修改數(shù)據(jù),無需整個(gè)芯片擦除。

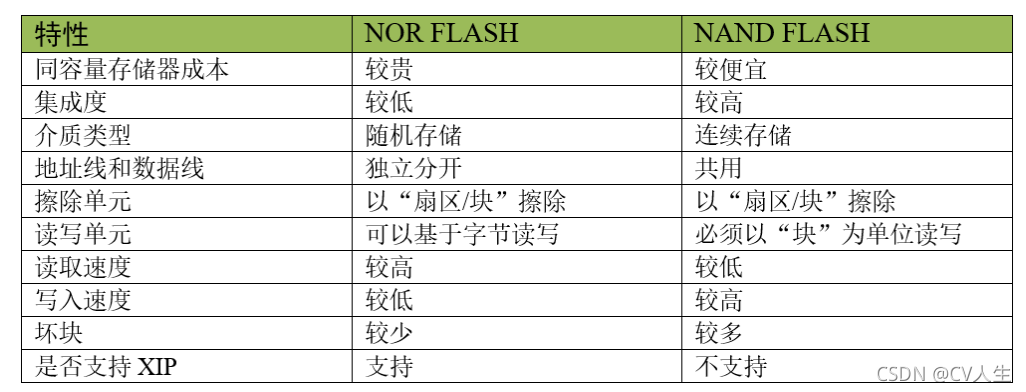

2、FLASH 存儲(chǔ)器

FLASH 存儲(chǔ)器又稱為閃存,它也是可重復(fù)擦寫的儲(chǔ)器,部分書籍會(huì)把 FLASH 存儲(chǔ)器稱為 FLASH ROM,但它的容量一般比 EEPROM 大得多,且在擦除時(shí),一般以多個(gè)字節(jié)為單位。根據(jù)存儲(chǔ)單元電路的不同,F(xiàn)LASH 存儲(chǔ)器又分為 NOR FLASH 和 NAND FLASH。

【ADC】

STM32f103 系列有 3 個(gè) ADC,精度為 12 位,每個(gè) ADC 最多有 16 個(gè)外部通道。其中 ADC1 和 ADC2 都有 16 個(gè)外部通道,ADC3 根據(jù) CPU 引腳的不同通道數(shù)也不同,一般都有 8 個(gè)外部通道。

【DAC】

STM32 具有片上 DAC 外設(shè),它的分辨率可配置為 8 位或 12 位的數(shù)字輸入信號(hào),具有兩個(gè) DAC 輸出通道,這兩個(gè)通道互不影響,每個(gè)通道都可以使用 DMA 功能,都具有出錯(cuò)檢測能力,可外 部觸發(fā)。

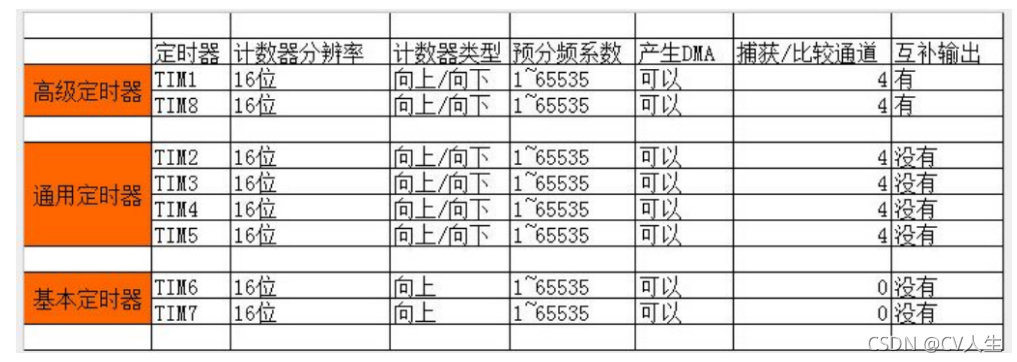

【TIM】

一、定時(shí)器的分類

STM32F1 系列中,除了互聯(lián)型的產(chǎn)品,共有 8 個(gè)定時(shí)器,分為基本定時(shí)器,通用定時(shí)器和高級(jí) 定時(shí)器。

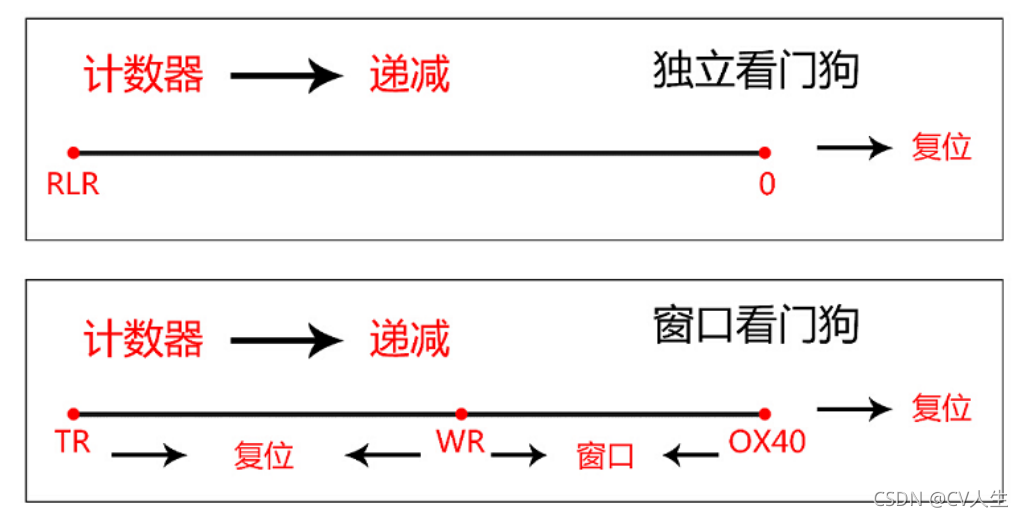

【IWDG獨(dú)立看門狗/WWDG窗口看門狗】

一、獨(dú)立看門狗定義及使用場景

獨(dú)立看門狗:是一個(gè) 12 位的遞減計(jì)數(shù)器,當(dāng)計(jì)數(shù)器的值從某個(gè)值一直減到 0 的時(shí)候,系統(tǒng)就會(huì)產(chǎn)生一個(gè)復(fù)位信號(hào),即 IWDG_RESET。如果在計(jì)數(shù)沒減到 0 之前,刷新了計(jì)數(shù)器的值的話,那么就不會(huì)產(chǎn)生復(fù)位信號(hào),這個(gè)動(dòng)作就是我們經(jīng)常說的喂狗。

獨(dú)立看門狗的時(shí)鐘由獨(dú)立的 RC 振蕩器 LSI 提供,即使主時(shí)鐘發(fā)生故障它仍然有效,非常獨(dú)立。LSI 的頻率一般在 30~60KHZ 之間,根據(jù)溫度和工作場合會(huì)有一定的漂移,我們一般取 40KHZ, 所以獨(dú)立看門狗的定時(shí)時(shí)間并一定非常精確,只適用于對(duì)時(shí)間精度要求比較低的場合。

二、窗口看門狗定義及使用場景

窗口看門狗:跟獨(dú)立看門狗一樣,也是一個(gè)遞減計(jì)數(shù)器不斷的往下遞減計(jì)數(shù),當(dāng)減到一個(gè)固定值 0X40 時(shí)還不喂狗的話,產(chǎn)生復(fù)位,這個(gè)值叫窗口的下限,是固定的值,不能改變。這個(gè)是跟獨(dú)立看門狗類似的地方,不同的地方是窗口看門狗的計(jì)數(shù)器的值在減到某一個(gè)數(shù)之前喂狗的話也會(huì)產(chǎn)生 復(fù)位,這個(gè)值叫窗口的上限,上限值由用戶獨(dú)立設(shè)置。窗口看門狗計(jì)數(shù)器的值必須在上窗口和下 窗口之間才可以喂狗。

三、圖解看門狗

RLR 是重裝載寄存器,用來設(shè)置獨(dú)立看門狗的計(jì)數(shù)器的值。TR 是窗口看門狗的計(jì)數(shù)器的值,由 用戶獨(dú)立設(shè)置,WR 是窗口看門狗的上窗口值,由用戶獨(dú)立設(shè)置。

-

控制器

+關(guān)注

關(guān)注

112文章

16445瀏覽量

179446 -

內(nèi)核

+關(guān)注

關(guān)注

3文章

1382瀏覽量

40422 -

STM32

+關(guān)注

關(guān)注

2272文章

10923瀏覽量

357556 -

Cortex-M3

+關(guān)注

關(guān)注

9文章

270瀏覽量

59589 -

GPIO

+關(guān)注

關(guān)注

16文章

1216瀏覽量

52377

原文標(biāo)題:STM32基礎(chǔ)知識(shí)總結(jié)

文章出處:【微信號(hào):電子工程師筆記,微信公眾號(hào):電子工程師筆記】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

STM32單片機(jī)中的C語言基礎(chǔ)知識(shí)

STM32基礎(chǔ)知識(shí)總結(jié)

第5章 PHY芯片和STM32的MAC基礎(chǔ)知識(shí)

有關(guān)STM32看門狗基礎(chǔ)知識(shí)

STM32開發(fā)基礎(chǔ)知識(shí)點(diǎn)匯總,總結(jié)的太棒了

路由器常用基礎(chǔ)知識(shí)總結(jié)

linux /Android 基礎(chǔ)知識(shí)總結(jié)大全

適合C語言小白看的基礎(chǔ)知識(shí)梳理總結(jié)

51單片機(jī)學(xué)習(xí) 基礎(chǔ)知識(shí)總結(jié)

Arduino入門必備基礎(chǔ)知識(shí)(基礎(chǔ)認(rèn)證考前總結(jié))

【51單片機(jī)】考試基礎(chǔ)知識(shí)總結(jié)(引腳)

STM32中C語言的基礎(chǔ)知識(shí)

STM32基礎(chǔ)知識(shí)總結(jié)

STM32基礎(chǔ)知識(shí)總結(jié)

評(píng)論