FPGA的BRAM和LUT等資源都是有限的,在FPGA開發(fā)過程中,可能經(jīng)常遇到BRAM或者LUT資源不夠用的情況。

一般建議BRAM和LUT資源的消耗不要超過80%,當然高端一點的FPGA芯片也可以放寬到90%,超過這個限制,可能就會出現(xiàn)時序違例較嚴重的情況,導致上板運行出現(xiàn)異常的情況。

今天分享一下BRAM資源使用優(yōu)化策略,以Vivado的 Block Memory Generator為例 。

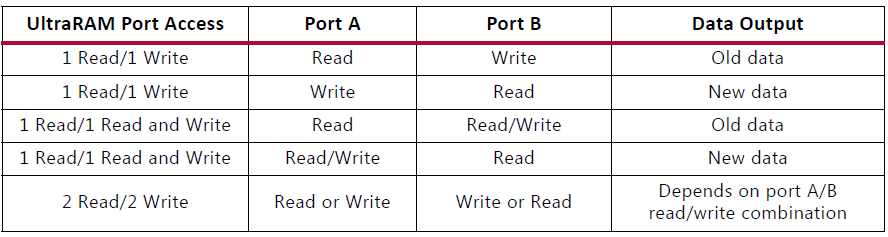

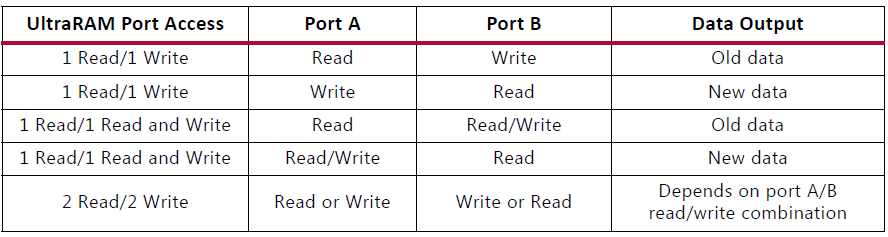

1、Distribute BRAM或URAM 替代BRAM

存儲深度和寬度較小,且LUT資源或URAM有富裕,可以用“Distribute BRAM”或“URAM”來替代。

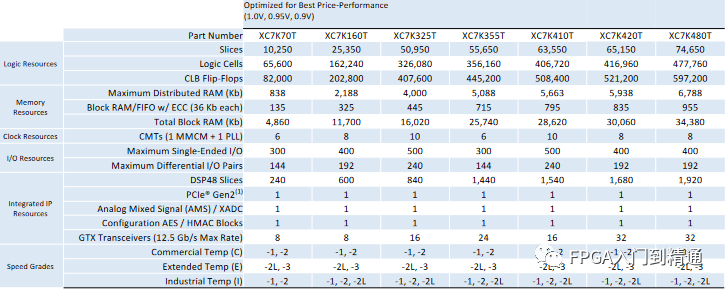

這里需要注意使用的FPGA芯片型號,是否帶URAM資源。

- (* ram_style = "block" *)表示用Block RAM實現(xiàn)

- (* ram_style = "reg" *)表示用寄存器實現(xiàn)

- (* ram_style = "distributed" *)表示用分布式 RAM實現(xiàn)

- (* ram_style = "uram" *)表示用uram實現(xiàn)

這里給出代碼示例:

// FPGA 雙口 RAM

module dual_port_ram(

input clk,

input [7:0] data_in,

input [5:0] wr_addr,

input wr_en,

input [5:0] rd_addr,

output reg [7:0] data_out

);

// 聲明雙口 RAM 存儲器

(* ram_style = "block" *)reg [7:0] ram[63:0];

// 時鐘上升沿寫入

always @(posedge clk) begin

if (wr_en)

ram[wr_addr] <= data_in;

end

// 讀取;

always @(posedge clk) begin

data_out <= ram[rd_addr];

end

endmodule

2、雙口ROM替代單口ROM

如果工程中,有兩個以上的ROM或RAM使用的是相同的數(shù)據(jù),可以使用雙口替代單口模式,資源消耗是一樣的,這樣就可以節(jié)省一個或多個ROM IP。

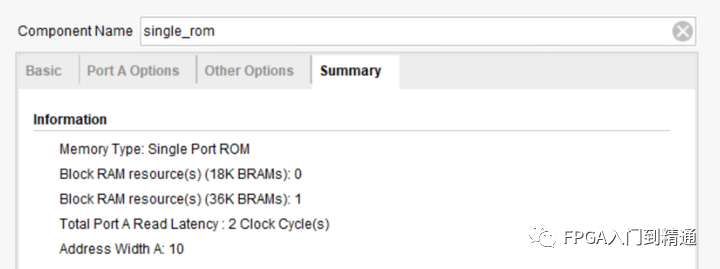

這里對比一下“數(shù)據(jù)寬度為32,存儲深度為1024”的單口和雙口模式下的資源消耗。

3、合理的數(shù)據(jù)寬度和深度設置

要想FPGA BRAM資源消耗優(yōu)化,更關鍵的是優(yōu)化FPGA工程的緩存大小設計,計算理論上緩存數(shù)據(jù)的位寬和最大深度,選擇出合適的參數(shù)。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605989 -

芯片

+關注

關注

456文章

51170瀏覽量

427227 -

ROM

+關注

關注

4文章

575瀏覽量

85987 -

資源

+關注

關注

0文章

59瀏覽量

17827 -

BRAM

+關注

關注

0文章

41瀏覽量

11016

發(fā)布評論請先 登錄

相關推薦

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM實現(xiàn)PS與PL交互

FPGA設計中BRAM的知識科普

FPGA資源優(yōu)化方法

【InTime試用體驗】使用簡易、策略選擇精確度高的一款時序優(yōu)化軟件

URAM和BRAM的區(qū)別是什么

FPGA設計應用及優(yōu)化策略有哪些?

FPGA實現(xiàn)基于Vivado的BRAM IP核的使用

使用FPGA調用RAM資源的詳細說明

FPGA布局及資源優(yōu)化

URAM和BRAM有哪些區(qū)別

URAM和BRAM有什么區(qū)別

FPGA實現(xiàn)基于Vivado的BRAM IP核的使用

基于FPGA設計的BRAM內(nèi)部結構

FPGA的BRAM資源使用優(yōu)化策略

FPGA的BRAM資源使用優(yōu)化策略

評論