用FPGA的鎖相環(huán)PLL給外圍芯片提供時(shí)鐘

FPGA鎖相環(huán)PLL(Phase-Locked Loop)是一種廣泛使用的時(shí)鐘管理電路,可以對(duì)輸入時(shí)鐘信號(hào)進(jìn)行精確控制和提高穩(wěn)定性,以滿足各種應(yīng)用場(chǎng)景下的時(shí)序要求。尤其對(duì)于需要高速數(shù)據(jù)傳輸、信號(hào)采集處理等場(chǎng)景的數(shù)字信號(hào)處理系統(tǒng)而言,F(xiàn)PGA PLL的應(yīng)用更是至關(guān)重要。本文將介紹FPGA鎖相環(huán)PLL的基本原理、設(shè)計(jì)流程、常見問題及解決方法,以及該技術(shù)在外圍芯片時(shí)鐘提供方面的應(yīng)用實(shí)例。

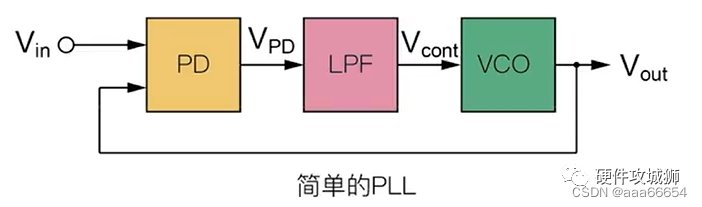

一、FPGA鎖相環(huán)PLL基本原理

1.時(shí)鐘頻率的調(diào)整

FPGA的鎖相環(huán)PLL可用于頻率合成、頻率分頻、頻率鎖定等應(yīng)用場(chǎng)景。通過選擇不同的分頻倍數(shù)、反饋比例等參數(shù)設(shè)置,F(xiàn)PGA的PLL可以將輸入時(shí)鐘信號(hào)(例如50MHz)轉(zhuǎn)換成符合特定要求的輸出時(shí)鐘信號(hào)(例如150MHz)。此外,PLL還可以實(shí)現(xiàn)時(shí)鐘頻率的穩(wěn)定性控制、抖動(dòng)降低等功能。

2.時(shí)鐘相位的保持

由于時(shí)鐘信號(hào)在傳輸中容易因信號(hào)衰減、干擾等原因而發(fā)生相位偏移或漂移,因此在數(shù)字信號(hào)處理中,時(shí)序要求往往非常嚴(yán)格。FPGA的PLL可以通過引入反饋機(jī)制,使輸出時(shí)鐘與輸入時(shí)鐘在相位上保持一致,從而消除了輸入時(shí)鐘信號(hào)的相位抖動(dòng)和漂移問題,提高了時(shí)序穩(wěn)定性和系統(tǒng)性能。

二、FPGA鎖相環(huán)PLL設(shè)計(jì)流程

FPGA鎖相環(huán)PLL的設(shè)計(jì)流程包括以下幾個(gè)關(guān)鍵步驟:

1.確定輸入輸出時(shí)鐘頻率要求

在設(shè)計(jì)鎖相環(huán)PLL之前,首先需要明確輸入時(shí)鐘頻率和輸出時(shí)鐘頻率的要求。一般來說,輸入時(shí)鐘頻率會(huì)直接決定PLL的穩(wěn)定性和可靠性,而輸出時(shí)鐘頻率則需要根據(jù)具體應(yīng)用場(chǎng)景做出相應(yīng)選擇。在確定輸入輸出時(shí)鐘頻率要求時(shí),需要全面考慮系統(tǒng)性能、功耗和成本等因素。

2.選擇合適的PLL芯片和器件

根據(jù)設(shè)計(jì)要求,選擇合適型號(hào)的鎖相環(huán)PLL芯片和外圍器件是設(shè)計(jì)流程中的重要一步。通常情況下,F(xiàn)PGA廠家會(huì)提供相應(yīng)的鎖相環(huán)IP核,設(shè)計(jì)工程師可以直接調(diào)用該IP核,進(jìn)行參數(shù)設(shè)置和優(yōu)化。此外,還需要注意PLL的時(shí)鐘分頻比、輸出時(shí)鐘占空比、穩(wěn)定度、抖動(dòng)度等指標(biāo),以及其與FPGA芯片的兼容性等問題。

3.進(jìn)行鎖相環(huán)參數(shù)設(shè)置

鎖相環(huán)PLL的性能和穩(wěn)定性很大程度上取決于參數(shù)設(shè)置和調(diào)整。在進(jìn)行參數(shù)設(shè)置時(shí),需要根據(jù)具體應(yīng)用場(chǎng)景中的時(shí)鐘頻率、時(shí)序要求、抖動(dòng)等指標(biāo)進(jìn)行適當(dāng)調(diào)整。具體而言,需要設(shè)置參考時(shí)鐘、反饋時(shí)鐘、比例因子、反饋分頻比、輸出分頻比等參數(shù)。

4.進(jìn)行仿真和調(diào)試

在設(shè)置好PLL參數(shù)之后,需要進(jìn)行仿真和調(diào)試,驗(yàn)證所設(shè)置的參數(shù)是否能夠滿足系統(tǒng)性能和穩(wěn)定性要求。通常情況下,可以使用Vivado或Quartus等EDA工具進(jìn)行仿真和調(diào)試。

三、FPGA鎖相環(huán)PLL常見問題及解決方法

在FPGA鎖相環(huán)PLL的設(shè)計(jì)過程中,也會(huì)存在一些常見問題,例如輸入時(shí)鐘穩(wěn)定性、抖動(dòng)、鎖定時(shí)間等問題。針對(duì)這些常見問題,可以采取以下一些解決措施:

1.優(yōu)化輸入時(shí)鐘電路,提高時(shí)鐘穩(wěn)定性

輸入時(shí)鐘穩(wěn)定性是影響PLL性能和穩(wěn)定性的一個(gè)重要因素。在輸入時(shí)鐘穩(wěn)定性不佳的情況下,常會(huì)出現(xiàn)PLL無法鎖定、抖動(dòng)過大等問題。為了優(yōu)化輸入時(shí)鐘電路,可以采用差分信號(hào)傳輸方式,增加阻抗匹配電路,降低信號(hào)瑕疵和干擾等措施。

2.調(diào)整PLL參考時(shí)鐘和反饋時(shí)鐘

參考時(shí)鐘和反饋時(shí)鐘是確定鎖相環(huán)PLL頻率的兩個(gè)關(guān)鍵因素。為了提高鎖相環(huán)PLL的穩(wěn)定性,可以盡可能選擇高精度、低抖動(dòng)的參考時(shí)鐘和反饋時(shí)鐘。此外,還可以選擇更優(yōu)的比例因子、反饋分頻比等參數(shù),以達(dá)到更好的性能表現(xiàn)。

3.增加反饋環(huán)路濾波器

反饋環(huán)路濾波器可以消除輸入時(shí)鐘信號(hào)的抖動(dòng)和漂移,從而提高PLL的穩(wěn)定性和性能。在實(shí)際設(shè)計(jì)中,可以增加額外的反饋環(huán)路濾波器,或優(yōu)化現(xiàn)有的濾波器參數(shù),以適應(yīng)不同的應(yīng)用場(chǎng)景需求。

四、FPGA鎖相環(huán)PLL在提供外圍芯片時(shí)鐘方面的應(yīng)用實(shí)例

FPGA鎖相環(huán)PLL在提供外圍芯片時(shí)鐘方面的應(yīng)用實(shí)例非常廣泛。例如,在數(shù)字信號(hào)處理系統(tǒng)中,常常需要對(duì)采集設(shè)備、輸出設(shè)備等外圍芯片進(jìn)行時(shí)鐘管理。其中,外圍芯片的時(shí)鐘穩(wěn)定性和相位一致性直接影響系統(tǒng)的采樣精度、時(shí)序穩(wěn)定性和性能表現(xiàn)。在這種場(chǎng)景下,F(xiàn)PGA鎖相環(huán)PLL可以通過提供穩(wěn)定、可靠、高精度的時(shí)鐘信號(hào),實(shí)現(xiàn)對(duì)外圍芯片的時(shí)鐘管理和校準(zhǔn)。

另外,在工業(yè)自動(dòng)化、通信網(wǎng)絡(luò)、醫(yī)療診斷等領(lǐng)域,也大量應(yīng)用了FPGA鎖相環(huán)PLL技術(shù)。例如,在互聯(lián)網(wǎng)通信中,F(xiàn)PGA鎖相環(huán)PLL可以實(shí)現(xiàn)信號(hào)轉(zhuǎn)換和調(diào)制解調(diào)等功能;在醫(yī)療系統(tǒng)中,F(xiàn)PGA鎖相環(huán)PLL可提供高穩(wěn)定的同步時(shí)鐘,配合高速數(shù)據(jù)傳輸,實(shí)現(xiàn)高分辨率醫(yī)學(xué)圖像的采集和處理等。

綜上所述,F(xiàn)PGA鎖相環(huán)PLL是一種非常重要的時(shí)鐘管理技術(shù),可以優(yōu)化數(shù)字信號(hào)處理系統(tǒng)的時(shí)序穩(wěn)定性和性能表現(xiàn)。在今后的應(yīng)用中,F(xiàn)PGA鎖相環(huán)PLL技術(shù)將進(jìn)一步發(fā)揮其優(yōu)勢(shì),滿足更加苛刻和復(fù)雜的應(yīng)用場(chǎng)景需求。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

606007 -

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

590瀏覽量

87895 -

pll

+關(guān)注

關(guān)注

6文章

781瀏覽量

135332 -

時(shí)鐘電路

+關(guān)注

關(guān)注

10文章

239瀏覽量

50799 -

環(huán)路濾波器

+關(guān)注

關(guān)注

3文章

26瀏覽量

13200

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

鎖相環(huán)是什么意思

可編程晶振的鎖相環(huán)原理

鎖相環(huán)PLL的噪聲分析與優(yōu)化 鎖相環(huán)PLL與相位噪聲的關(guān)系

鎖相環(huán)PLL在無線電中的應(yīng)用 鎖相環(huán)PLL與模擬電路的結(jié)合

鎖相環(huán)PLL與頻率合成器的區(qū)別

鎖相環(huán)PLL的工作原理 鎖相環(huán)PLL應(yīng)用領(lǐng)域

將 Hercules 鎖相環(huán)(PLL)咨詢SSWFO21#45的影響降至最低

CDC509高性能、低偏斜、低抖動(dòng)、鎖相環(huán)(PLL)時(shí)鐘驅(qū)動(dòng)器數(shù)據(jù)表

CDCVF2510A鎖相環(huán)(PLL)時(shí)鐘驅(qū)動(dòng)器數(shù)據(jù)表

CDCVF2505時(shí)鐘鎖相環(huán)時(shí)鐘驅(qū)動(dòng)器數(shù)據(jù)表

簡(jiǎn)述鎖相環(huán)的基本結(jié)構(gòu)

鎖相環(huán)和鎖相放大器的區(qū)別

鎖相環(huán)相位噪聲的影響因素

鎖相環(huán)的基本原理和主要作用

鎖相環(huán)PLL學(xué)習(xí)記錄

用FPGA的鎖相環(huán)PLL給外圍芯片提供時(shí)鐘

用FPGA的鎖相環(huán)PLL給外圍芯片提供時(shí)鐘

評(píng)論