今天開源一個FPGA圖像處理相關(guān)的項目:圖像旋轉(zhuǎn)。圖像旋轉(zhuǎn)算法本身非常簡單,但是如果想讓旋轉(zhuǎn)之后的圖像更加完整、平滑,還需要進行雙線性插值處理,因此整個算法FPGA實現(xiàn)起來還是有一定難度的。

01算法流程

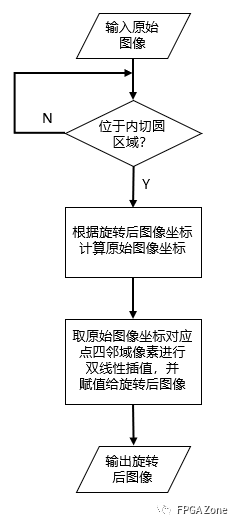

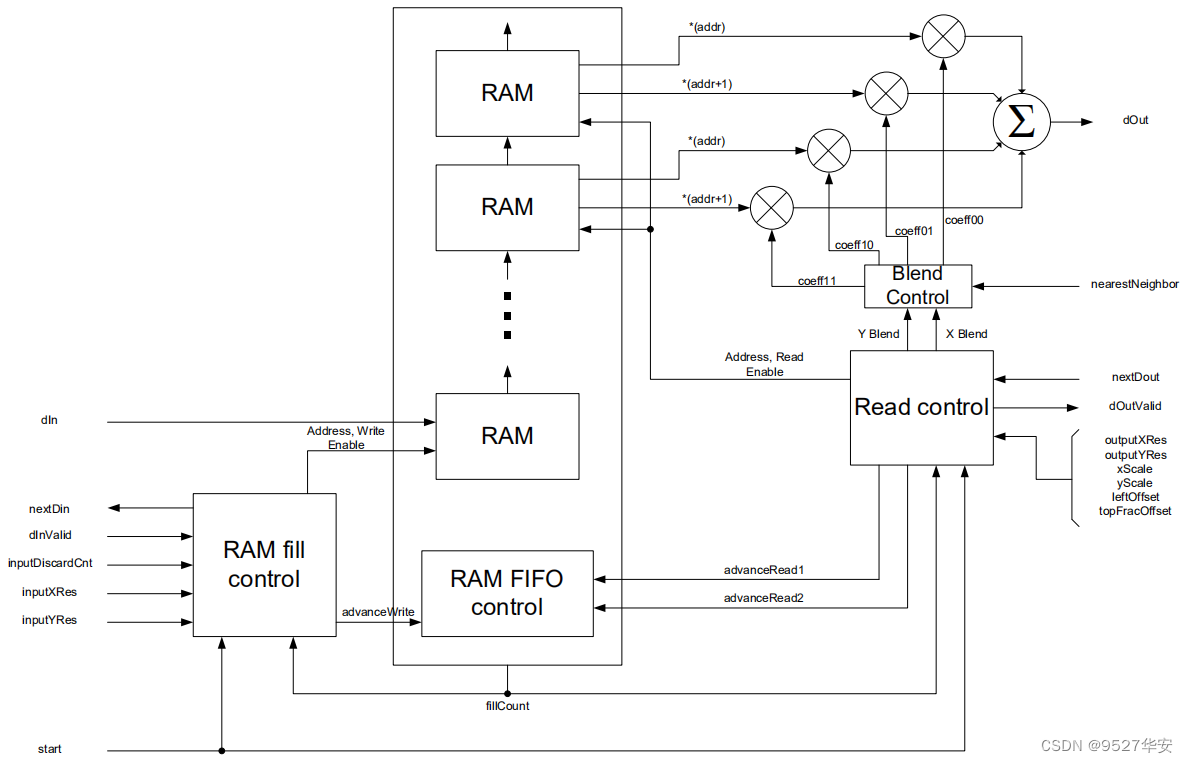

圖像旋轉(zhuǎn)算法可以有兩種思路:一種是前向映射,就是由原始圖像出發(fā),將像素點傳遞給旋轉(zhuǎn)后的圖像;另一種是反向映射,就是從旋轉(zhuǎn)后的圖像出發(fā),找到原始圖像對應(yīng)像素點,然后通過雙線性插值算法使旋轉(zhuǎn)后圖像更清晰完整。由于前者會丟失很多圖像信息,因此在本項目中采用后者。算法流程圖如下。

02原理簡介

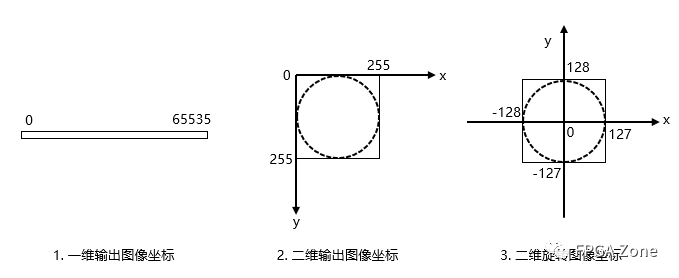

輸入圖像分辨率默認為256*256,算法處理的是以128為半徑內(nèi)切圓區(qū)域。

輸出圖像一維坐標(biāo)為i[0,65535],假設(shè)圖像逆時針旋轉(zhuǎn)θ得到輸出圖像,對應(yīng)的輸入圖像旋轉(zhuǎn)坐標(biāo)(X,Y)則可以表示成:

X=(i%256-128)*cos(θ)+(128-i/256)*sin(θ)

Y=-(i%256-128)*sin(θ)+(128-i/256)*cos(θ)

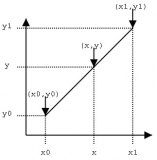

首先,對(X,Y)向下取整得到(xx,yy),小數(shù)部分表示為(dx,dy),將(xx,yy)轉(zhuǎn)換到輸出圖像坐標(biāo)系下為:

xx=xx+128;

yy=128-yy;

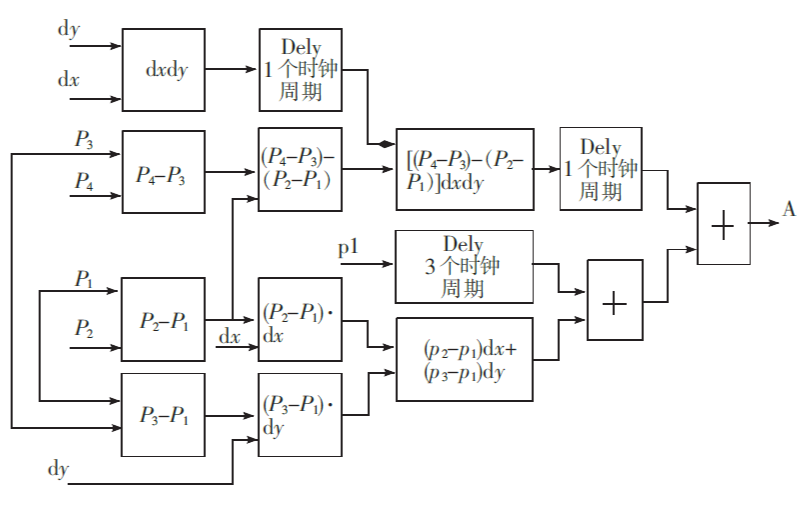

進行雙線性插值處理:

I(xx,yy)=(1-dx)(1-dy)I(xx,yy)+ (1-dx)dyI(xx,yy-1)+dx(1-dy)I(xx+1,yy)+dxdyI(xx+1,y-1)

浮點數(shù)定點化處理:

- sin(θ)和cos(θ)值為乘以8192取整后的結(jié)果;

- 將上式中dx,dy項定義為8位整數(shù),1改為255參與運算,最后將計算結(jié)果向右平移16位。

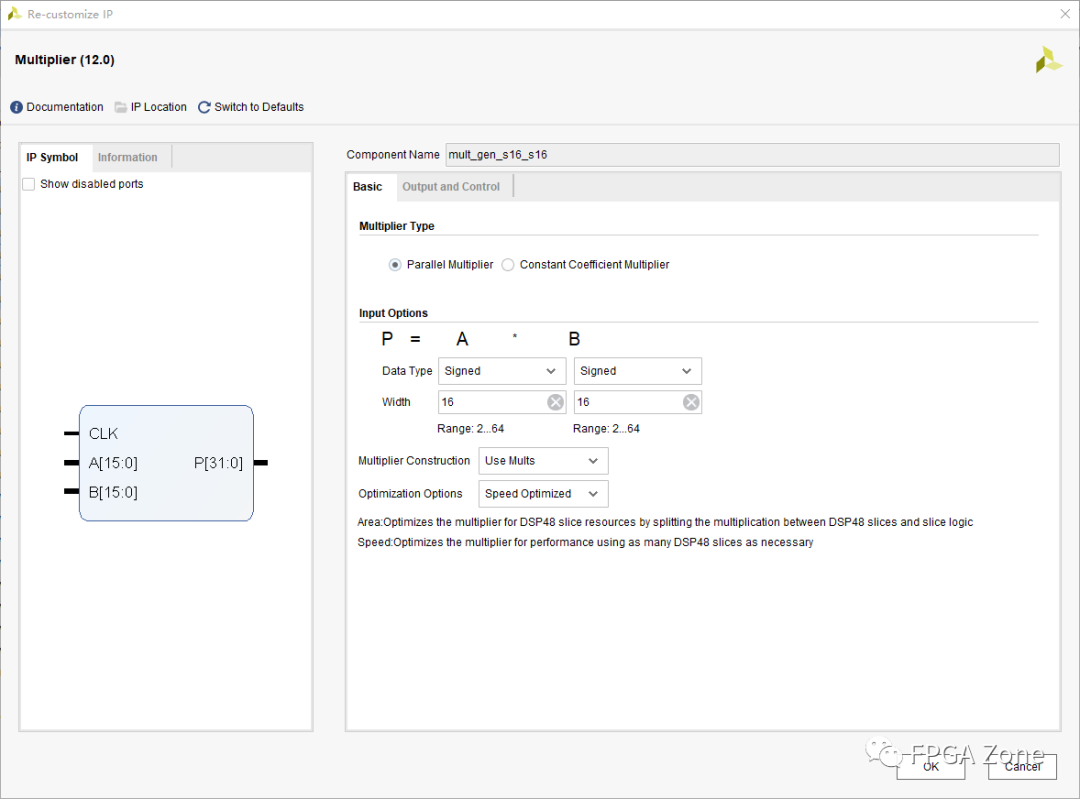

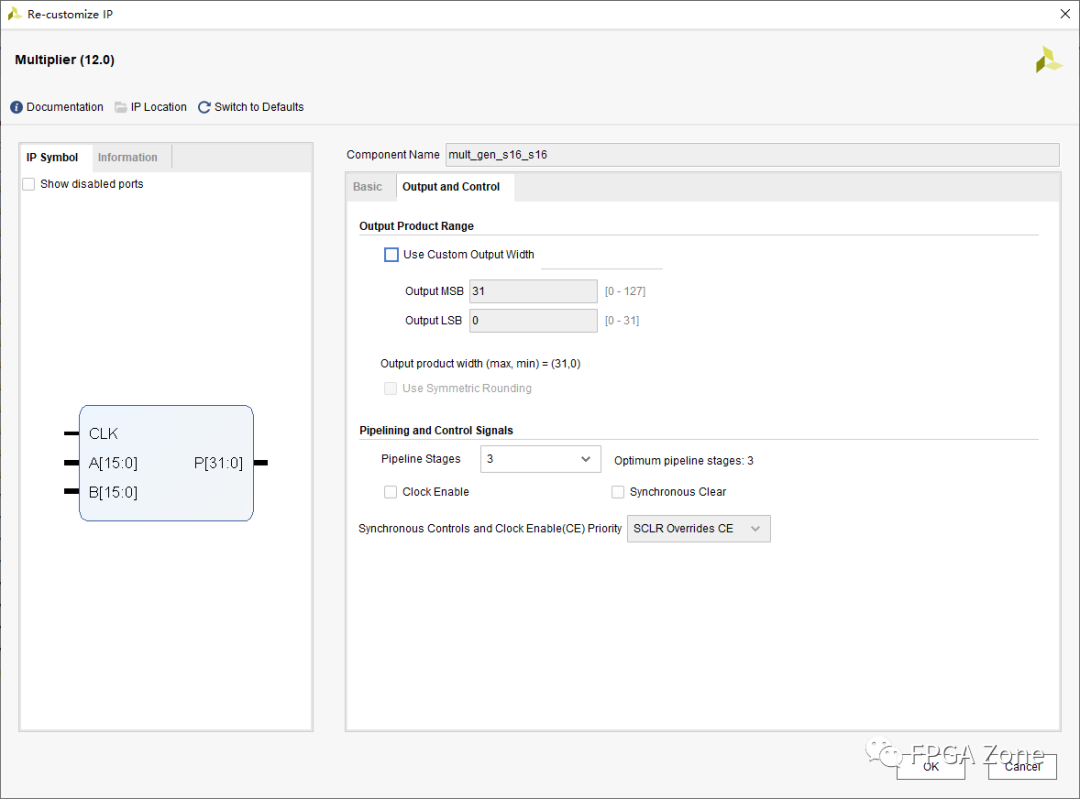

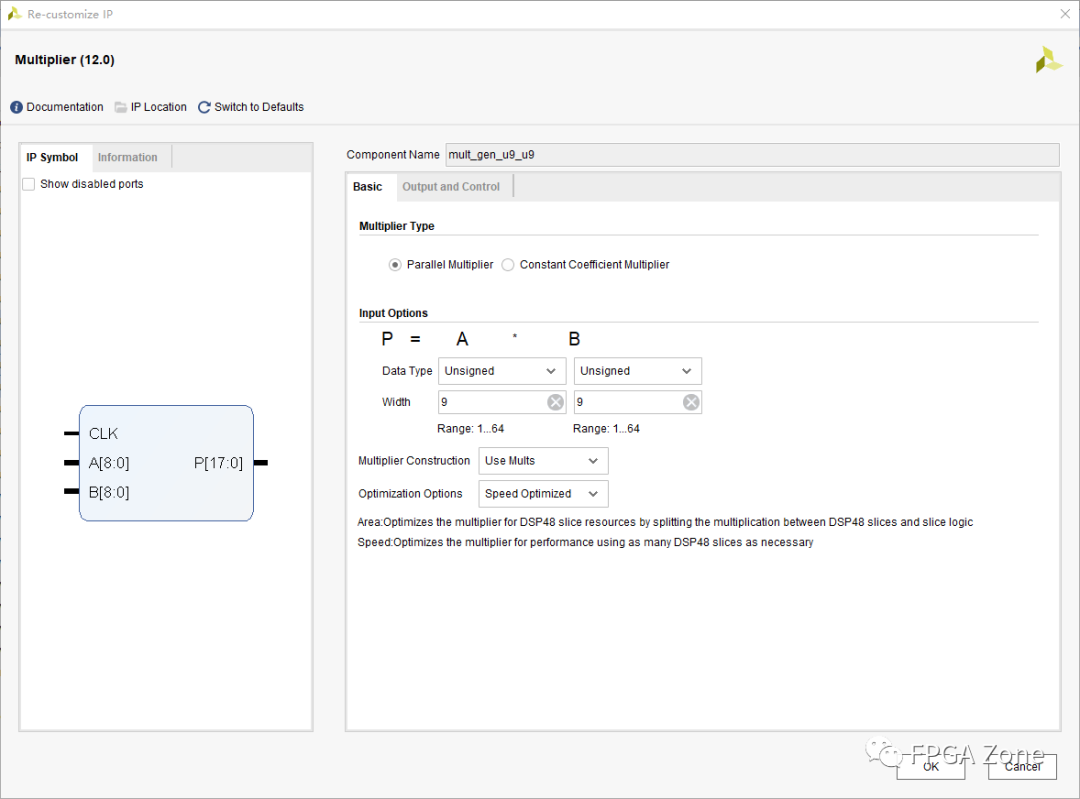

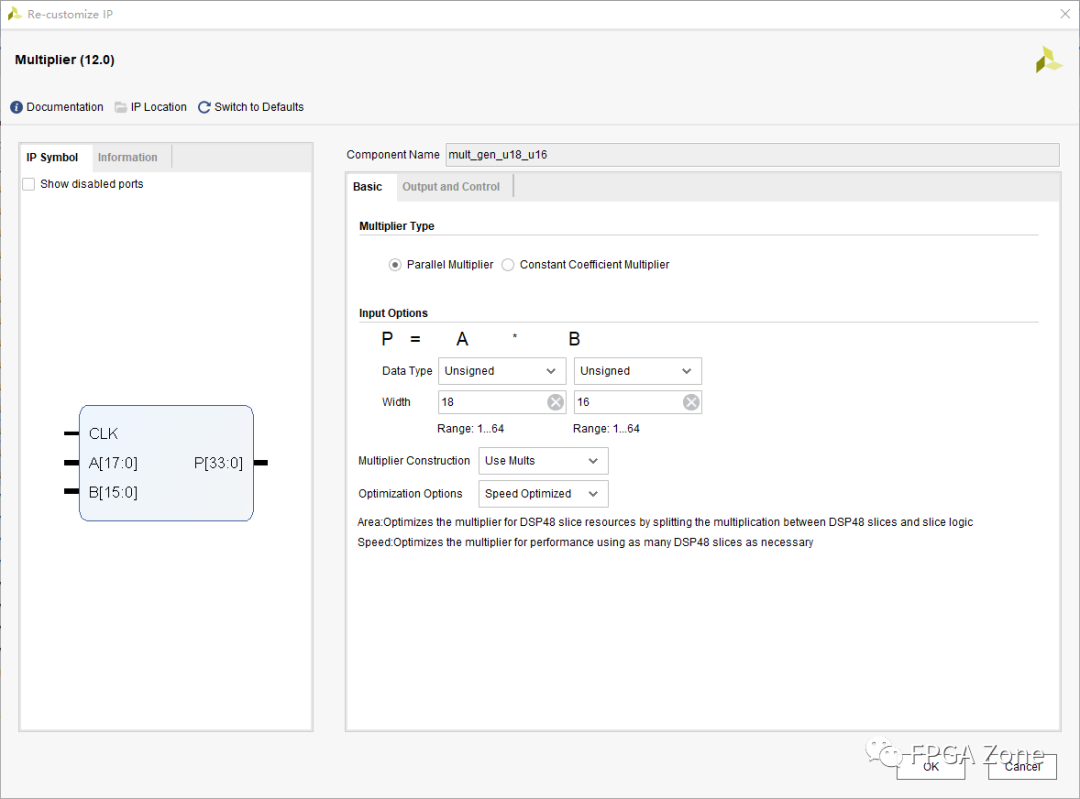

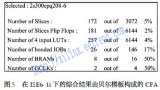

03IP核配置

該Vivado工程用到的IP主要是 **Multiplier,**用于乘法運算。

- Signed_16bit * Signed_16bit

- Unsigned_9bit * Unsigned_9bit

- Unsigned_18bit * Unsigned_16bit

04測試結(jié)果

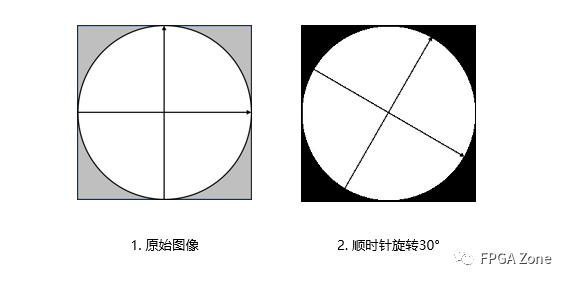

下方左側(cè)圖像為256*256大小的原始測試圖像,右側(cè)為順時針旋轉(zhuǎn)30°后的結(jié)果。其中只處理了內(nèi)切圓區(qū)域內(nèi)的圖像,其余部分像素賦值為零。

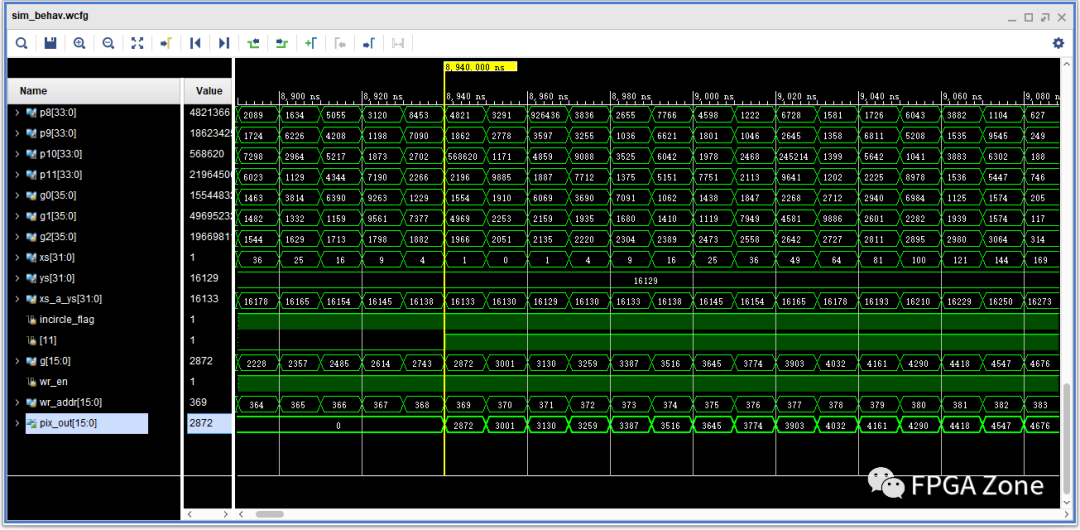

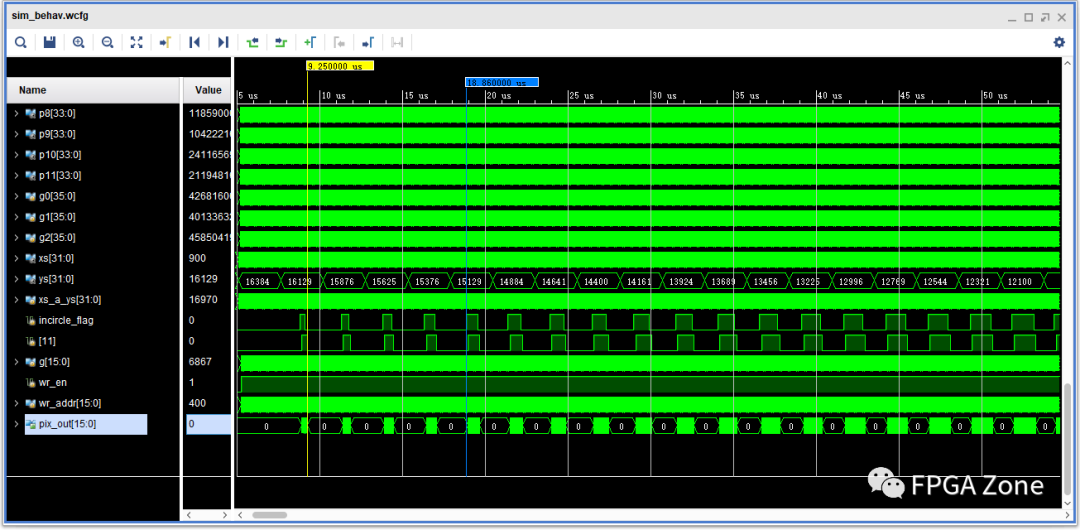

Verilog代碼的Vivado仿真結(jié)果如下所示。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21797瀏覽量

606016 -

圖像處理

+關(guān)注

關(guān)注

27文章

1300瀏覽量

56894 -

算法

+關(guān)注

關(guān)注

23文章

4630瀏覽量

93356 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66890 -

圖像旋轉(zhuǎn)

+關(guān)注

關(guān)注

0文章

3瀏覽量

2210

發(fā)布評論請先 登錄

相關(guān)推薦

什么是線性插值?一維線性插值和雙線性插值在BMS開發(fā)中的應(yīng)用

求雙線性插值法的C語言程序!幫幫忙!拜托各位了!

這個論壇里面有沒有人做 fpga圖像縮小的 (不是放大)??求交流交流 真的是很頭大 到處找不到做 圖像縮小的?

一種基于FPGA的實時視頻圖像處理算法研究與實現(xiàn)

一種改進的線性圖像插值算法

基于最優(yōu)移位雙線性插值的圖像縮放旋轉(zhuǎn)硬件加速研究

基于雙線性插值原理實現(xiàn)圖像縮放算法

基于FPGA的雙線性CFA插值算法的設(shè)計

如何通過FPGA變成我們看到的色彩斑斕的圖片

在FPGA上如何實現(xiàn)雙線性插值的計算

使用FPGA實現(xiàn)視頻圖像縮放顯示的設(shè)計論文說明

雙線性插值算法的講解

FPGA純verilog代碼實現(xiàn)圖像縮放

基于FPGA的圖像旋轉(zhuǎn)和雙線性插值算法設(shè)計

基于FPGA的圖像旋轉(zhuǎn)和雙線性插值算法設(shè)計

評論