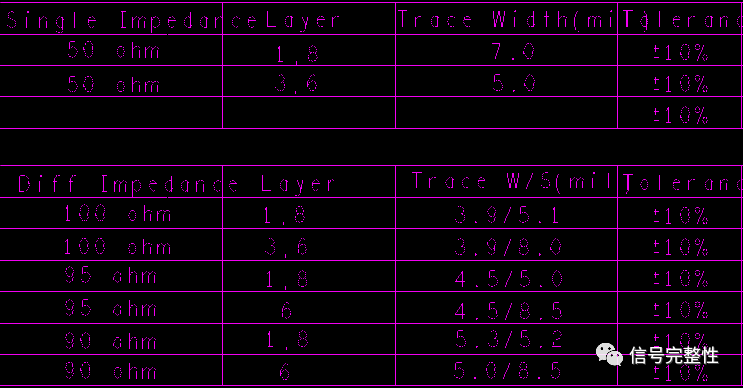

高速電路設計的工程師都知道,在進行高速電路設計時,對傳輸線的阻抗有明確的要求,給板廠發生產文件(Gerber)時也會一而再,再而三的告訴他們要控制好阻抗。比如下圖所示在PCB中定義每一層的阻抗要求。

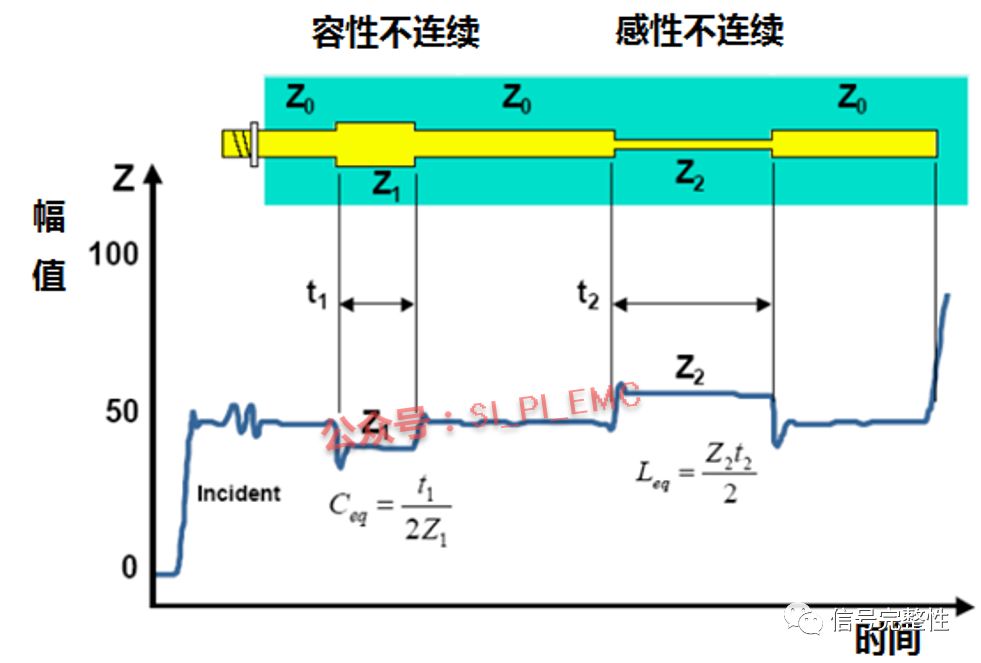

阻抗不連續會導致信號完整性的問題,比如信號反射、非單調、抖動增大、誤碼增多等等。還有可能增大能量輻射造成EMI的問題,也會減少器件的壽命等等。

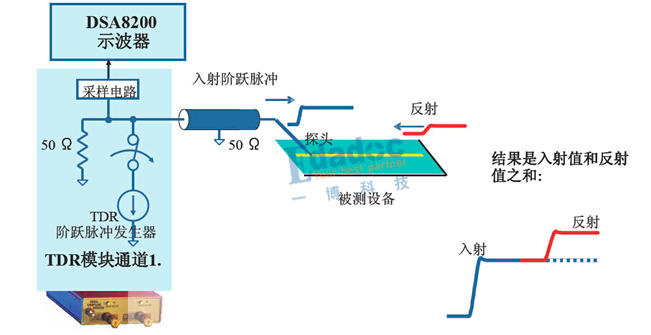

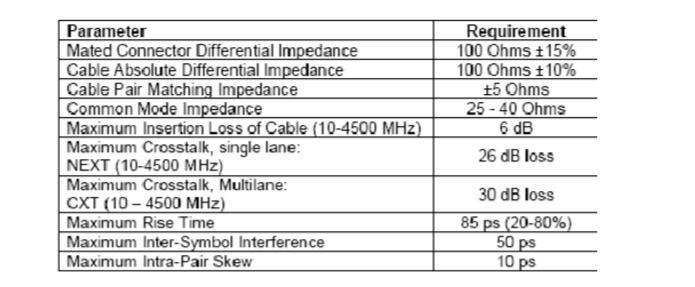

不僅僅是PCB,還有連接器、線纜、芯片設計也一樣有明確的阻抗要求。既然在設計的時候有定義阻抗,那么就需要測量生產出來的產品,檢查其是否能滿足阻抗的要求。一般使用采樣示波器(帶TDR模塊)、網絡分析儀(帶TDR選件)或者簡易的阻抗測試儀測量。前面兩種我都使用過,精度都非常高,后面一種只是在展會上試用過,在特定的場合其精度也不錯。

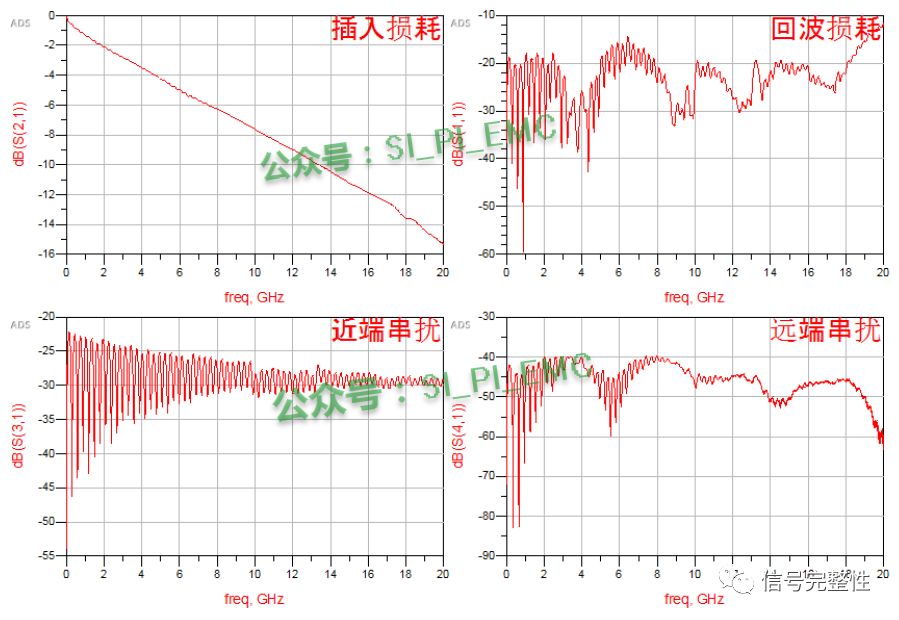

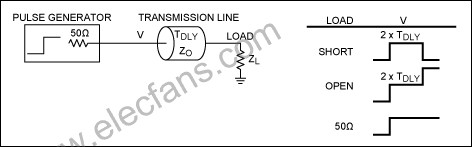

今天咱們介紹的并不是這些儀器,也不對比他們的優劣。今天要給大家介紹的是當大家使用網絡分析儀測試獲得S參數或者仿真獲得S參數時,如何獲得TDR的結果。盡管S參數能完全的描述PCB、線纜等傳輸線的無源特性,但是這些都是頻域的,只能表征整體的特性,無法表征物理結構每一個點的變化情況。

TDR的結果表征的是阻抗隨著時間的變化。

在ADS中有多種方式可以把頻域的S參數轉換為TDR的結果,在本文中給大家介紹一種常用的方式,即采用編輯公式的方式,把S參數轉換為TDR結果。

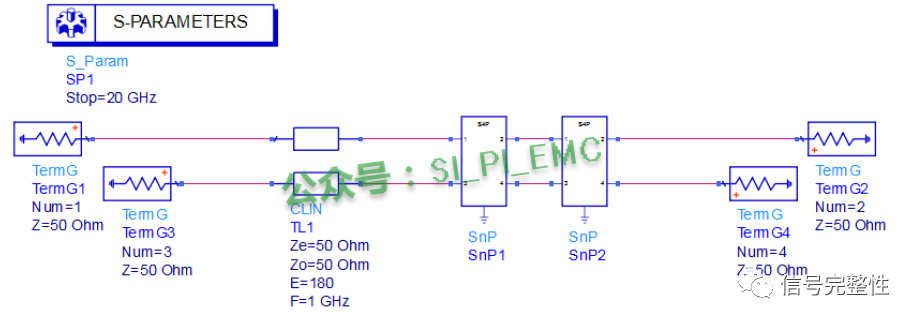

先建立一個原理圖:

這是一個差分對傳輸線的S參數仿真原理圖,仿真完成后,在ADS的數據顯示窗口中先編輯一個單端轉差分的公式SDD11=0.5*(S11-S31+S33-S13)(不會的,可以參考下文ADS信號完整性專題之如何將單端S參數轉化為差分S參數)

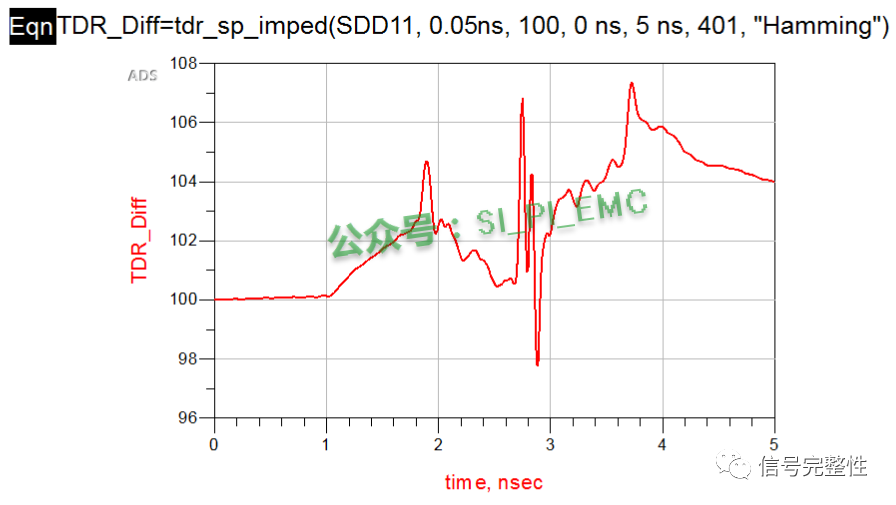

S參數轉換為TDR使用的公式為TDR= tdr_sp_imped(Sii, delay, zRef, Tstart, Tstop, NumPts, window)。根據此公式編輯差分對S參數轉TDR阻抗公式并查TDR結果曲線,如下圖所示:

如果是單端的S2P的文件,則把SDD11修改為S11,參考阻抗zRef修改為50ohm(具體參考阻抗zRef、截止時間Tstop修改為多少,則根據實際情況而定)。

其它的方式,比如使用Front Panel SP TDR 工具直接轉TDR,使用瞬態計算方式等。

審核編輯:湯梓紅

-

pcb

+關注

關注

4326文章

23161瀏覽量

399976 -

示波器

+關注

關注

113文章

6282瀏覽量

185849 -

網絡分析儀

+關注

關注

8文章

646瀏覽量

27506 -

高速電路

+關注

關注

8文章

159瀏覽量

24275 -

S參數

+關注

關注

2文章

141瀏覽量

46608

原文標題:S參數轉TDR(阻抗)--網絡分析儀“變”采樣示波器

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何使用TDR進行電纜測試

在ADS仿真或者查看S參數的方法

基于TDR/TDT的S參數測量設計

S參數什么頻段會影響TDR阻抗

高速串行數據挑戰與TDR阻抗測試和高速串行鏈路的分析

什么是TDR?TDR測試原理分析

迪賽康的TDR手持探頭測試應用方案

ADS中S參數轉TDR測試方案

ADS中S參數轉TDR測試方案

評論