Sub-LVDS是一種低功耗、低誤碼率、低串擾和低輻射的差分信號技術,是LVDS技術在Camera接口上的一種應用。Sub-LVDS采用低擺幅電流模式傳輸系統,同傳統的電壓模式相比較,在達到幾乎相同的性能水平時,由于有比傳統模式更好的抗電源噪聲能力,它可以在噪聲容限低得多,而且擺幅也低得多的情況下工作。目前,Sub-LVDS技術在Sony的Camera/Sensor中比較常見,主要傳輸的數據格式為RAW10或者RAW12。SUB-LVDS的電壓更低,共模電壓為1.8V,差模電壓為150mV。

Sub-LVDS是LVDS電氣規范的低電壓版本,不同于LVDS,它的共模和差分信號電平降低,但仍然能夠驅動LVDS接收器。當LVDS驅動需要與Sub-LVDS接收器接口連接時,問題就出現了。從驅動的信號開始電壓水平不在一個合適的范圍內,以確保與接收器的正常通信,必須改變驅動器輸出以保證適當的電壓水平。本文討論如何將LVDS驅動器和Sub-LVDS接收器之間的接口互聯,以及如何使用簡單的電阻網絡修改信號電壓等級以保證兼容性。

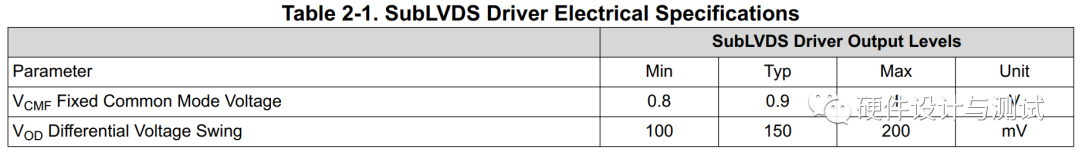

Sub-LVDS驅動器輸出參數

Sub-LVDS驅動器接收參數

LVDS輸出與Sub-LVDS驅動器接收參數

從以上表格得知,SubLVDS作為LVDS的發展,采用低擺幅電流模式傳輸系統,同傳統的電壓模式相比較,在達到幾乎相同的性能水平時,由于有比傳統模式更好的抗電源噪聲能力,它可以在噪聲容限低得多,而且擺幅也低得多的情況下工作。設計一個高效電流模式電路的主要挑戰是靜態功耗,但這在超高速網絡中不成問題,因為這時的動態功耗往往起主要作用。再者,此處采用了更加先進的工藝,將供電電壓從2.5 V降到1.8 V,輸出電壓擺幅從350 mV降為150mV,從而可以達到更低的功耗和提供更高的傳輸速率。

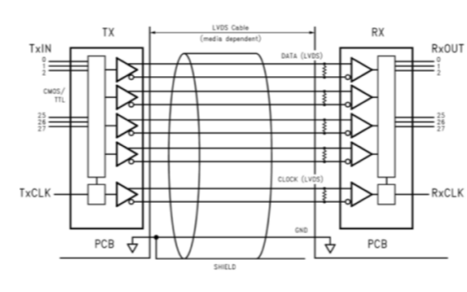

SubLVDS驅動電路

驅動電路是SubLVDS中的重要部分,其功能是實現將輸入的CMOS信號轉換為差分輸出信號,使得在傳輸過程中,抗噪特性更好。

SubLVDS與LVDS的互聯

由于 LVDS 驅動器具有1.2V的典型固定共模電壓輸出和350mV的典型差分電壓擺幅,因此降壓電阻網絡的目標是實現 0.9V 的固定共模電壓以及 150mV 的輸出差分電壓擺幅。使用簡單的電阻網絡連接 LVDS 驅動器和 Sub-LVDS 接收器是支持 Sub-LVDS 接收器所需較低信號電壓電平的可行且經濟的選擇。

Sub-LVDS在7系列FPGA的應用

Sub-LVDS在手冊xapp582和wp393都有描述,直接看圖

選擇DIFF_HSTL_II_F I/O標準用于Sub-LVDS發射機,因為它具有0.9V標稱的共模電壓。DIFF_HSTL_II_F_18的擺幅太大,不能用于subblvds信號。串聯終端放置在線路中,以減少信號擺幅,從而滿足Sub-LVDS規范,同時保持共模在正確的范圍內。

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606026 -

驅動器

+關注

關注

53文章

8272瀏覽量

147070 -

接口

+關注

關注

33文章

8694瀏覽量

151923 -

lvds

+關注

關注

2文章

1045瀏覽量

66011 -

差分信號

+關注

關注

3文章

378瀏覽量

27772

發布評論請先 登錄

相關推薦

基于FPGA的高速LVDS數據傳輸

FPGA編程LVDS信號圖像處理技術

DLPC3433+DLPA2000+DLP3010開發需要DLP3010把每一幀都投射到不同顏色的幕布上

LVDS接口技術在DAC系統中的應用

基于索尼SUB-LVDS并行橋的設計應用

索尼圖像傳感器橋接的解決方案

FPGA上LVDS接收器的速度是否會降低?

UltraScale FPGA中的LVDS上的1000Base-X的介紹

如何解決FPGA引腳與LVDS信號相連時兼容性的問題

LVDS在FPGA中的使用教程之LVDS的介紹

基于Sony Sub-LVDS to MIPI CSI-2 Sensor Bridge圖像傳感器的參考設計

FPGA與LVDS信號兼容性分析方法

基于FPGA的內部LVDS接收器設計

將 LVDS 驅動器與 Sub-LVDS 接收器對接應用說明

Sub-LVDS技術在FPGA上的應用

Sub-LVDS技術在FPGA上的應用

評論