近年來,5G、自動駕駛、超大規(guī)模計算,以及工業(yè)物聯(lián)網(wǎng)等領(lǐng)域呈現(xiàn)出強(qiáng)勁的發(fā)展勢頭。推動這些高速發(fā)展的產(chǎn)業(yè)是AI(人工智能)和ML(機(jī)器學(xué)習(xí))的大規(guī)模應(yīng)用。這種全新的技術(shù)布局不僅加速了更復(fù)雜的計算需求、更強(qiáng)的功能性和更快的數(shù)據(jù)傳輸速度,同時也為芯片研發(fā)人員帶來了前所未有的挑戰(zhàn):即下一代芯片必須更快且更智能。

在當(dāng)前的背景下,由于算力和存儲需求正面臨爆發(fā)式增長,這直接導(dǎo)致推動先進(jìn)SoC(系統(tǒng)級芯片)設(shè)計和驗證的壓力也呈指數(shù)級增加。特別是在集成電路規(guī)模越來越龐大的現(xiàn)實情況下,從設(shè)計到流片(Tape-out)的全流程中,驗證變得尤為重要。這是因為有效的驗證不僅確保了電路在設(shè)計層面的完善,還保證了其在實際應(yīng)用中的穩(wěn)定運(yùn)行,從而降低了修正和調(diào)整的成本和時間。

為了應(yīng)對這一挑戰(zhàn)并縮短驗證周期,硬件仿真成為了超大規(guī)模集成電路驗證的首選工具。它能在最短的時間內(nèi)完成對電路功能的全面驗證,這樣就大大減少了整個設(shè)計到生產(chǎn)的周期。同時,AI/ML算力的飛速增長不僅促進(jìn)了EDA(電子設(shè)計自動化)工具的快速演進(jìn),還與EDA工具結(jié)合,催生了一種“雙向加速”的良性循環(huán)。

去年年底,思爾芯推出了首款國產(chǎn)企業(yè)級硬件仿真系統(tǒng)——芯神鼎OmniArk。值得一提的是,芯神鼎已將AI應(yīng)用于編譯流程中,這無疑推動了芯片設(shè)計領(lǐng)域的發(fā)展。

芯神鼎硬件仿真系統(tǒng)采用了由AI驅(qū)動的智能編譯引擎,該引擎能夠在編譯流程中極大地減少編譯時間和內(nèi)存占用,實現(xiàn)增量編譯,并能智能匹配P&R(布局與布線)策略,從而顯著提高布線的成功率。本文將從多個獨(dú)立模塊的角度,深入探討芯神鼎硬件仿真系統(tǒng)的智能編譯流程。

并行綜合:打破傳統(tǒng)編譯瓶頸

傳統(tǒng)綜合方法充滿了局限性。在集成電路設(shè)計領(lǐng)域,傳統(tǒng)綜合方法主要有兩種:Top-down綜合和Bottom-up綜合。

1.Top-down綜合

該方法對整個設(shè)計進(jìn)行處理,以實現(xiàn)徹底的優(yōu)化。盡管優(yōu)化程度高,但這一方案的綜合時間通常非常長,不適用于迅速變化的項目周期。

2.Bottom-up綜合

此方法首先對底層模型進(jìn)行獨(dú)立綜合,然后逐步并入上層模塊進(jìn)行綜合。雖然這適用于一些包含獨(dú)立IP的復(fù)雜設(shè)計,但其在超大規(guī)模集成電路(VLSI)應(yīng)用中表現(xiàn)出速度和靈活性的明顯不足。

對于超大規(guī)模集成電路,這兩種傳統(tǒng)綜合方法通常成為編譯過程的瓶頸。除了時間效率低下,其對計算資源,特別是內(nèi)存的占用也相當(dāng)巨大。

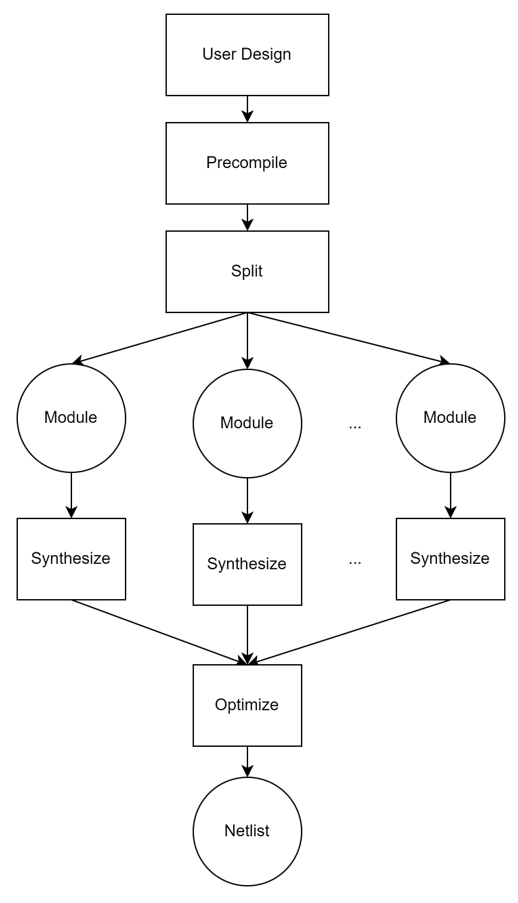

芯神鼎硬件仿真系統(tǒng)對并行綜合進(jìn)行了創(chuàng)新,采用Module-by-Module的綜合方式,徹底改變了這一現(xiàn)狀。首先,芯神鼎針對整個設(shè)計進(jìn)行必要的全局處理和優(yōu)化,例如XMR(Cross-Module Reference)處理。接著,以Module為最小粒度,啟動多核并行綜合過程。

這一步是本系統(tǒng)最大的創(chuàng)新之一,它允許系統(tǒng)充分利用服務(wù)器/集群的并行計算性能。在所有模塊綜合完成之后,系統(tǒng)進(jìn)一步進(jìn)行跨模塊邊界(Cross Module Boundary)邏輯優(yōu)化。此外,芯神鼎能根據(jù)服務(wù)器配置和實際負(fù)載動態(tài)調(diào)節(jié)并行任務(wù)數(shù)量,以實現(xiàn)負(fù)載均衡。

這種并行綜合方法大大加速了超大規(guī)模集成電路設(shè)計的整體綜合效率。實際應(yīng)用中,對于多核NVDLA(NVIDIA Deep Learning Accelerator)這樣的復(fù)雜設(shè)計。

經(jīng)測試,其加速率可以達(dá)到驚人的10~100倍,尤其在多核設(shè)計中表現(xiàn)出色。 通過創(chuàng)新的并行綜合技術(shù),芯神鼎硬件仿真系統(tǒng)成功地突破了傳統(tǒng)綜合方法在時間和資源效率方面的局限,為超大規(guī)模集成電路設(shè)計帶來了前所未有的效率提升。

圖一:并行綜合流程

高效率與高質(zhì)量的智能P&R

在基于硬件仿真的超大規(guī)模設(shè)計流程中,P&R(布局與布線)通常是編譯的最后一步,負(fù)責(zé)生成最終的bitstream文件。雖然現(xiàn)有的編譯工具提供了多種P&R選項,目的是適應(yīng)不同設(shè)計需求和優(yōu)化目標(biāo),但實際情況卻遠(yuǎn)沒有那么簡單。由于各種SoC需求和應(yīng)用場景的多樣性,幾乎沒有一種“通用”的P&R選項組合能適用于所有場景。因此,開發(fā)人員需要根據(jù)特定的設(shè)計需求,手動選擇或調(diào)整P&R選項,以求達(dá)到最佳的設(shè)計輸出。

1. 基于機(jī)器學(xué)習(xí)的智能P&R

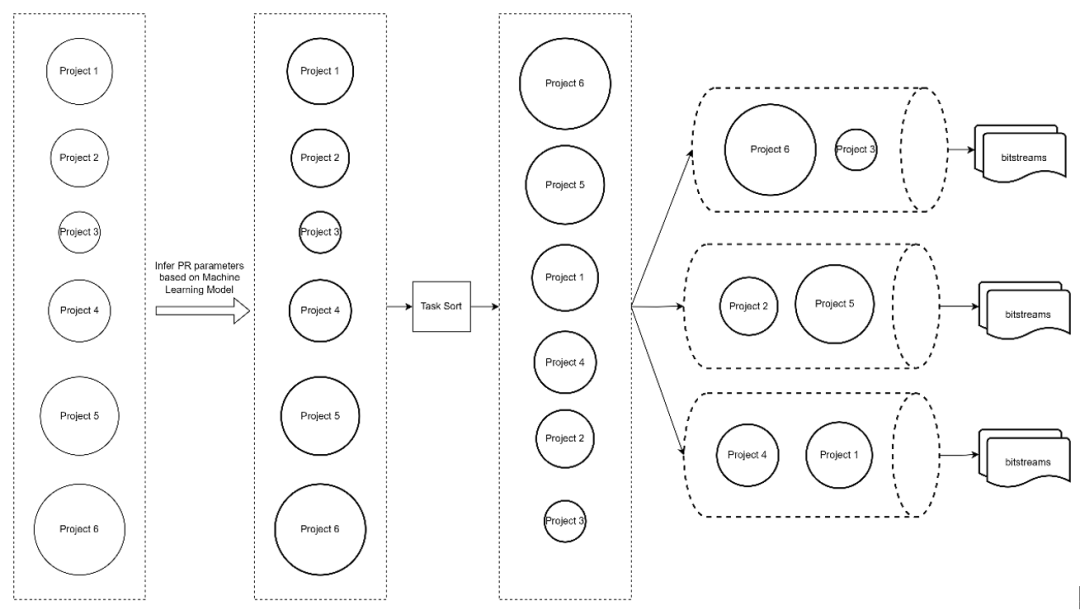

芯神鼎硬件仿真系統(tǒng)突破了這一局限,采用基于機(jī)器學(xué)習(xí)(ML)的智能P&R方法。通過使用大量的實際P&R數(shù)據(jù)進(jìn)行深度訓(xùn)練,系統(tǒng)生成的ML模型能在推理階段輸出最優(yōu)的P&R參數(shù)組合。更值得一提的是,這種基于數(shù)據(jù)驅(qū)動的方法在多個關(guān)鍵性能指標(biāo)上都超過了人工專家的判斷。例如,在布線成功率方面,經(jīng)測試,可以顯著提高布線通過率;同時,P&R所需的總時間也可大幅度減少。

2.優(yōu)化任務(wù)調(diào)度和并行計算

除了使用機(jī)器學(xué)習(xí)進(jìn)行智能選項推薦外,芯神鼎硬件仿真系統(tǒng)還進(jìn)一步優(yōu)化了任務(wù)調(diào)度算法。通過智能任務(wù)調(diào)度,系統(tǒng)能確保在進(jìn)行P&R操作時充分利用編譯服務(wù)器的多核計算能力。具體的并行能力和效率提升取決于編譯服務(wù)器的性能和配置。

通過集成基于機(jī)器學(xué)習(xí)的智能P&R以及高效的任務(wù)調(diào)度和并行計算功能,芯神鼎硬件仿真系統(tǒng)為FPGA設(shè)計提供了一種更高效、更質(zhì)量可控的解決方案。這不僅大幅減少了編譯時間,同時也顯著提升了輸出結(jié)果的質(zhì)量。

圖二:任務(wù)調(diào)度和并行計算流程

增量編譯

在超大規(guī)模集成電路(VLSI)的設(shè)計過程中,即使進(jìn)行了多方面的編譯流程優(yōu)化,編譯時間依然可能成為項目進(jìn)度的瓶頸。更進(jìn)一步地說,對于那些已經(jīng)編譯過但需做細(xì)微修改的工程,每次都進(jìn)行全量編譯會大大延長開發(fā)周期,耗費(fèi)人力和計算資源。

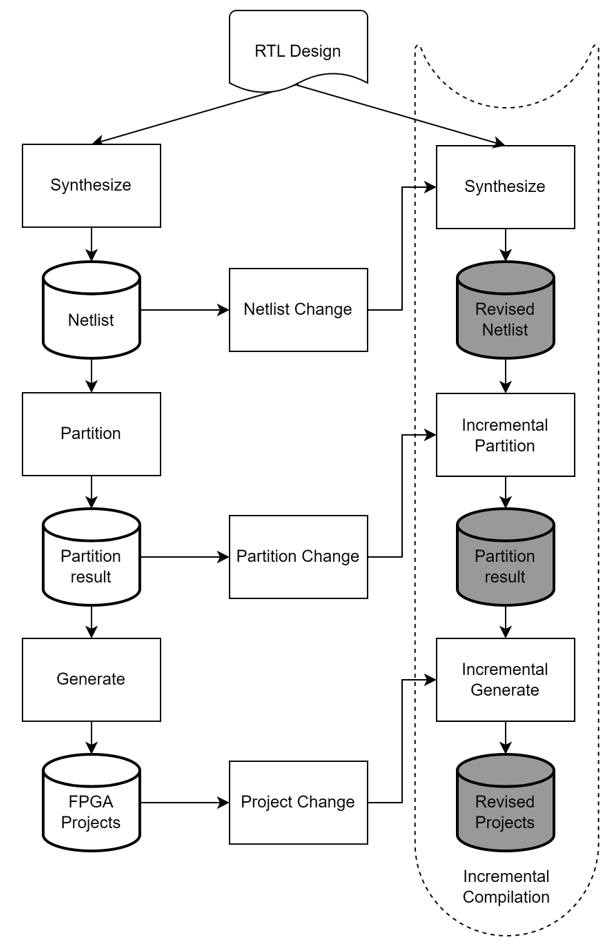

增量編譯(Incremental Compilation)是一種編程優(yōu)化策略,用于加快編譯過程。在一個大型或復(fù)雜的代碼基礎(chǔ)上,每次進(jìn)行全量編譯(即重新編譯整個代碼基礎(chǔ))通常會消耗大量時間和計算資源。增量編譯的目標(biāo)是只重新編譯自上次編譯后發(fā)生變化或被影響的代碼部分,而不是整個代碼庫。

增量編譯系統(tǒng)首先會跟蹤代碼中各模塊、函數(shù)或文件的依賴關(guān)系。當(dāng)某一部分代碼發(fā)生改動后,編譯系統(tǒng)會識別這一改動,并查找所有依賴于該部分的其他代碼。只有被改動的代碼和依賴于它的代碼會被重新編譯。其它未改動和不受影響的代碼則不需要重新編譯。重新編譯的代碼會與舊的編譯結(jié)果合并,生成一個更新的可執(zhí)行文件或庫。對于代碼庫非常大的項目,增量編譯幾乎是必需的。

芯神鼎硬件仿真系統(tǒng)便采用了這種增量編譯策略。它采用了一種先進(jìn)的增量編譯引擎,該引擎涵蓋了綜合模塊、Partition模塊以及工程生成模塊等關(guān)鍵部分。這些模塊都集成了增量編譯技術(shù),可以在二次編譯過程中智能感知用戶所做的任何修改。這種自動感知機(jī)制極大地減少了重新編譯所需的計算量,因為它只針對修改過的部分進(jìn)行編譯,而非整個設(shè)計。這樣不僅大幅度縮短了編譯時間,還優(yōu)化了資源使用效率。

圖三:增量編譯流程

總結(jié)

AI+EDA的結(jié)合代表了一次跨越式的技術(shù)進(jìn)步,它不僅有望延續(xù)并拓展摩爾定律的生命周期,還能顯著節(jié)約研發(fā)時間和資本投入,提升行業(yè)整體競爭力。進(jìn)一步地,這一結(jié)合還為全球芯片設(shè)計領(lǐng)域開創(chuàng)了全新的可能性,比如通過機(jī)器學(xué)習(xí)算法優(yōu)化設(shè)計流程,從而縮短產(chǎn)品上市時間,或者在更短的時間內(nèi)完成更為復(fù)雜的設(shè)計任務(wù)。

芯神鼎硬件仿真系統(tǒng)集多種創(chuàng)新技術(shù)于一身,如并行綜合、智能P&R和增量編譯等模塊,不僅大幅度縮短了編譯時間,還提高了整體編譯質(zhì)量。這些模塊都運(yùn)用了我們自主研發(fā)的先進(jìn)技術(shù),為客戶在超大規(guī)模集成電路驗證方面提供了強(qiáng)有力的支持。除了應(yīng)對現(xiàn)有的編譯挑戰(zhàn),我們的解決方案還具備極強(qiáng)的可擴(kuò)展性,能夠適應(yīng)未來更高復(fù)雜度的工程需求。

通過持續(xù)的研發(fā)和創(chuàng)新,芯神鼎硬件仿真系統(tǒng)有望成為推動整個集成電路設(shè)計行業(yè)進(jìn)入新“智”元的重要力量,開啟一個全新的、以數(shù)據(jù)和算法為驅(qū)動的芯片設(shè)計時代。

審核編輯:劉清

-

EDA工具

+關(guān)注

關(guān)注

4文章

268瀏覽量

31937 -

SoC芯片

+關(guān)注

關(guān)注

1文章

617瀏覽量

35042 -

人工智能

+關(guān)注

關(guān)注

1796文章

47683瀏覽量

240301 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8441瀏覽量

133087 -

自動駕駛

+關(guān)注

關(guān)注

785文章

13932瀏覽量

167012

原文標(biāo)題:AI驅(qū)動的國產(chǎn)硬件仿真芯神鼎如何加速超大規(guī)模芯片設(shè)計

文章出處:【微信號:S2C_Corporation,微信公眾號:思爾芯S2C】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AI時代下芯片復(fù)雜度飆升,思爾芯國產(chǎn)硬件仿真加速芯片創(chuàng)新

ICCAD 2024|摩爾定律在AI時代不斷蛻變,思爾芯探討國產(chǎn)EDA發(fā)展新路徑

“2025 IC風(fēng)云榜”揭曉,思爾芯獲“年度最佳解決方案獎”

思爾芯加入甲辰計劃,共推RISC-V生態(tài)

思爾芯受邀參加CCF Chip 2024大會

思爾芯亮相CCF Chip 2024,展示數(shù)字前端EDA技術(shù)

思爾芯亮相CCF Chip 2024,展示創(chuàng)新EDA技術(shù)與產(chǎn)學(xué)研合作

思爾芯創(chuàng)新實踐成果通過上海市高新技術(shù)成果轉(zhuǎn)化項目認(rèn)定

思爾芯芯神瞳原型驗證系統(tǒng)通過上海市高新技術(shù)成果轉(zhuǎn)化項目認(rèn)定

思爾芯即將亮相CCF Chip 2024 ,共推智算芯未來

思爾芯亮相DAC 2024:應(yīng)用為導(dǎo)向,從“芯”出發(fā)

相約DAC 2024!思爾芯攜帶多款數(shù)字前端EDA產(chǎn)品亮相,與您不見不散

Wi-Fi 7射頻IP驗證系統(tǒng)發(fā)布!思爾芯EDA助力Sirius Wireless加速芯片設(shè)計

思爾芯亮相第二屆玄鐵RISC-V生態(tài)大會

演講預(yù)告|思爾芯邀您共聚中國IC領(lǐng)袖峰會,一起探索“芯”未來

思爾芯OmniArk推動芯片設(shè)計領(lǐng)域的發(fā)展

思爾芯OmniArk推動芯片設(shè)計領(lǐng)域的發(fā)展

評論