在設計周期中,您可保留多個版本的工程,這些工程使用相同的 IP 和相同的配置。重新運行整個工程會導致每次都要重新生成 IP,很費時間。

在 Vivado工程設置中,您的 IP 存儲庫允許您將自己的 IP 添加到 Vivado IP 目錄中,搭配遠程 IP 高速緩存一起使用時,即可顯著縮短編譯時間。這篇博文解釋了具體設置方法。

在開始下述步驟前,最好先創建格式化目錄結構:

注釋:此結構中應有一個頂層的父目錄,例如,iprepo,然后是子目錄;每個 IP 一個子目錄,還有一個子目錄對應由 Vivado 創建的遠程 IP 高速緩存。

此 IP 必須位于遠程 IP 高速緩存的同級目錄內。這是因為 Vivado 遇到component.xml文件時,就會停止搜索 IP 高速緩存的目錄結構,而此文件始終與封裝的 IP 目錄一起生成。

第 1 步:將所有必需的源文件封裝為單個 IP

一般,IP 封裝步驟包括以下 3 個步驟,并且封裝的 IP 文件一起接受管理。

1. 將 RTL 添加到 Vivado 工程中,并對其進行綜合,驗證其完整性 。

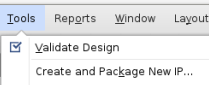

2.使用 Vivado 中的“Tools”(工具)選項對 RTL 進行封裝:

3. 確保基于ip_repo目錄中的 IP 名稱選擇一個目錄。

第 2 步:驗證并生成所有遠程高速緩存文件

在這一步中,您需要從已封裝的 IP 文件夾中例化已封裝的 IP,但不含任何邏輯連接。隨后,為存儲庫中的不同 IP 配置生成網表。

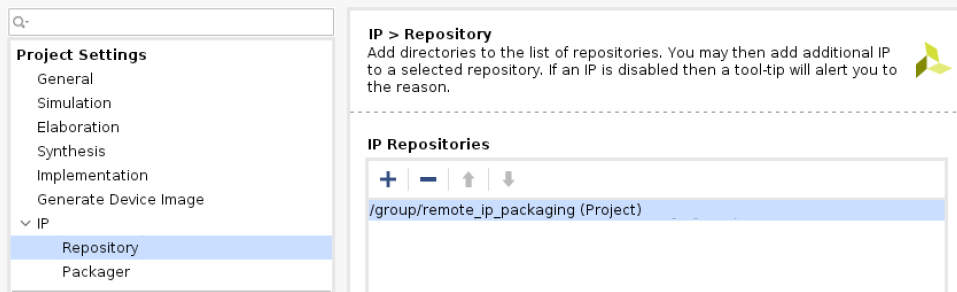

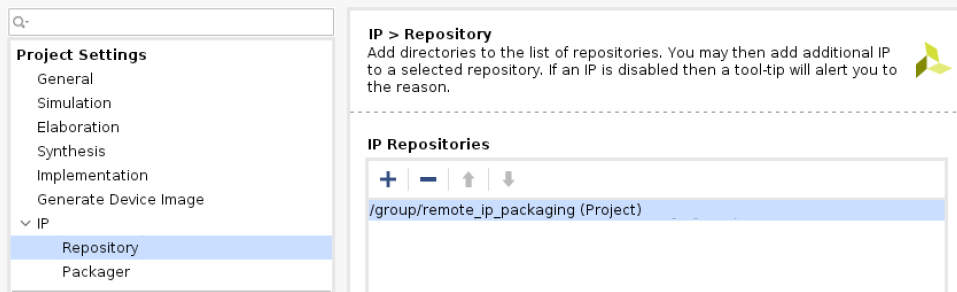

1.通過工程設置將新創建的用戶 IP 存儲庫添加到 Vivado 工程中:

2. 將該 IP 添加到新創建的 IP integrator 塊設計中。 您可選中 IP 并按下 Ctrl-T 鍵,輕松將此 IP 的所有端口連接到外部端口。或者,您可將其添加到設計中。

3. 如果您的 IP 可配置,請添加多項配置,以便在 IP 高速緩存中填充更多通用配置。

注釋:應用此變通方法時存在諸多限制,只要與用戶 IP 設置存在任何不匹配,都可能導致重新生成已例化的 IP。

請確保軟件構建相匹配

請確保 device part/speed_grade/board name 相匹配

確保 IP 設置與生成此 IP 時的 IP 緩存文件相匹配。鑒于有時參數傳播可能導致覆蓋用戶 IP 上的部分參數,例如,從上游傳播的時鐘頻率會被覆蓋,因此應執行檢查。

4. 確認設計并審查任何“Error”(錯誤)和“Critical Warning”(嚴重警告)

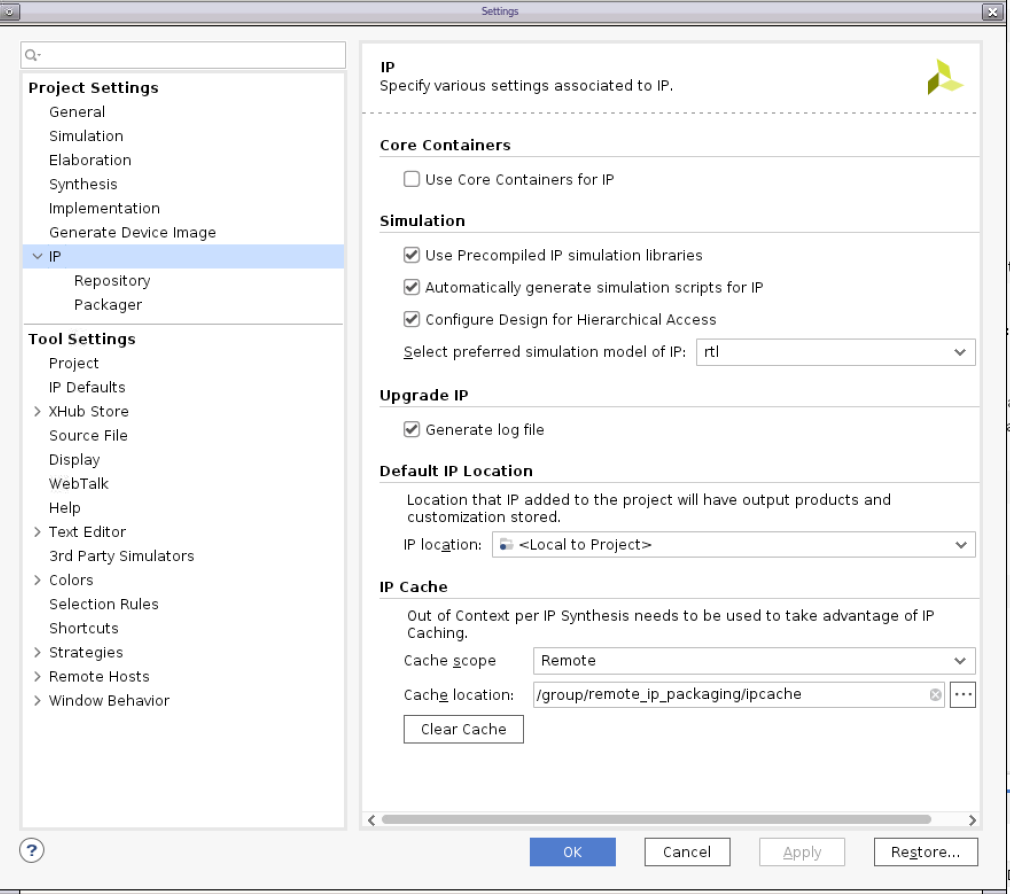

5. 生成設計之前,在 IP Repository 目錄下指定遠程 IP 存儲庫,例如,/iprepo/ipcache:

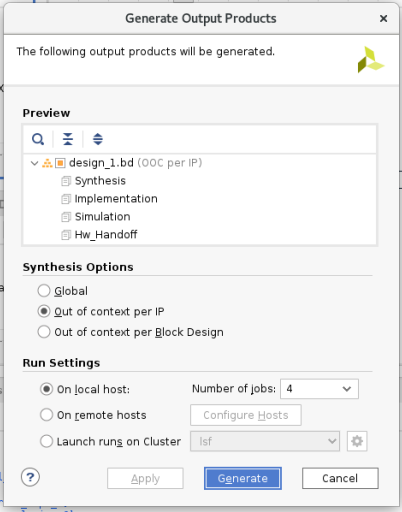

6.使用默認“Out of context per IP”(非關聯按 IP)選項生成塊設計:

7.生成完成后,應顯示已填充的遠程 IP 高速緩存。

其中將生成新的目錄,并以散列代碼作為目錄名稱。

第 3 步:在正式設計中例化 IP,并復用遠程 IP 存儲庫

在工程中使用用戶 IP 存儲庫和 IP 高速緩存:

1.現在,您只需要指向頂層的 IP 存儲庫目錄,即可同時使用用戶 IP 和遠程 IP 高速緩存。

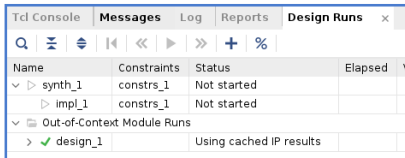

2. 生成設計時,如果使用的器件/開發板和 IP 配置選項未更改,就不會發生重新綜合,并且 IP 運行狀態將顯示“Using cached IP results”(使用緩存的 IP 結果):

建議的版本管理:

請通過腳本封裝用戶 IP,或創建獨立工程來封裝 IP。

創建獨立工程來例化包含所有不同配置的用戶 IP,并生成此 IP,同時導出高速緩存。

在正式工程中采用此 IP,并遵循本文檔中的指南進行操作。

審核編輯:劉清

-

存儲器

+關注

關注

38文章

7528瀏覽量

164345 -

RTL

+關注

關注

1文章

385瀏覽量

59951 -

Vivado

+關注

關注

19文章

815瀏覽量

66890

原文標題:開發者分享|節省編譯時間系列-為多個 Vivado? 工程復用遠程 IP 高速緩存

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MRAM高速緩存的組成

高速緩存/海量緩存的設計實現

怎么利用異步FIFO和PLL結構來實現高速緩存?

怎樣去實現一種基于DSP和ADC技術高速緩存和海量緩存?

高速緩存Cache介紹

高速緩存(Cache),高速緩存(Cache)原理是什么?

AN1600 - 在PIC32MZ器件上使用L1高速緩存

使用MPLAB Harmony v3基于PIC32MZ MCU在運行時使用高速緩存維護操作處理高速緩存一致性問題

為多個Vivado?工程復用遠程IP高速緩存

為多個Vivado?工程復用遠程IP高速緩存

評論