在項(xiàng)目初期,在使用FPGA工具quartus或者vivado生成版本燒入開發(fā)板進(jìn)行調(diào)試時(shí)(DC開啟優(yōu)化選項(xiàng)后同樣會(huì)優(yōu)化掉寄存器),我們有時(shí)會(huì)發(fā)現(xiàn)部分寄存器被優(yōu)化掉了,今天簡(jiǎn)單聊聊被優(yōu)化的幾種情況。

1、寄存器被優(yōu)化的原因

目前鴿子發(fā)現(xiàn)寄存器被優(yōu)化的原因主要有兩種:

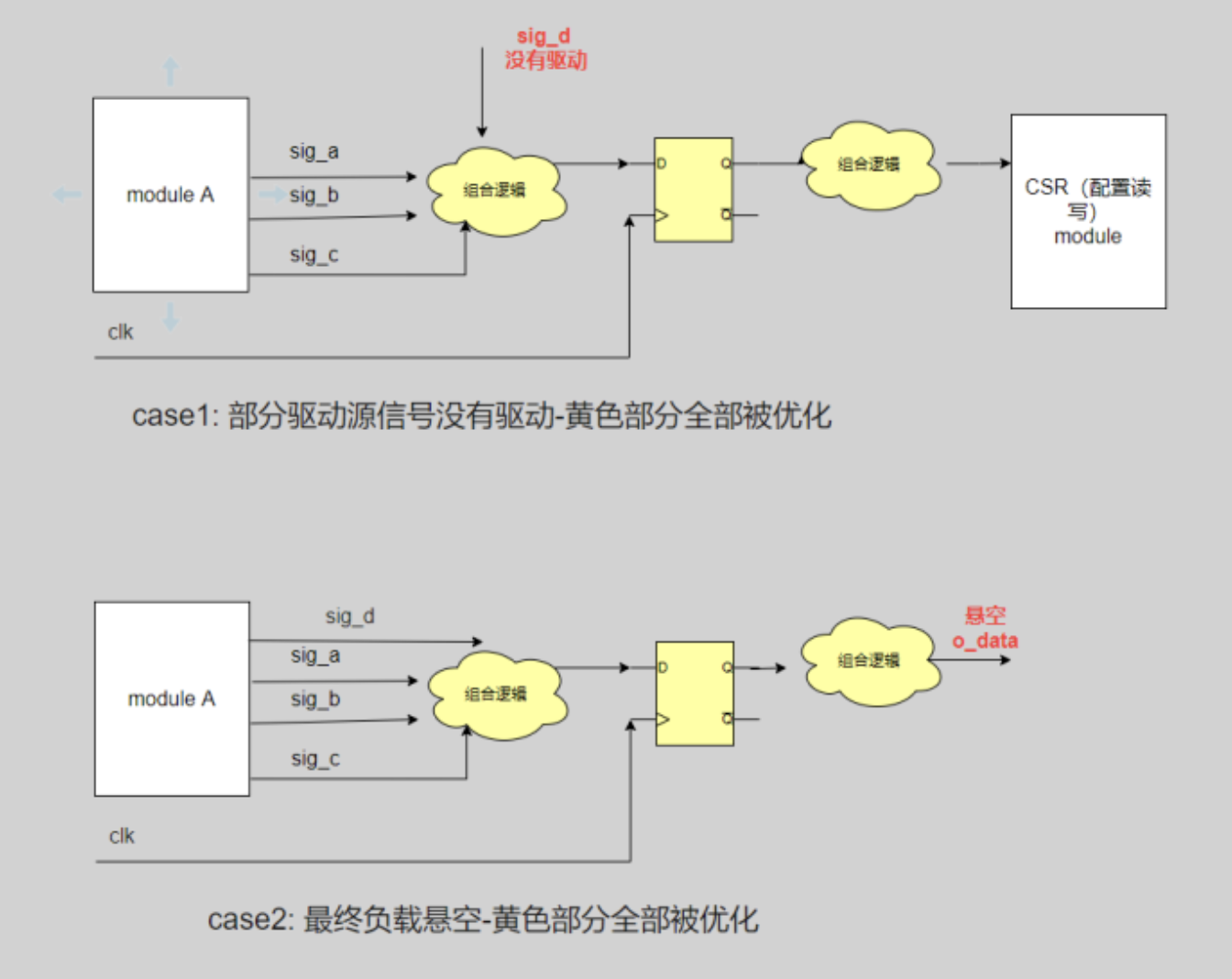

1)驅(qū)動(dòng)寄存器的信號(hào)沒有驅(qū)動(dòng)源

a. 至少有一個(gè)信號(hào)沒有驅(qū)動(dòng)源,也可能是多個(gè)

2)寄存器負(fù)載是懸空的,包含如下場(chǎng)景

a. 寄存器的唯一負(fù)載時(shí)懸空

b. 寄存器的所有負(fù)載均懸空

部分場(chǎng)景下被優(yōu)化的問題很好排查,有些場(chǎng)景排查會(huì)比較麻煩,僅僅從信號(hào)連線上看都是正常的,無法通過肉眼快速發(fā)現(xiàn)問題,這時(shí)候需要去看綜合報(bào)告,找到問題的源頭。

2、案例--大量寄存器被優(yōu)化

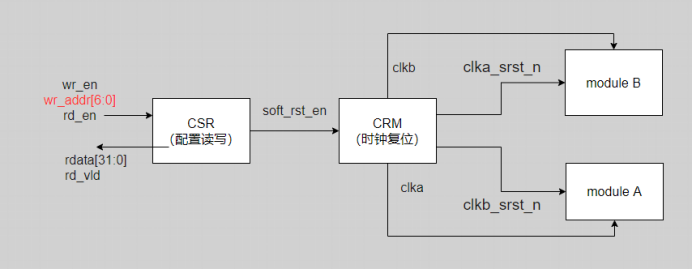

如下圖所示,crm是復(fù)制產(chǎn)生時(shí)鐘復(fù)位的模塊,其中輸出clka/clka_rst_n給模塊a,其中輸出clkb/clkb_rst_n給模塊b。Soft_reset_n是clka_rst_n和clkb_rst_n的源頭之一。Soft_reset_n為0,則clka_rst_n/clkb_rst_n為0,處于復(fù)制狀態(tài)。Soft_reset_n是配置讀寫模塊CSR的一個(gè)可配置寄存器,其內(nèi)部偏移地址為0x60。

通過quartus/vivado查看網(wǎng)表結(jié)構(gòu)和資源利用率,我們發(fā)現(xiàn)模塊A和模塊B大量資源被優(yōu)化,不符合常理。經(jīng)過檢測(cè)發(fā)現(xiàn),所有信號(hào)連接均正常,沒有懸空,所有信號(hào)均存在負(fù)載。

經(jīng)過反復(fù)排查后發(fā)現(xiàn),CSR模塊被手動(dòng)添加的Soft_reset_n寄存器地址分配在0x60,而CSR入口wr_addr[5:0]只有6bit,只能訪問0x40以內(nèi)的地址范圍,因此Soft_reset_n在實(shí)際網(wǎng)表中是不存在的,導(dǎo)致clka_rst_n/clkb_rst_n都沒有驅(qū)動(dòng)源,因此模塊A和模塊B大量資源被優(yōu)化。

3、推薦檢查方法

在進(jìn)行FPGA版本調(diào)試之前,首先進(jìn)行spyglass lint檢查 或者檢查quartus/vivado產(chǎn)生的綜合報(bào)告,檢查是否存在如下warning:

信號(hào)沒有驅(qū)動(dòng)

信號(hào)懸空

把這些warning確認(rèn)完后再進(jìn)行版本調(diào)試。

4、簡(jiǎn)單的規(guī)律

大量模塊邏輯被優(yōu)化,重點(diǎn)看時(shí)鐘復(fù)位

少量模塊邏輯被優(yōu)化,重點(diǎn)看資源獨(dú)享的驅(qū)動(dòng)信號(hào)

End

原審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605987 -

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121155 -

CSR

+關(guān)注

關(guān)注

3文章

118瀏覽量

69724 -

優(yōu)化

+關(guān)注

關(guān)注

0文章

220瀏覽量

23959 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66886

原文標(biāo)題:啥?我的寄存器被被優(yōu)化掉了!

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

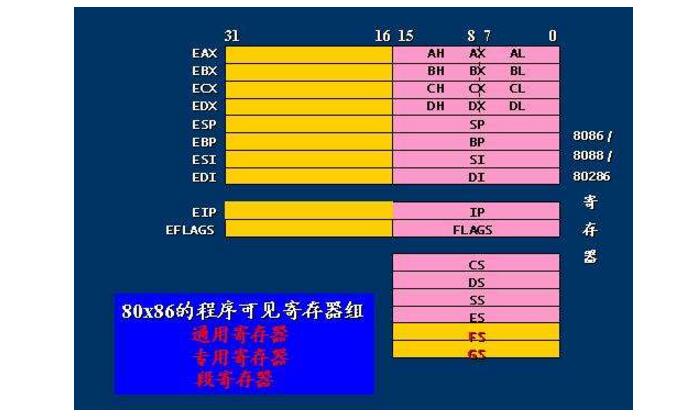

寄存器是什么?怎么操作寄存器點(diǎn)亮LED燈?

聊聊寄存器被優(yōu)化的2種情況

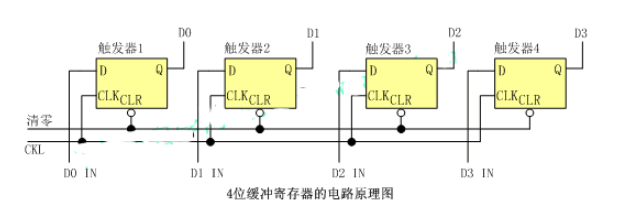

寄存器與移位寄存器

數(shù)據(jù)寄存器,數(shù)據(jù)寄存器是什么意思

基于FPGA的可變長(zhǎng)度移位寄存器優(yōu)化設(shè)計(jì)

淺談ARM寄存器組織

為什么寄存器比內(nèi)存快_原因是這個(gè)

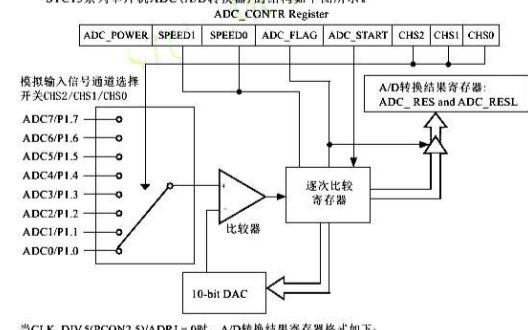

AD轉(zhuǎn)換寄存器設(shè)置

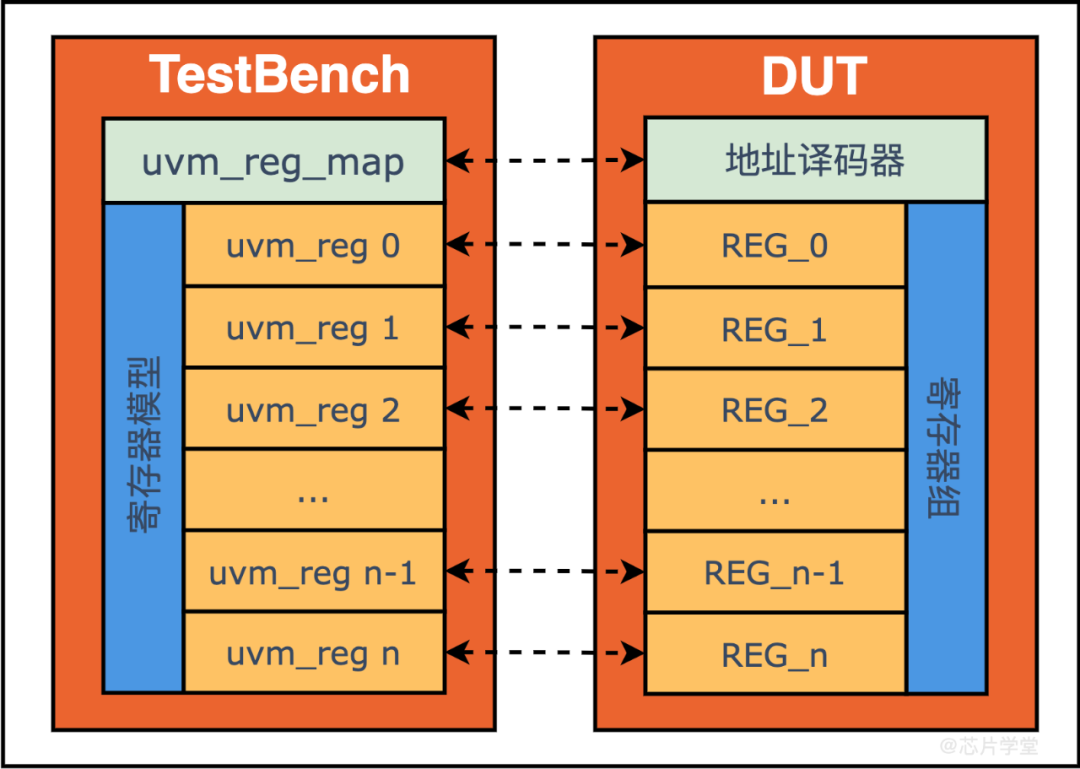

簡(jiǎn)述RAL寄存器模型基礎(chǔ)

淺談寄存器被優(yōu)化的原因

淺談寄存器被優(yōu)化的原因

評(píng)論