1、RR輪詢調度?

在設計中,我們經常會用到RR(Round-Robin,RR)輪詢調度,用于保證在一個時間段內的多個請求信號都能得到公平響應。

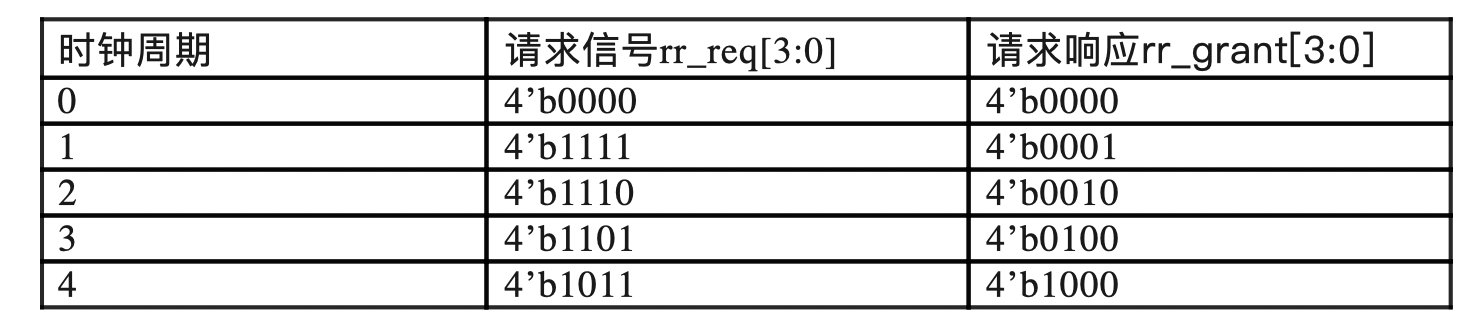

如下所示:輸入rr_req[3:0]為4個請求信號,輸出rr_grant[3:0]為4請求信號對應的4個響應信號:rr_req[n]表示第n請求申請響應,rr_grant[n]為1表示第n個請求被響應。

如表所示,T1周期,所有請求均有效,首先響應低bit的請求,所以rr_grant[0]=1。

T3周期,請求rr_req[0]有效,但是在T2時刻中被響應(rr_grant[1]=1),因此此次不再響應,而是響應rr_req[2],所以rr_grant[2]=1.

2、Verilog是如何實現RR輪詢調度的?

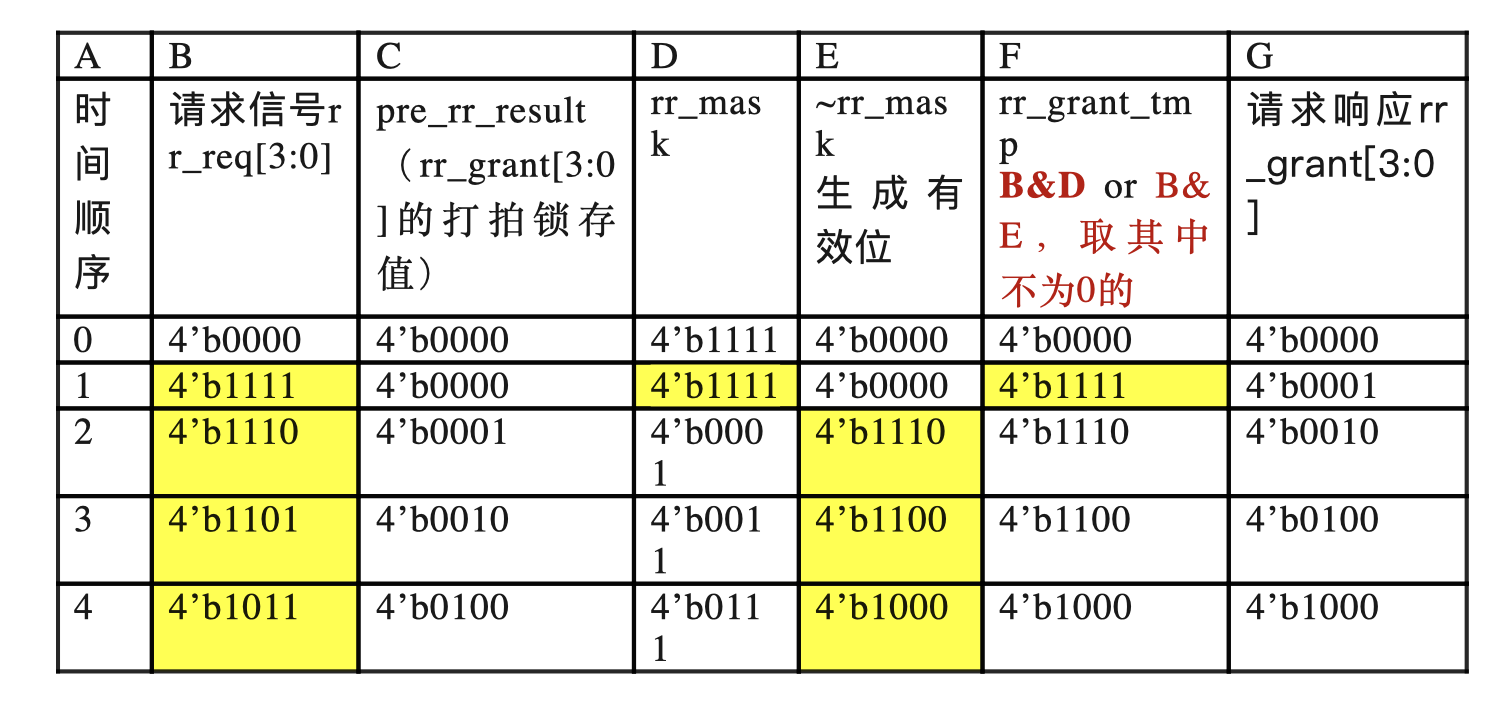

在verilog實現中,僅僅采用簡單的組合邏輯和寄存器就可以實現rr輪詢調度,不需要狀態機等設計。

基本原理是鎖存上一次輸出請求響應rr_grant[3:0],并且生成相應的有效位rr_mask[3:0],從(rr_valid[3:0]&rr_mask[3:0]) 和 rr_valid[3:0]&(~rr_mask[3:0]) 選取不為0的作為獲得rr_grant_tmp,rr_grant_tmp再經過組合邏輯并且取最低有效位。此處mask中1表示請求有效。

B列:為請求信號rr_req[3:0]

C列:pre_rr_result 為模塊內部鎖存的上一拍rr_grant[3:0],即寄存器鎖存打拍

D列:rr_mask為pre_rr_result經過組合邏輯得到的掩碼,rr_mask= {pre_rr_result[2:0],pre_rr_result[3]}-1’b1

E列: rr_mask為pre_rr_result經過組合邏輯得到的掩碼,rr_mask= ( {pre_rr_result[2:0],pre_rr_result[3]}-1’b1)

F列:rr_grant_tmp為B&D or B&E,取其中不為0的

G列:rr_grant_tmp經過組合邏輯輸出最低有效位:(~rr_grant_tmp+1’b1)&rr_grant_tmp

-

寄存器

+關注

關注

31文章

5363瀏覽量

121199 -

IC設計

+關注

關注

38文章

1302瀏覽量

104292 -

鎖存器

+關注

關注

8文章

908瀏覽量

41645 -

狀態機

+關注

關注

2文章

492瀏覽量

27654 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8309

發布評論請先 登錄

相關推薦

IC設計:Verilog是如何實現RR輪詢調度的?

核心路由器的多端口線卡調度

Linux系統調度是實現特性的關鍵部分

請問FreeRTOS是如何實現調度的?

Microchip單片機固定時間片輪詢調度匯編代碼 精選資料分享

Microchip單片機固定時間片輪詢調度匯編代碼 精選資料推薦

STM32是怎樣去實現軟件時間片調度的

基于FPGA的輪詢合路的設計和實現

基于SDH芯片的S19202的輪詢合路的設計

基于動態分組的M2M上行優先級調度算法綜述

Microchip單片機固定時間片輪詢調度匯編代碼

STM32 操作系統內核調度原理與實現(1):輪詢系統,前后臺系統與多線程系統

RR輪詢調度?Verilog是如何實現RR輪詢調度的?

RR輪詢調度?Verilog是如何實現RR輪詢調度的?

評論