引言

前面講完了編碼器,其實(shí)不知不覺(jué)地,也順便把譯碼器也講了,畢竟,二者是一個(gè)相反操作的過(guò)程,類(lèi)似于加減,前進(jìn)與后退,調(diào)制與解調(diào),F(xiàn)FT 和 IFFT 等等。

譯碼器的邏輯功能就是將每一個(gè)輸入的二進(jìn)制代碼轉(zhuǎn)為對(duì)應(yīng)的多輸出高、低電平信號(hào)或另外一個(gè)代碼,是編碼器的逆運(yùn)算,譯碼器又可以分為變量譯碼和顯示譯碼。變量譯碼器一般是一種較少輸入變?yōu)檩^多輸出的器件,常見(jiàn)的有 N 線 - 2^N 線譯碼和 8421BCD 碼譯碼兩類(lèi);顯示譯碼器用來(lái)將二進(jìn)制數(shù)轉(zhuǎn)換成對(duì)應(yīng)的七段碼,一般其可分為驅(qū)動(dòng) LED 和驅(qū)動(dòng) LCD 兩類(lèi)。

一、變量譯碼器的 Verilog 代碼實(shí)現(xiàn)和 RTL 電路實(shí)現(xiàn)

module Decoders(

input wire [2:0] b, // 輸入信號(hào)_未譯碼

output reg [7:0] d // 輸出信號(hào)_已譯碼

);

reg d = 8'b0000_0000;

always @ ( b ) begin

case ( b )

3'b000 : d <= 8'b0000_0001;

3'b001 : d <= 8'b0000_0010;

3'b010 : d <= 8'b0000_0100;

3'b100 : d <= 8'b0001_0000;

3'b101 : d <= 8'b0010_0000;

3'b110 : d <= 8'b0100_0000;

3'b111 : d <= 8'b1000_0000;

default: d <= 8'b0000_0000;

endcase

end

endmodule

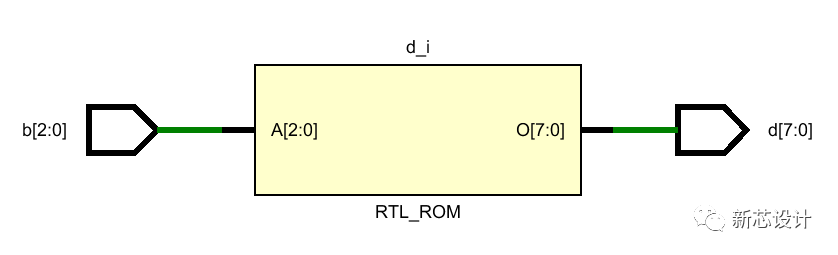

這是一個(gè) 3 線 ? 8 線變量譯碼器,基于查找表 LUT(Look Up Table)的方式實(shí)現(xiàn)的一個(gè)電路,其 RTL 電路圖如下所示:

變量譯碼器的 RTL 電路圖

這里的譯碼器,其實(shí)就只是基于 LUT 的譯碼器,是最簡(jiǎn)單的,并沒(méi)有經(jīng)過(guò)復(fù)雜的運(yùn)算操作,其思想只是簡(jiǎn)單地輸入地址,然后輸入地址所在的數(shù)據(jù)即可。

譯碼是編碼的逆過(guò)程,在編碼時(shí),每一種二進(jìn)制代碼,都賦予了特定的含義,即都表示了一個(gè)確定的信號(hào)或者對(duì)象;把代碼狀態(tài)的特定含義 “翻譯” 出來(lái)的過(guò)程叫做譯碼,實(shí)現(xiàn)譯碼操作的電路稱(chēng)為譯碼器;或者說(shuō),譯碼器是可以將輸入二進(jìn)制代碼的狀態(tài)翻譯成輸出信號(hào),以表示其原來(lái)含義的電路。

-

二進(jìn)制

+關(guān)注

關(guān)注

2文章

796瀏覽量

41756 -

LED驅(qū)動(dòng)

+關(guān)注

關(guān)注

72文章

1007瀏覽量

138178 -

譯碼器

+關(guān)注

關(guān)注

4文章

312瀏覽量

50463 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59948 -

Verilog設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

20瀏覽量

6545

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

40. 譯碼器 (5)#譯碼器 #數(shù)字電路

數(shù)字電子電路技術(shù)--譯碼器及其應(yīng)用

數(shù)字電路設(shè)計(jì)的基本方法有哪些

譯碼器定義

譯碼器

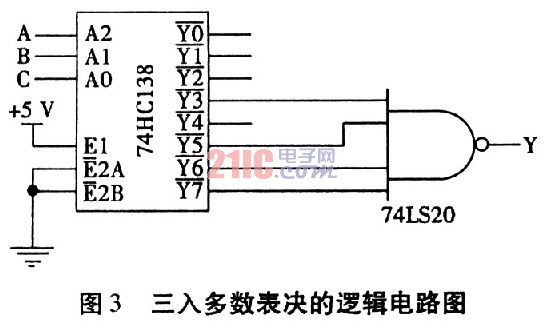

74HCl38譯碼器在數(shù)字電路設(shè)計(jì)中的應(yīng)用

數(shù)字電路中顯示譯碼器設(shè)計(jì)的分析

譯碼器的分類(lèi)和應(yīng)用

Multisim14.0數(shù)字電路譯碼器實(shí)現(xiàn)函數(shù)的工程文件免費(fèi)下載

單片機(jī) 什么是編碼器?什么是譯碼器?

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(jì)(5)譯碼器

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(jì)(5)譯碼器

評(píng)論