看到一個交流群在討論關于【關于STM32中斷優先級的話題】,其中就有小伙伴提到:為什么有些STM32中斷沒有【子優先級】?

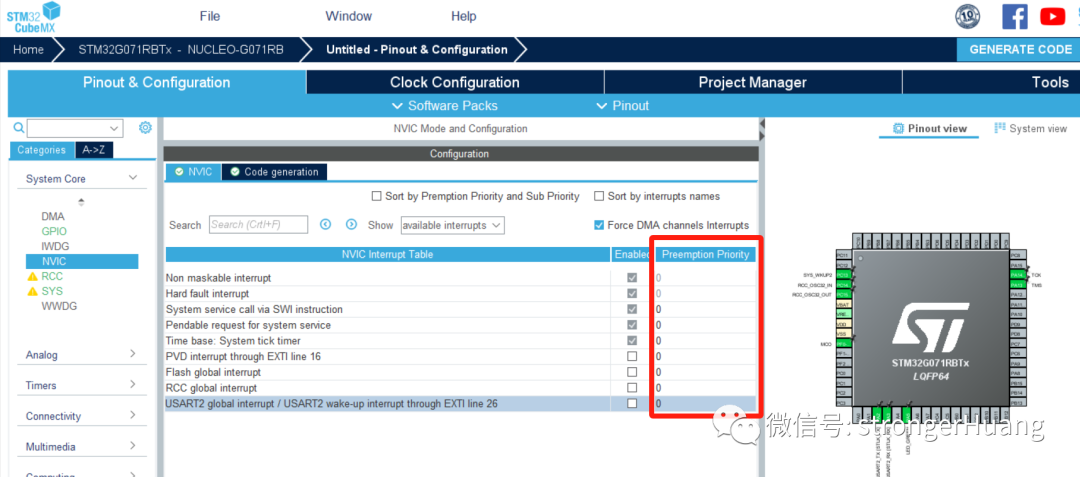

比如,有時候你在使用STM32CubeMX配置時,你會發現只有Preemption Priority【搶占優先級】,而沒有Sub Priority【次優先級】:

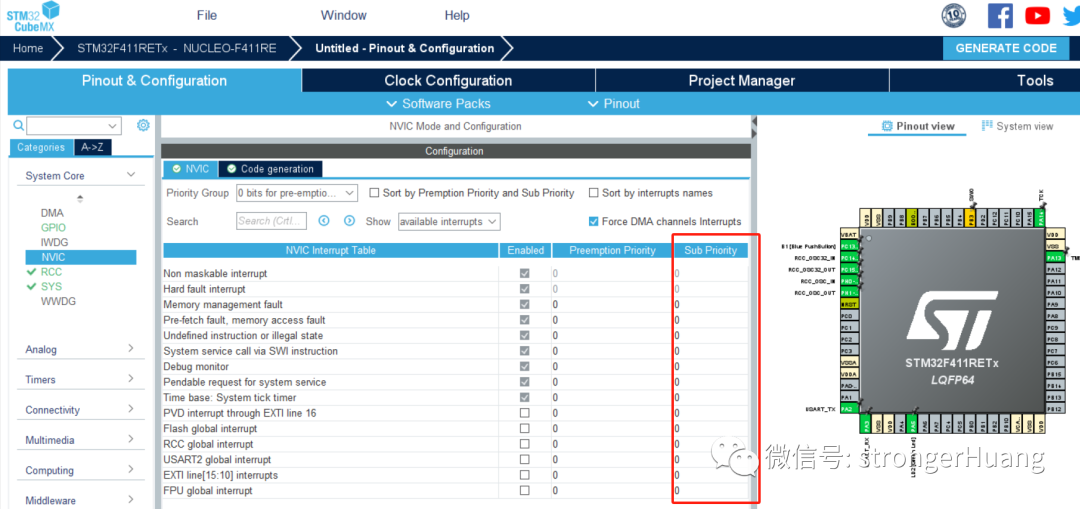

然而,有時候你會發現又有Sub Priority【次優先級】:

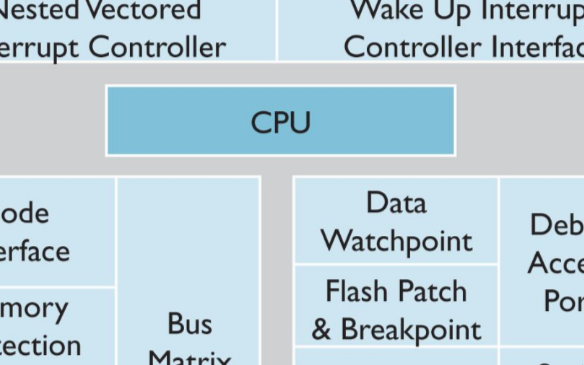

這個問題就牽涉到STM32,準確的來說的是 Cortex-M NVIC嵌套向量中斷控制器的問題。

關于Cortex-M的NVIC

NVIC:Nested Vectored Interrupt Controller,嵌套向量中斷控制器。

在每個Cortex-M內核中都有這么一個NVIC嵌套向量中斷控制器,當MCU使用的內核不同,其中的NVIC也可能不同。

比如,Cortex-M0和Cortex-M3內核中NVIC功能就不同。

其中,中斷優先級分組功能就不同。

Cortex-M0的NVIC沒有優先級分組功能,Cortex-M3、 M4、M7有分組功能。 ?

?

所以,你在使用STM32CubeMX配置時,M0/M0+內核的STM32是沒有【次優先級】那個選項的。

Cortex-M0包含STM32F0、L0、G0等處理器。

對底層感興趣的朋友可以繼續往下看。

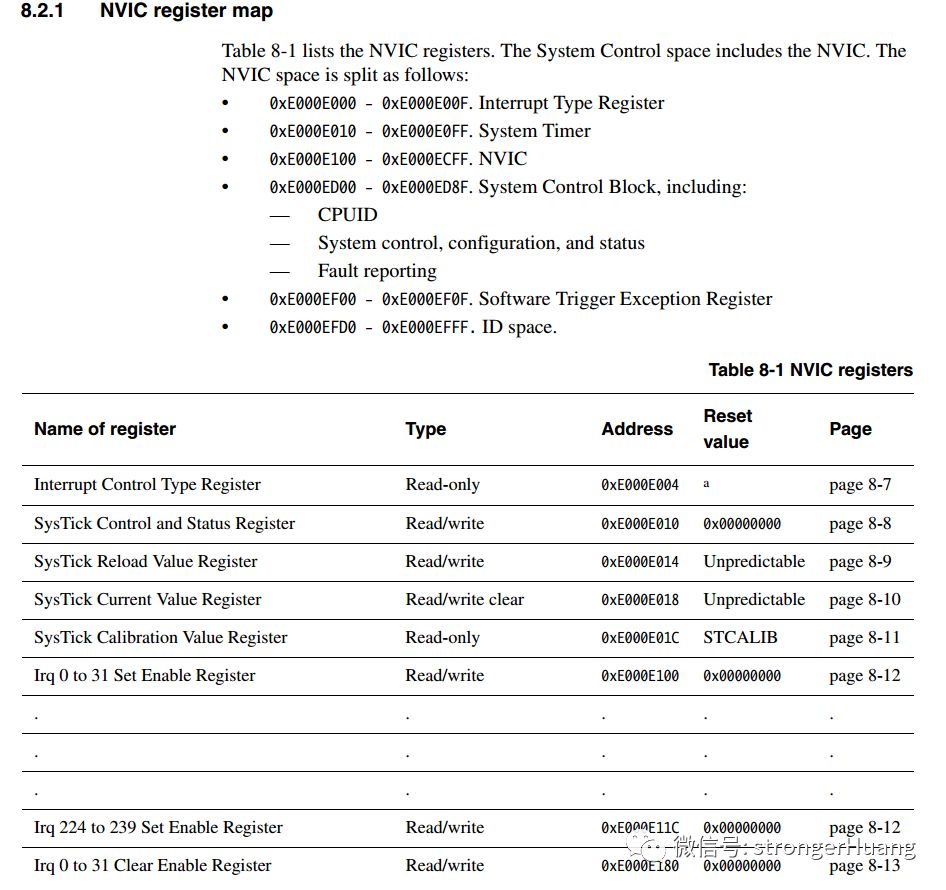

NVIC寄存器

NVIC寄存器,需查看對應的內核(Cortex-M)手冊,在ARM官網能找到( M3也有對應的中文翻譯版,大家可以自己網上搜索)。

內核中的寄存器和我們STM32參考手冊中寄存器一樣,不同的Bit位代表含義不同。

但是,對于NVIC來說,由于包含眾多優先級相關配置,寄存器數量相對較多(NVIC寄存器族)。 ? ?

? ?

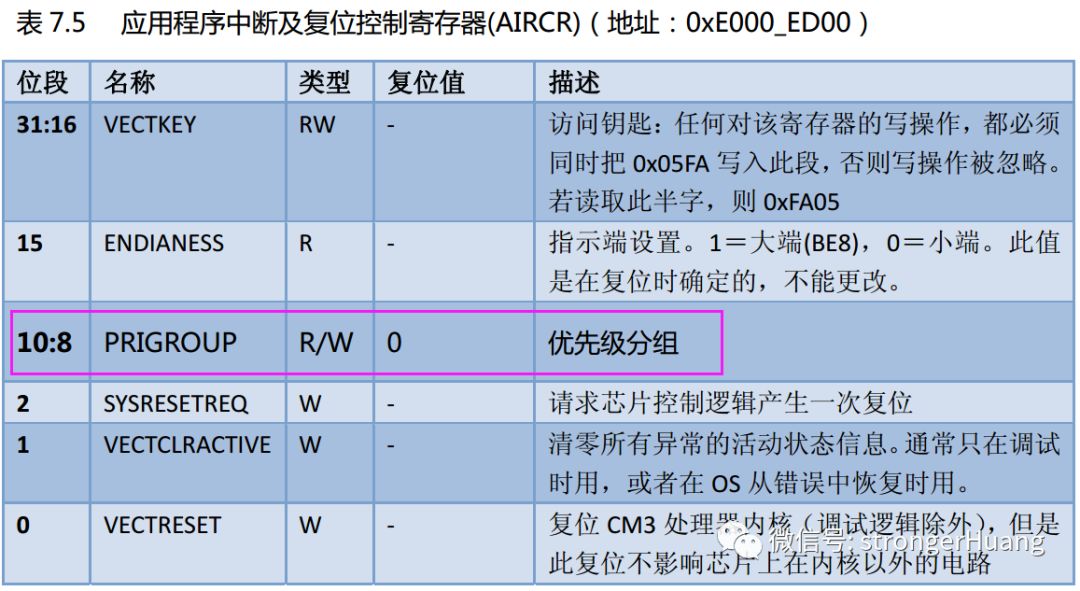

拿M3來說,優先級分組的配置,位于NVIC的AIRCR應用程序中斷及復位控制寄存器中: ?

?

中斷入口

額外提下一個小伙伴問的問題:為什么外部中斷8和9都使用同一個中斷?

void EXTI9_5_IRQHandler(void) { if(EXTI_GetITStatus(EXTI_Line8) != RESET) { /* 代碼 */ EXTI_ClearITPendingBit(EXTI_Line8); } if(EXTI_GetITStatus(EXTI_Line9) != RESET) { /* 代碼 */ EXTI_ClearITPendingBit(EXTI_Line9); } }我想,這個問題應該不難。好比一個main程序入口,進入之后需要處理很多事情,只是在里面需要區分事件。

很多外設中斷,都會使用同一個中斷入口,有一個原因:節約中斷入口資源分配。

像USART發送和接收中斷,TIM不同通道捕獲中斷等。

審核編輯:劉清

-

STM32

+關注

關注

2272文章

10923瀏覽量

357541 -

Cortex-M

+關注

關注

2文章

229瀏覽量

29841 -

ARM單片機

+關注

關注

0文章

45瀏覽量

9914 -

中斷優先級

+關注

關注

0文章

22瀏覽量

9406 -

stm32cubemx

+關注

關注

5文章

284瀏覽量

15000

原文標題:STM32中斷沒有子優先級?

文章出處:【微信號:strongerHuang,微信公眾號:strongerHuang】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

STM32 MCU通過STM32CubeMx配置NVIC怎么沒有中斷子優先級選項

Stm32中斷優先級概念及使用

STM32中斷優先級的分配以及中斷原則

stm32中斷優先級分組

為什么有些STM32中斷沒有子優先級?

為什么有些STM32中斷沒有子優先級?

評論