今天看皮皮蝦的時候看見一個視頻真的不是滋味,一位攝影家給一位農民一張照片。

他拿著照片陷入沉思,是迷茫,是震驚,是苦澀。仔仔細細看著照片中的人,很陌生又很熟悉:難道我已經這么老了嗎?

中國確實是這樣,有說不清的人就像被拋棄,一邊是快速發展的光鮮亮麗,一邊是這樣的不知道怎么辦的人,守著父輩的東西一直下去。

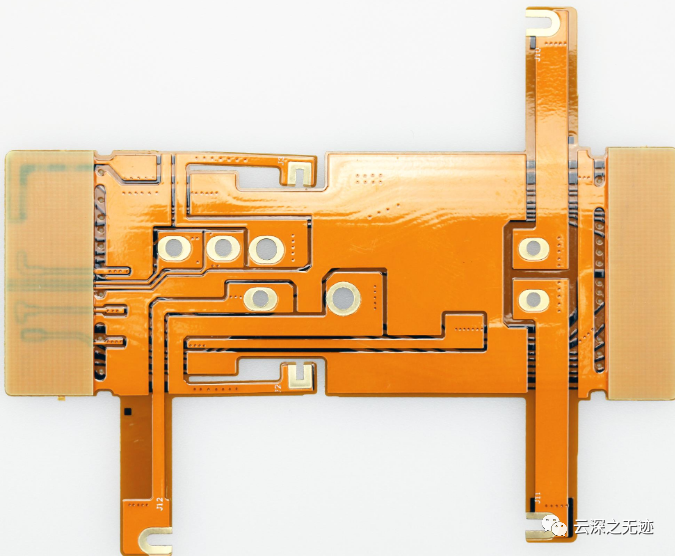

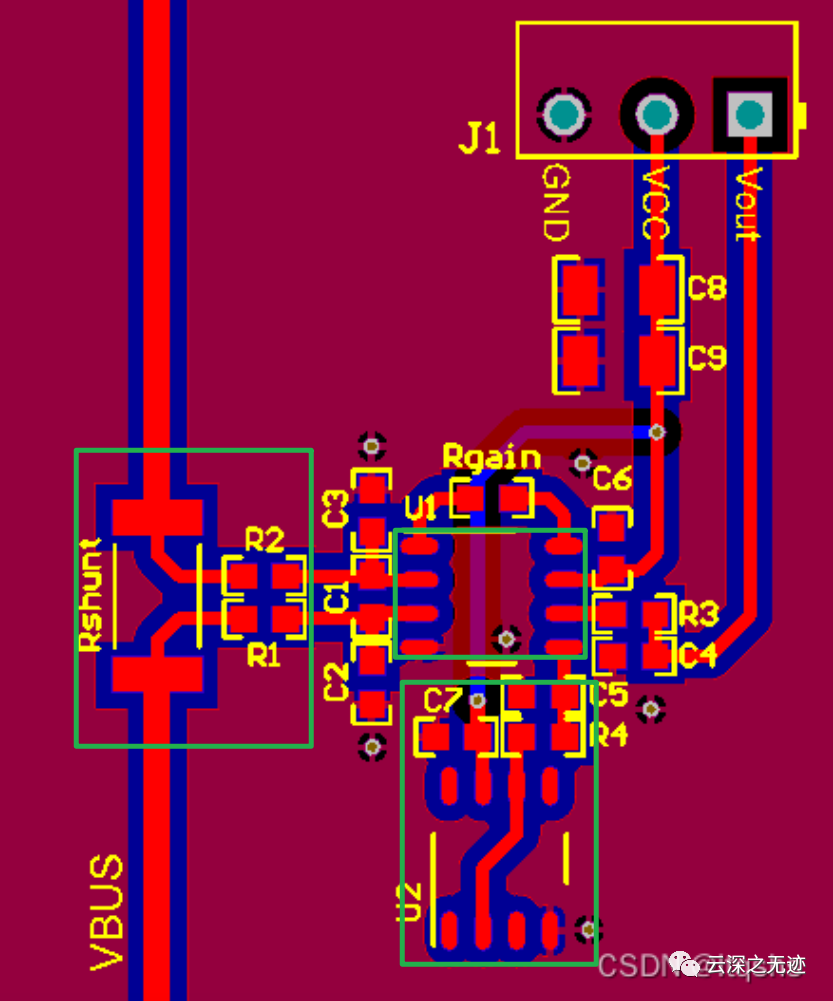

很離譜,看了這么多的文章視頻,都是搬運,不像我,我還至少寫倆個字。反正看了這么多文章來講,對布線這個事情,應該是器件的擺放最重要。因為原理圖設計的時候應該都是一個主要的芯片加一些外圍的電路,然后就是留下來了輸入和輸出的接口。按照擺放以外,還需要注意的事情就是布局的時候按照的是信號的流向,就是最好信號的傳輸距離越短越好,不過在低速里面無所謂了。

現在用嘉立創先繪制幾個板子,之后轉別的,因為功能還是有點羸弱的。比如就沒有原理圖和PCB同框,只有下面這兩個功能,不過倒是也夠用了,我指的是你有兩個屏幕,交叉的對照。

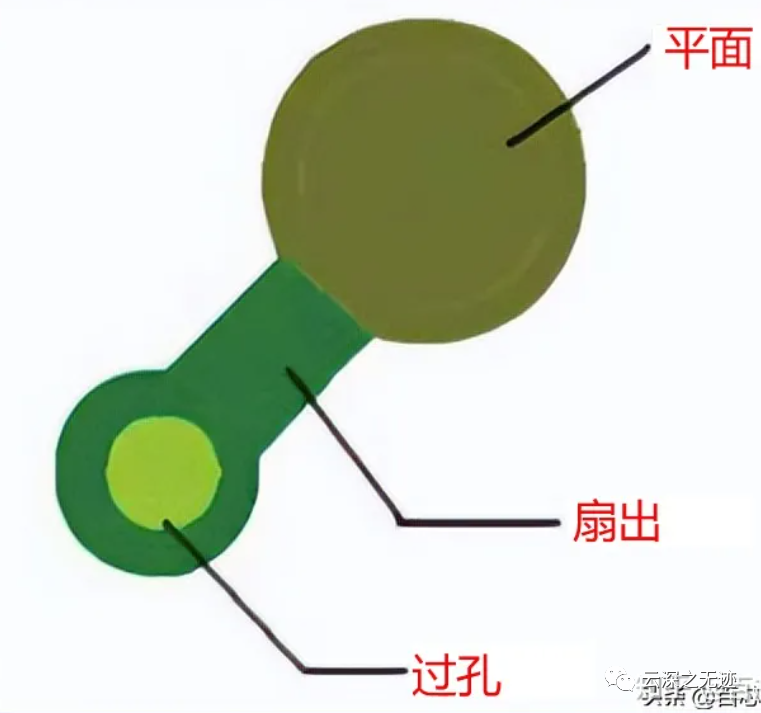

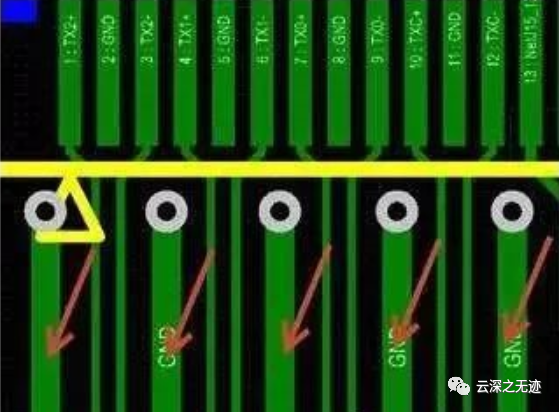

不過在B戰看到一個教程覺得不錯,在完成上面的布局以后就是要進行一個工作叫扇出?找了一下這個其實是服務于BGA封裝的,就是下面實在是不好走線,就提前把上面的焊盤都引出來。

扇孔的目的有兩個,打孔占位,減少回流路徑!

比如GND孔,就近扇孔可以做到縮短路徑的目的!預先打孔是為了防止不打孔后面走線的時候很密集的時候無法打孔下去,繞很遠鏈一根GND線,這種就很長的回流路徑了。

這種做高速PCB設計及多層PCB設計的時候經常遇到。預先打孔后面可以刪除很方便,反之等你走線完了再想去加一個過孔,很難,這時候你通常的想法就是隨便找根線連上便是,不能考慮到信號的SI,不太符合規范做法

就是這樣的感覺

說簡單點就是給所有的過孔上面引出東西,因為線走的密集了以后就不知道哪里會被干擾到。

還有就是多層板走線的時候,是看不見除了自己當前層之外的層里面的這個位置有沒有東西的,你打個孔就不一樣了。

還有就是多層板的理解也稍微的深刻了那么一點點、我以為的是底層和頂層就走所謂的信號線,第二層是地,第三層是Poewr。

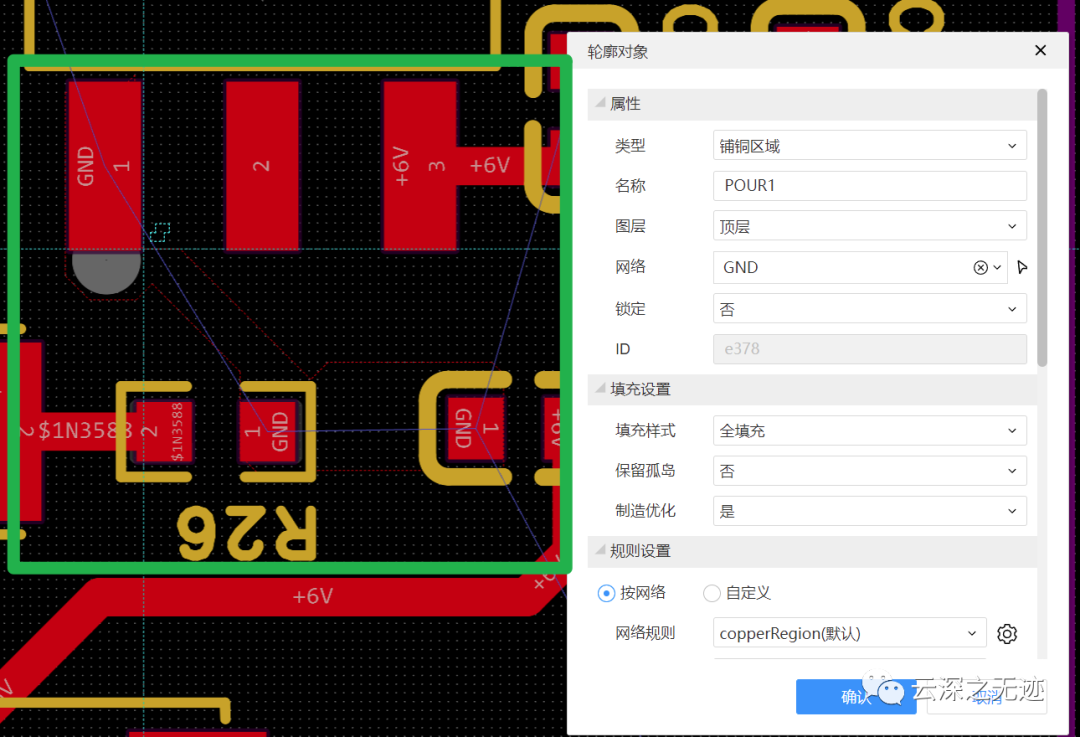

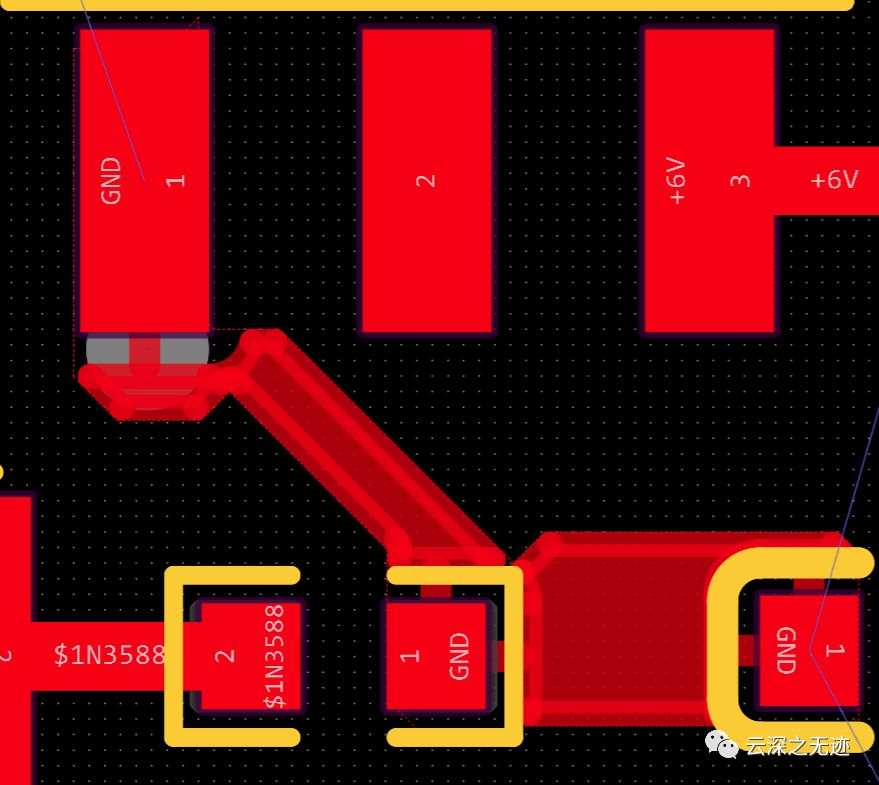

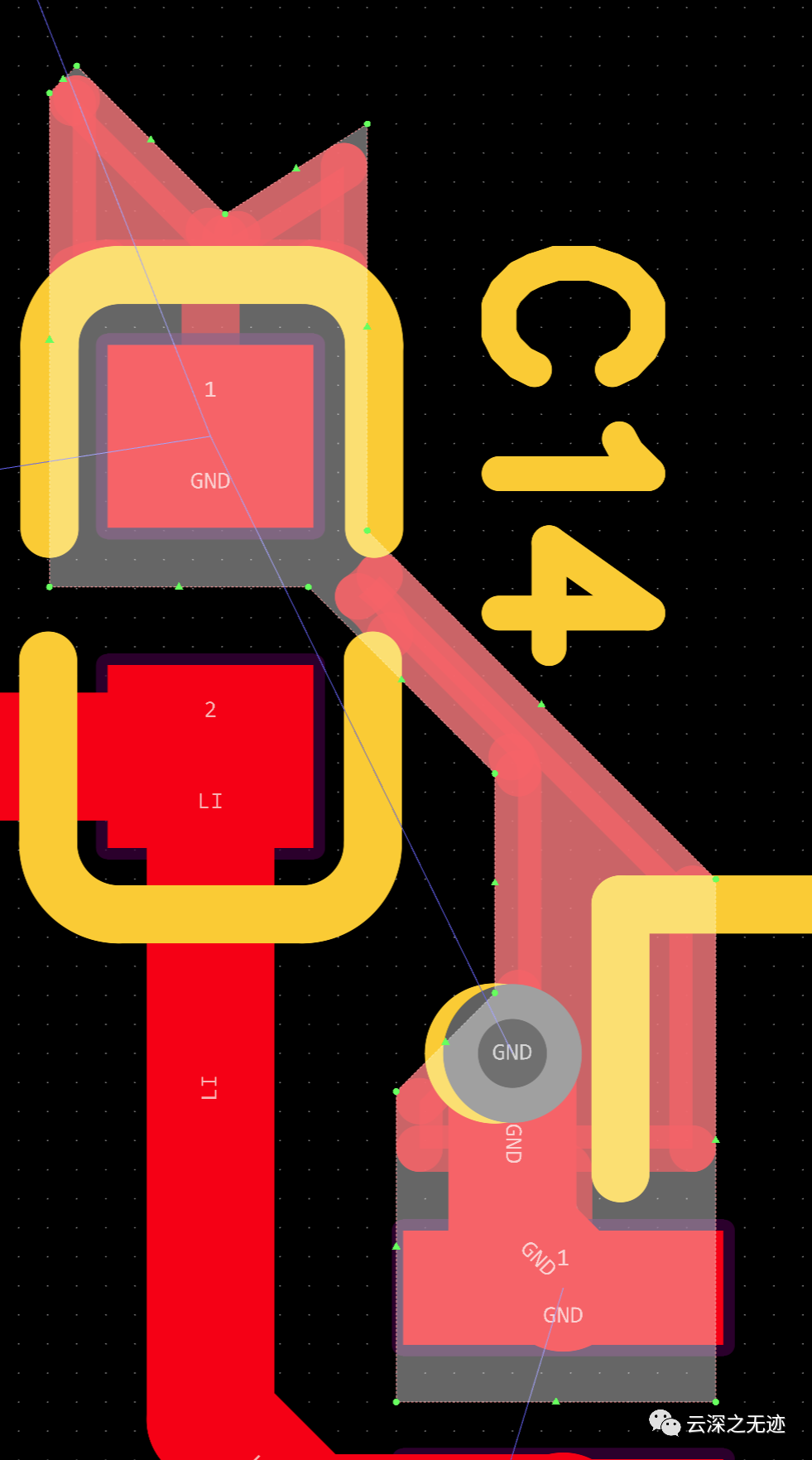

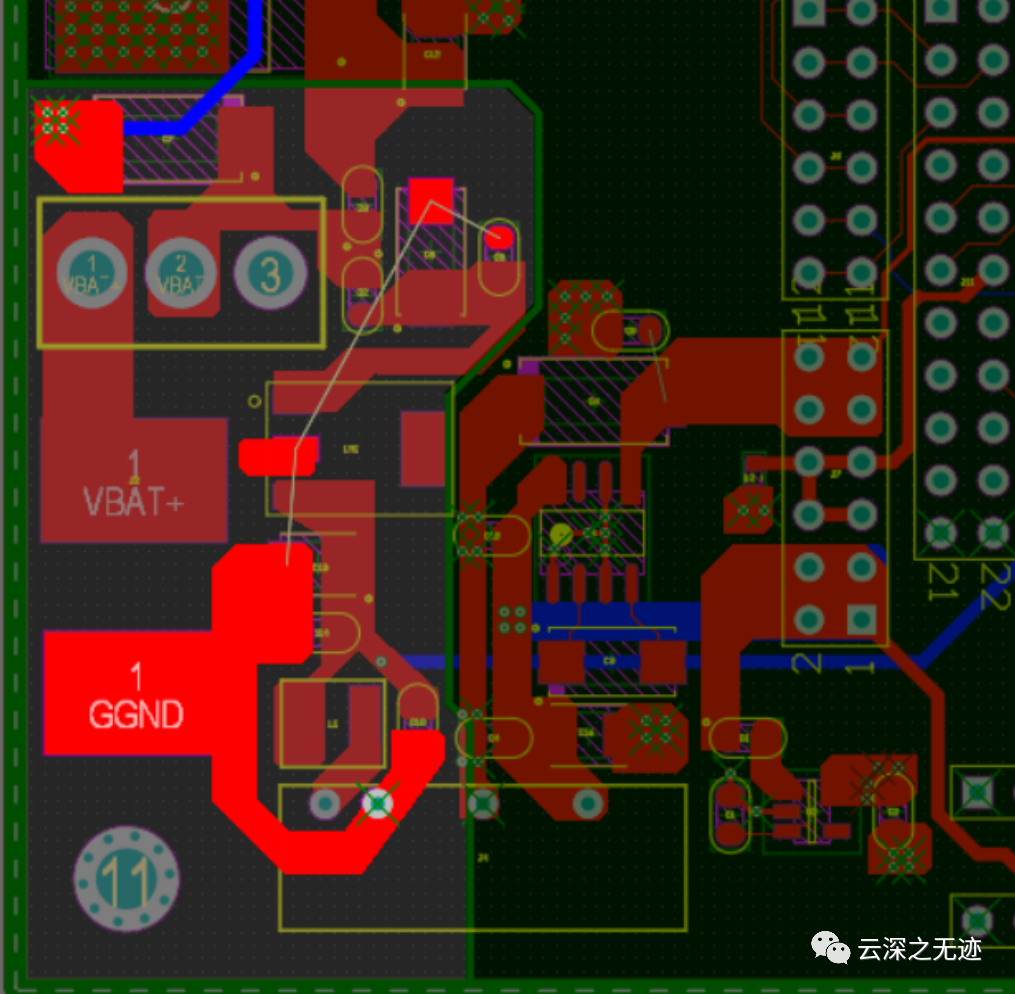

但是我看教程里面是這樣做的,在扇出的階段就把一些離的很近的GND,注意!就是GND,給鋪銅了(覆銅,灌銅都可以)。我一直以為鋪銅就是一個最后的工序而已,但是我覺得在前面完成這個過程好像挺合理的。

就是我現在這樣

可能灌的不好,但就是這樣這樣的意思

有點難看,反正也就是這樣就灌完了

所謂覆銅,就是將電路板上閑置的空間作為基準面,然后用固體銅填充,這些銅區又稱為灌銅。

覆銅的意義在于,減小地線阻抗,提高抗干擾能力;降低壓降,提高電源效率;與地線相連,還可以減小環路面積。

也出于讓PCB焊接時盡可能不變形的目的,大部分PCB 生產廠家也會要求PCB 設計者在PCB 的空曠區域填充銅皮或者網格狀的地線,

注意這個地方說的是!!!在空閑的位置,就是正好幾個元件的GND在一塊,其實在布局的時候也要有意識的去擺放。這個時候就鋪一下。然后鋪的時候或者是看見GND就趕緊打個孔下去,你放心,你還看我的文章,證明你還沒有到玩高速的段位,無所吊謂的,打孔就對了。

印刷電路板上的布線的分布電容會起作用,當長度大于噪聲頻率相應波長的1/20 時,就會產生天線效應,噪聲就會通過布線向外發射,如果在PCB中存在不良接地的覆銅話,覆銅就成了傳播噪音的工具,因此,在高頻電路中,千萬不要認為,把地線的某個地方接了地,這就是“地線”,一定要以小于λ/20 的間距,在布線上打過孔,與多層板的地平面“良好接地”。

這個孔的電容其實有個公式來著。不記得了。

還有就是我以為4層板的電源是一定要走到稍微的電源層的,其實不是,實現PCB走線的第一個點就是將對應的地方聯通就行!!!這個教程里面我如果沒有看錯,電源就沒有走電源層,就是上下倆層來回走。但是有的也說電源優先走電源層,但是一些小電流電源可能會走到信號層。

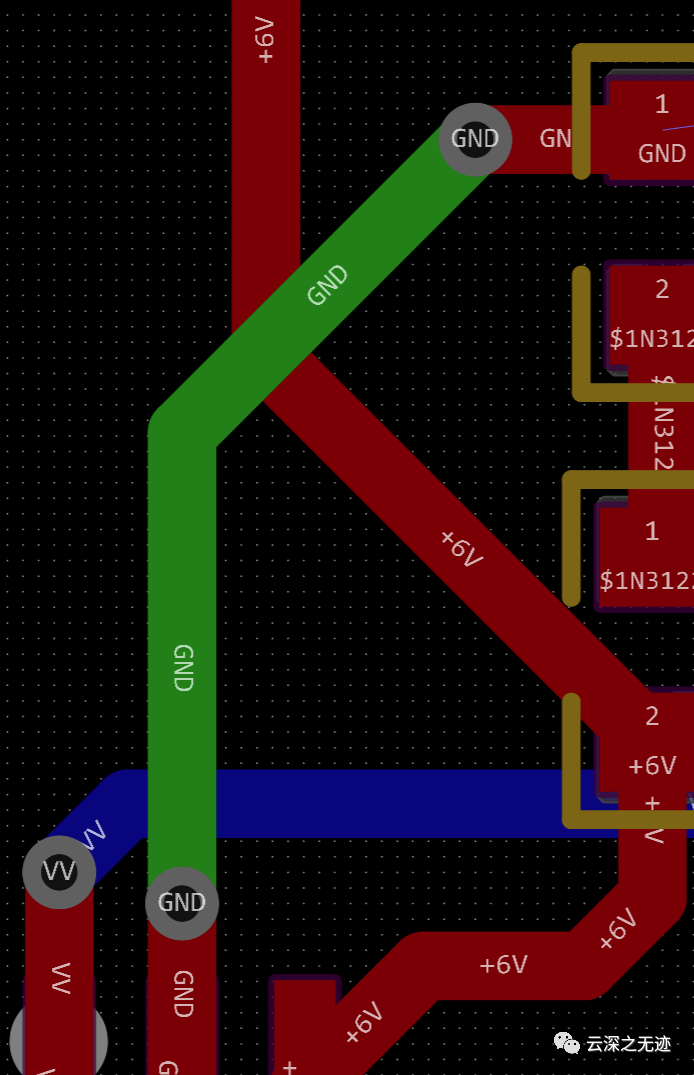

這個綠色的就是電源層,完全是可以可以走的

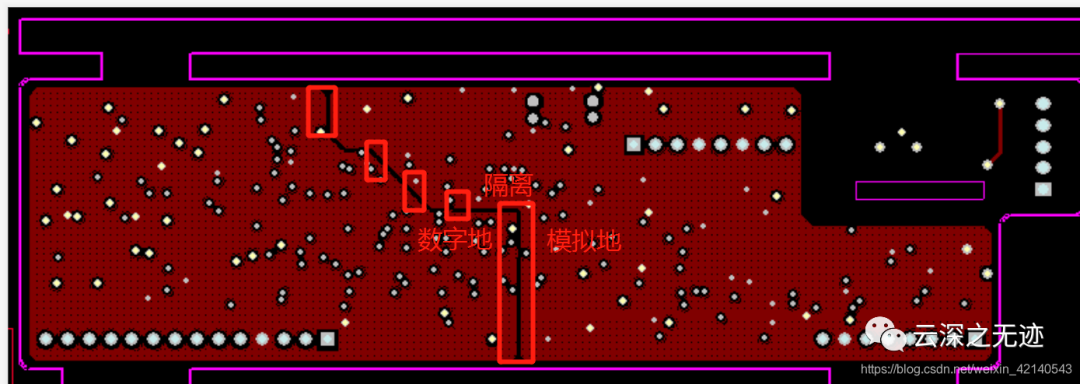

就是在走完GND,和信號線的時候再走電源線,但是要注電源平面分割的事情,就是GND也有很多。這里就簡單的說是模擬和數字地。

這個圖是我找到的一個比較好的圖

現在許多PCB不再是單一的數字或模擬電路,而是由數字電路和模擬電路混合構成的。因此布線的時候需要考慮它們之間的相互干擾問題,特別是地線上的噪聲干擾。

數字地、模擬地和保護地要分開,并且保持2.5mm間距;數字地、模擬地保持1mm的間距。

這里沒有截圖

這就是割開了

這個圖也好,就是說包地處理:鄰近GND層走線,空間足夠的情況下進行包地處理。

對了說下信號線:能不打孔則不打孔,減少走線長度。

孔的作用:一個面無法走的線,可以通過打孔,在另一個面進行走線。

PCB四層板布線,是電路板設計中十分重要的一環。其中,電源層的設計和走線,更是需要仔細考慮和處理的部分。本文將詳細介紹PCB四層板布線中,電源層的合理利用技巧和注意事項。

PCB四層板中的電源層是可以進行走線的。但是,在進行走線時需要注意以下幾點:

1.電源層的走線需要合理規劃,避免與其他信號層的走線產生干擾。

2.電源層的走線應盡量避免放置過多的孔洞。孔洞會導致電源層的連續性變差,從而影響整個電路板的性能。因此,我們應該盡量減少電源層上的孔洞數量,并合理安排孔洞的位置。

3.在走線過程中,要注意電源線的寬度和走線的路徑。電源線的寬度要根據電流大小來決定,一般情況下,電源線的寬度要比信號線寬。走線的路徑應盡量短且直接,減少線路阻抗和功耗的損失。

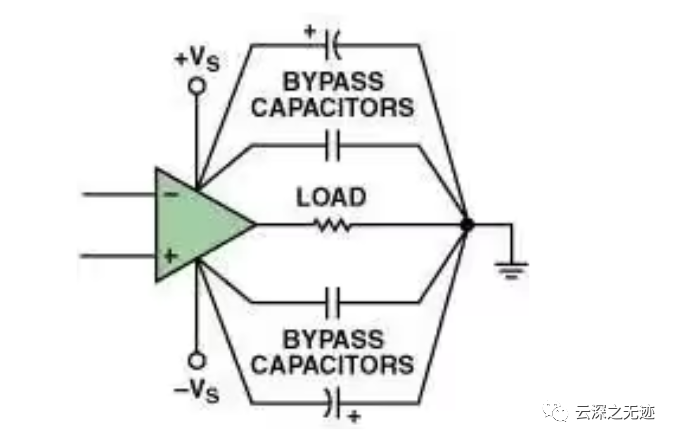

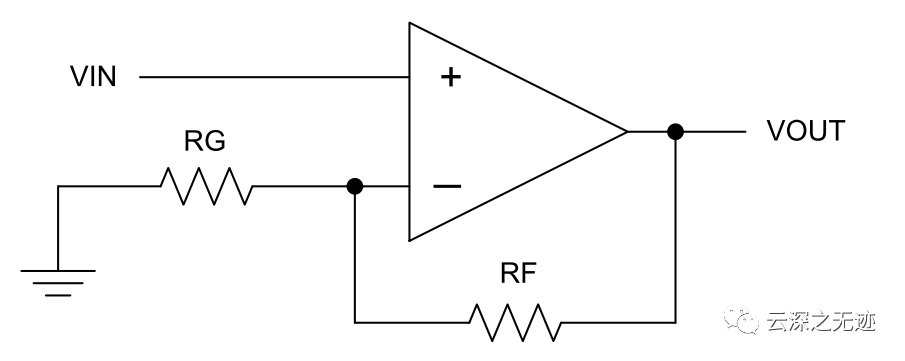

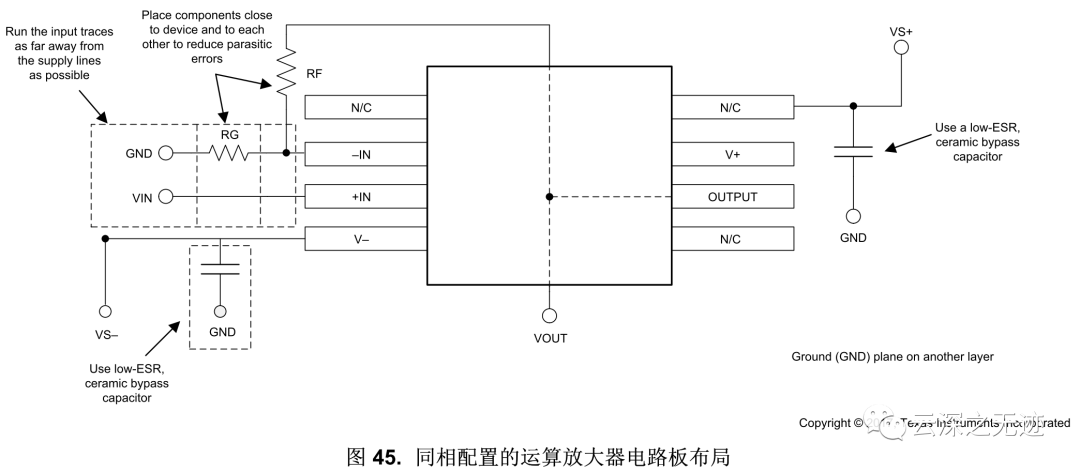

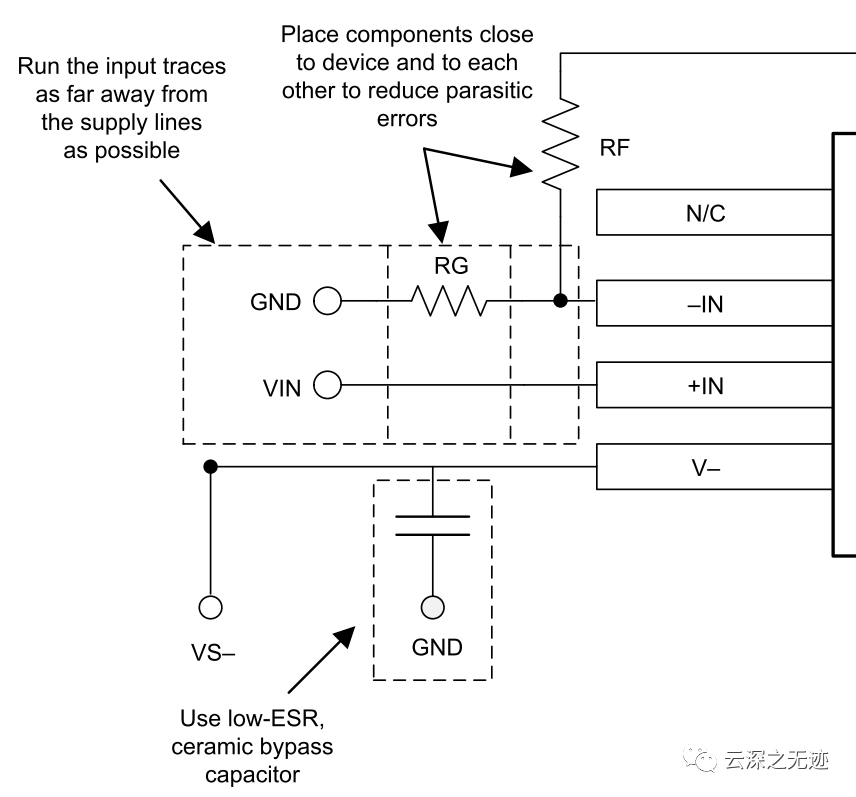

直接從運算放大器的電源引腳入手;具有最小電容值和最小物理尺寸的電容器應當與運算放大器置于PCB的同一面——而且盡可能靠近放大器。

電容器的接地端應該用最短的引腳或印制線直接連至接地平面。上述的接地連接應該盡可能靠近放大器的負載端以便減小電源端和接地端之間的干擾。

去耦電容應該盡量靠近芯片的電源引腳。如果使用了多個去耦電容器,應該將較小的去耦電容(旁路電容)放在離電源引腳最近的位置,將較大的去耦電容(庫電容)放在遠離電源引腳的位置。

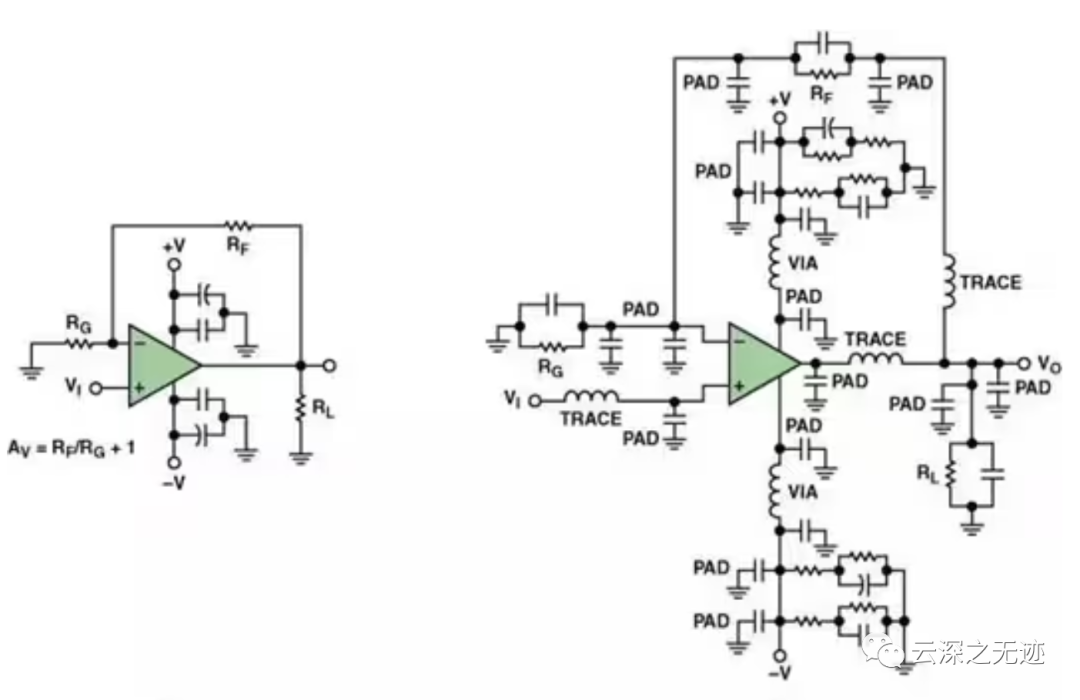

這個圖是考慮寄生效應的

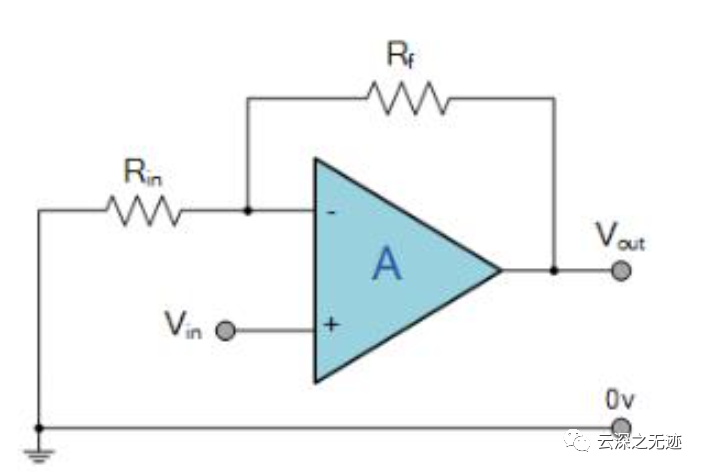

寄生效應就是那些溜進你的PCB并在電路中大施破壞、頭痛令人、原因不明的小故障(按照字面意思)。它們就是滲入高速電路中隱藏的寄生電容和寄生電感。其中包括由封裝引腳和印制線過長形成的寄生電感;焊盤到地、焊盤到電源平面和焊盤到印制線之間形成的寄生電容;通孔之間的相互影響,以及許多其它可能的寄生效應。圖3(a)示出了一個典型的同相運算放大器原理圖。但是,如果考慮寄生效應的話,同樣的電路可能會變成圖3(b)那樣。

不要將過孔(Via)置于去耦電容和電源引腳之間。

過孔本身擁有一些寄生參數,會影響去耦電容的濾波效果。

對于雙電源供電模式,在V+和V-之間接一個濾波電容,可以減少電路中的偶數次高次諧波。

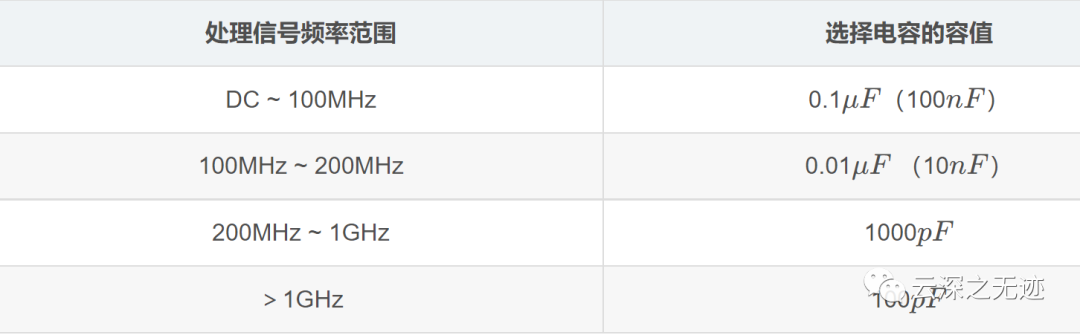

電容器的電容值應該根據處理信號的頻率按以下的標準確定(下列值是根據經驗得出的)。

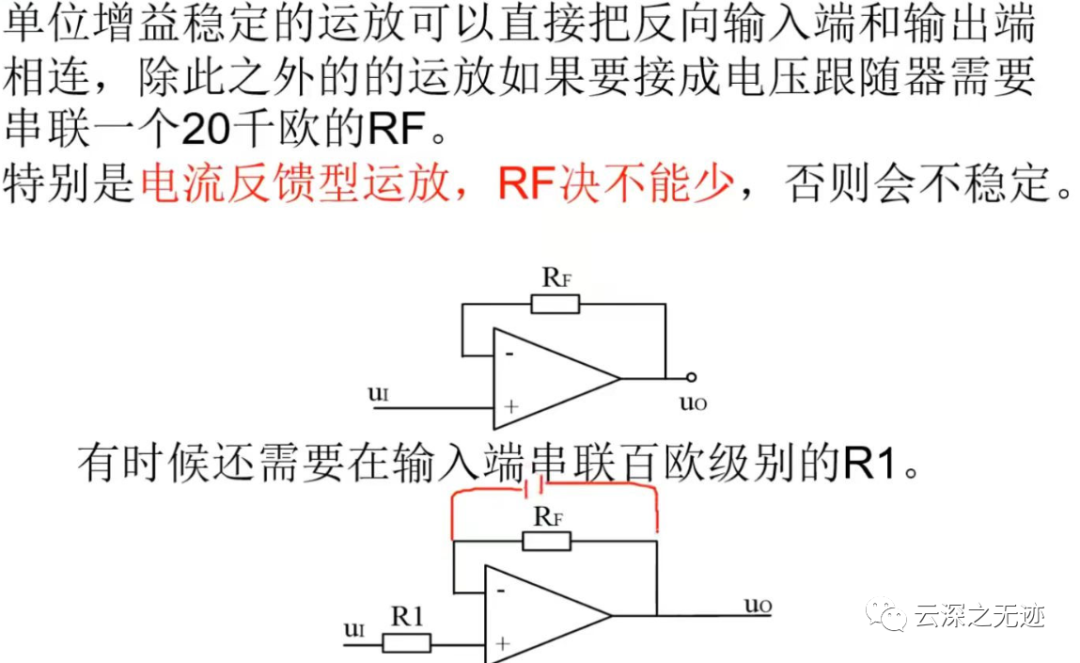

1.應該盡可能縮短反相輸入端引腳與其他器件的連接距離。(在運放中通常在反相輸入端輸入信號,這里應該是防止長導線的寄生參數對輸入信號的影響)

2.應盡可能拓寬走線寬度。

3.禁止直角走線或銳角走線。

4.應該灌流至少一個堅實的接地層。

5.不要為了方便用絲印來標識器件而舍棄良好的布局。

在畫PCB時,放大器的輸入輸出信號腳以及反饋電阻的下面不要在走其他線,這樣可以減小不同線之間的寄生電容的相互影響讓放大器更穩定。

5、表面貼裝器件的高頻新能比較好同時又體積小。

6、電路板布線時走線盡可能的短同時還要注意的他的長與寬讓寄生效應最小化。

7、對于電源線的處理電源線寄生特性最壞的直流電阻與自感所以我們在布電源線的時候盡可能的加寬些。

8、對于放大器輸入輸出連接線上面的電流非常小所以這樣他們是很容易受影響的寄生性效應對他們危害很大。

9、對于超過1CM的信號路徑最好是用受控阻抗和兩端終接(匹配電阻)的傳輸線。

10、放大器驅動阻容性負載為了解決穩定性的問題一種常用的技術是引入一個電阻ROUT 同時最好靠近運放 這樣利用串聯輸出電阻實現對容性負載的隔離。

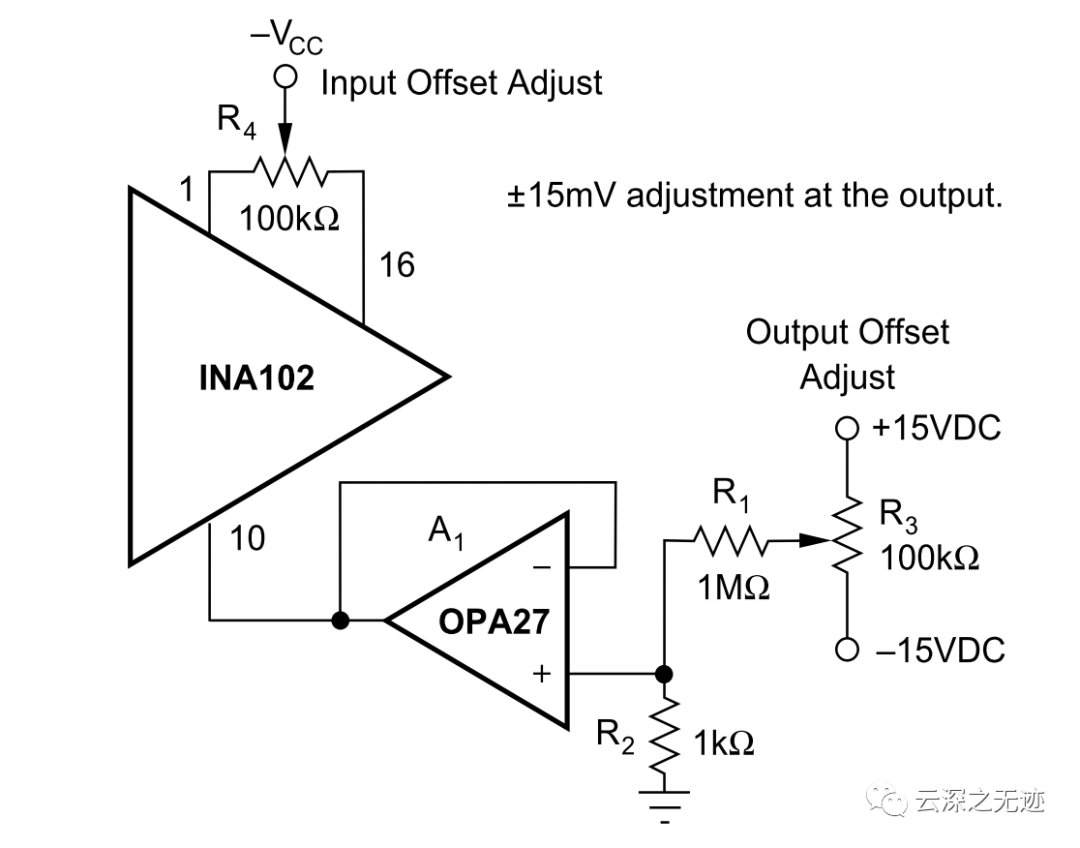

參考引腳緩沖電路定位在遠離參考引腳的地方,這增加了連接到參考引腳的電阻,并為噪聲和其他信號耦合到跟蹤打開了可能性。

參考引腳上的附加電阻將降低大多數INAs提供的高共模抑制比(CMRR)。因此,將參考引腳緩沖電路盡可能靠近INA的參考引腳。

因為REF端并不需要大的輸入電流,也不需要阻抗匹配,所以直接接參考電壓就可以的。

1.對于電路中可能會出現大的開關電流的元件要盡量遠離儀表放大器。

2.儀表放大器接地要放在遠端,而把大電流的元件或頻繁開關的元件放在接地的近端。

3.儀表放大器接地時加入耦合電容。

審核編輯:湯梓紅

-

原理圖

+關注

關注

1300文章

6358瀏覽量

235165 -

pcb

+關注

關注

4326文章

23160瀏覽量

399946 -

PCB設計

+關注

關注

394文章

4698瀏覽量

86341 -

布線

+關注

關注

9文章

777瀏覽量

84428

原文標題:媽的!關于PCB布線這個事!

文章出處:【微信號:TT1827652464,微信公眾號:云深之無跡】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB布線設計教程

PCB布線設計教程

評論