芯粒(chiplet)市場是整個芯粒領域最值得關注的話題之一。毫無疑問,技術問題會及時得到解決,例如芯粒裸片到裸片接口、創(chuàng)建良好的芯粒庫格式,或是改善已知良好裸片的測試。但芯粒商業(yè)模式將何去何從,依然迷霧重重。

理想的模式是:準備好一個 Intel CPU 芯粒、一個 NVIDIA GPU 芯粒、一個高通調制解調器芯粒和一個 AMD/Xilinx FPGA 芯粒,然后將它們置于同一個系統(tǒng)級封裝中即可。

但我們目前所處的階段離這個目標還很遙遠。

在今年美國硅谷舉辦的芯粒峰會(Chiplet Summit)上進行了一場題為“如何打通芯粒市場”的小組討論會。該會議由 Meta 公司的 Ravi Agarwal 主持,與會者(下圖中從左到右)依次為:

Ventana Micro Systems 公司的 Charles 先生

Alphawave Semi 公司(即 Alphawave IP 公司)的 Clint Walker

Marvell 公司的 Mark Kuemerle

NVIDIA 公司的 Durgesh Srivastava

Samsung Foundry 公司的 Kevin Yee

這場小組討論會精彩紛呈,不僅座無虛席,甚至還有很多站著的聽眾。因此,本文總結了此次討論會的精華內容,以與現(xiàn)場一致的問答形式與大家分享。

Q1.多家公司的芯粒能否組合起來協(xié)調運行?

Ventana

大家對芯粒都很感興趣,但當下只有自研芯粒的大公司才能生產出來。我們面臨的挑戰(zhàn)是,多家公司的芯粒能否組合一起協(xié)調運行?我們的生態(tài)系統(tǒng)中有很多不同的公司,今天就讓我們討論一下這個目標能否實現(xiàn)。

Alphawave 公司:我們今天的討論十分火熱,按某種規(guī)律來說,如果一次會議有很多人出席,那么五年之內就會形成一個市場。

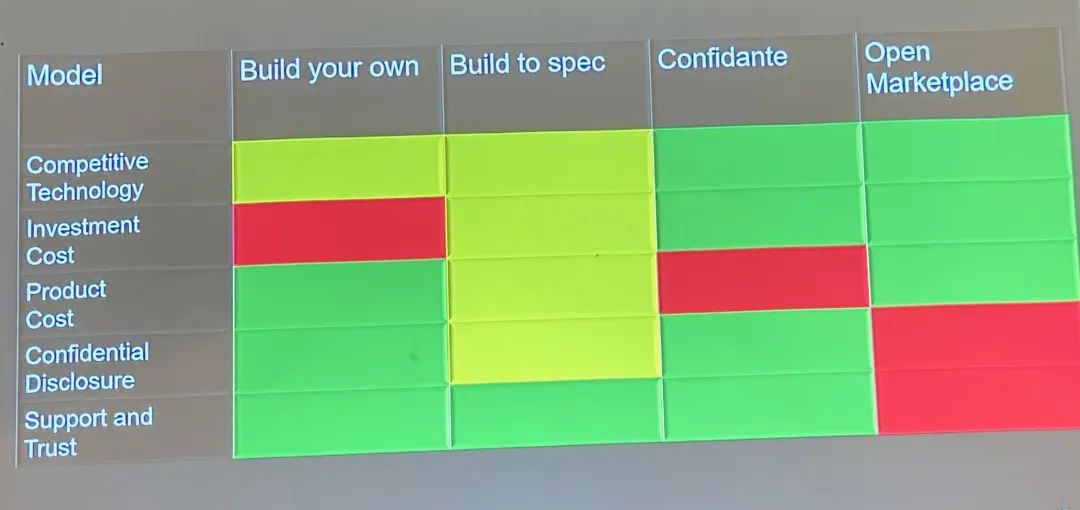

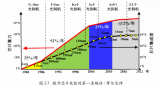

Marvell 公司:打造開放的芯粒市場,這個設想很美好,但需要克服很多障礙。理想化的情況是可以像逛商場一樣隨意挑選產品。目前,只有垂直整合公司或者供應商可以按照規(guī)范打造產品,只限于數(shù)量有限的芯粒和值得信賴的合作伙伴。這與“開放式芯粒市場”的構想相去甚遠。那該如何循序漸進地實現(xiàn)這一點?下圖展示了各種基于芯粒的設計實現(xiàn)方法的優(yōu)點(綠色)和缺點(紅色)。

NVIDIA 公司:業(yè)內認為,摩爾定律在推出 51 年后已經失效,就目前而言,超越摩爾定律成為了新常態(tài)。我們需要一種適合小型供應商的解決方案。

Samsung 公司:芯粒早已成為一種解決方案,但如何才能將其業(yè)務化或市場化?互操作性可能意味著要開發(fā)很多專有技術,對于市場來說,必須要有一個開放的標準。PCIe 之類的接口有“plugfest”事件來確保互操作性,那么裸片到裸片設計也需要類似的標準,但我們對此毫無頭緒。封裝是最棘手的問題之一。

Q2.芯粒的未來市場需求

1.未來 5-10 年芯粒的市場需求如何?

Marvell 公司:大家時刻都在尋找一種方式來使用多芯片系統(tǒng),以優(yōu)化開支結構。多芯片系統(tǒng)屬于高端基礎架構。我們偶爾會開發(fā)單芯片,不過現(xiàn)在的需求寥寥無幾。

Ventana 公司:汽車 ADAS 解決方案非常龐大,無論怎樣,裸片終究需要分割開,所以不妨就此開始解決。我們需要有機基板,它不局限于超大型、造價超高的芯片。

兩年內,AI 數(shù)據(jù)中心的市場規(guī)模將達到 5000 億美元,需求很旺盛。對此,芯粒是唯一的選擇。

NVDIA

Samsung 公司:我們和許多客戶溝通過,其中一些垂直整合商表示,他們如今有 50% 的設計是基于芯粒的。在 5-10 年內,需求將非常高,但對其他廠商來說,我們需要構建一個生態(tài)系統(tǒng)。OSAT 需要準備就緒,接口互操作性也是必需的(UCIe 已經發(fā)布但尚不成熟)。Open HBI 好像消失了。

2.芯粒可以采取哪種商業(yè)模式,在 KGD(Known-good-die,已知良好裸片) 方面有什么經驗可供分享?

Ventana 公司:一些廠商擁有最終設計,如果出現(xiàn)問題,可以聯(lián)系自己的供應商,這與 IP 沒有太大區(qū)別。芯粒有所不同,不過也有一些現(xiàn)行的模式。

AlpahWave

起初我們需要 ASIC 模式,現(xiàn)在正在努力提供更多標準選項,目標是在5-10 年后可以像逛商場一樣挑選芯粒。

Marvell 公司:我們采用過“選擇一個值得信賴的合作伙伴”模式。如果要從多個來源集成,如何啟用多個芯粒就成為一項挑戰(zhàn),因為每個芯粒都有自己的測試功能和 KGD。我們需要找到相應的方法,讓不同的公司可以分享更多信息,同時不必擔心知識產權受損。

Samsung 公司:這將是一次革新,只是現(xiàn)在仍停留在商業(yè)談判階段,每個公司手握整個設計,但是還沒有標準模式。

Q3.芯粒未來發(fā)展需要考慮的問題

1. 如何確保芯粒的安全性?

Marvell 公司:安全的現(xiàn)行定義是一切都包含在一個 SoC 中。但問題是:只在一個芯粒中能否實現(xiàn)安全性?是不是每個公司都有各自的安全標準?重點是要讓多個芯片以安全的方式統(tǒng)一運行。目前并不存在這種技術。

NVIDIA 公司:數(shù)據(jù)中心有很多安全要求,我們要確保傳輸、存儲和計算過程中的安全性。

Alphawave 公司:安全啟動也是一個問題。要把它置于哪個芯粒上?具體的位置是哪里?是否需要設計一個專用的安全芯粒?

2. 如果一個產品包含多個芯粒,最終客戶會感知到利潤的層層疊加嗎?

我們認為答案是肯定的。在之前展示的虛構系統(tǒng)中,我希望每個芯粒都做到最好。在這種環(huán)境下,利潤必定層層疊加。芯粒就像是一個包裝好的產品,而我們秘制調料剛剛好。IP 模式已經是慣例,如果芯粒朝著IP的方向走,將會有新的變化。

Marvell

Ventana 公司:芯粒可以讓人們買到想買的東西。如果開發(fā)的解決方案針對自己的需求,并且買到的東西也是恰好需要的,那么性價比就會很高。這將在一定程度上抵消利潤層層疊加的問題。

Alphawave 公司:與我們如今面對的關于代工廠、IP 等方面的問題差不多。如果能買到支持 60 種不同產品的 I/O 芯粒,那么成本將會更低。UCIe 就像 PCIe,只需要“連上插頭”就可以了。

3.軟件支持的問題又將如何?在芯粒中,使用微處理器來實現(xiàn)系統(tǒng)啟動或初始化,那么對于每個子系統(tǒng)附帶的軟件,我們要為最終客戶提供哪些支持?

Marvell 公司:這是當下芯粒面臨的問題。垂直整合公司可以投入人力物力開發(fā)通用 API,也可以支持基于芯粒的系統(tǒng)。但這僅限于垂直整合公司或按規(guī)格加工的模式。相比之下,裸片到裸片的通信顯得很簡單。

Ventana 公司:這也是我們致力于解決的方向,必須搞清楚如何分區(qū),就像是拼接一個 SoC ,然后提供一個完整的解決方案。

NVDIA

要構建芯粒生態(tài)系統(tǒng),軟件支持不可或缺。比如說如果四五家公司一起合作,那么肯定需要目前所缺乏的、通用的 API 框架。

Alphawever公司:沒人能為我們買到所有的 IP,而現(xiàn)在我們必須提供五家不同供應商的 API,還要知道如何讓客戶無縫使用,挑戰(zhàn)性很大。

Samsung 公司:在將基于芯粒的設計交付最終客戶時,設計結果應該和 SoC 一樣,像是 “一塊大型芯片”,我們開發(fā)軟件的方式也與開發(fā) SoC 的方式相同。

4.把 Compute Express Link (CXL) 和芯粒放在一起對比是個好主意。對于 CXL,我們有“結構管理器”,而這個術語沒有明確的定義。在異構設計中,這種模式無法發(fā)揮作用。定義結構管理器會成為多芯粒設計的一部分嗎?

NVIDIA 公司:結構非常重要。當前的 CXL 結構只能解決存儲器一個方面的問題。它不是面向點對點的。CXL 還在縱向擴展,位于機架內。但我們也要考慮橫向擴展機架到機架。

Marvell 公司:并非所有的芯粒系統(tǒng)都將基于 PCIe 或 CXL。如果結構管理器以不同的方式通信,能否依賴一個定義好的結構管理器標準,這需要打上一個問號。

Q4. 現(xiàn)場觀眾提問

1. 大家都對芯粒都充滿期待,我也是芯粒的忠實擁護者。芯粒的物理外形尺寸與 IP 區(qū)別很大。我們要如何解決這一點?在解決這個問題之前,很難打造一個統(tǒng)一市場。

Alphawave 公司:bump 間距不一樣,通道數(shù)量之類也不一樣。一切都是不同的,應該根據(jù)需求確定優(yōu)先級。

Marvell 公司:沒有哪種合理的方法可以讓外形尺寸標準化,以便將芯粒整齊排列在一起。我們還需要開發(fā)出多個裸片到裸片接口解決方案。這種“俄羅斯方塊”一樣的排列問題很難解決。

2. 外形尺寸方面如何?

Alpahwave 公司:這需要根據(jù)上市時間進行權衡。比如說本來預計有兩個通道,但最終出現(xiàn)了 16 個。要么只能采用這 16 個通道,要么就再等一年,才能實現(xiàn)兩個通道的設計。

這和 FPGA 類似,它們的尺寸永遠都不能做到完美匹配。

Samsung

Marvell 公司:什么時候才是創(chuàng)建芯粒的合適時機?把各種功能都打包在一個芯粒中,現(xiàn)在這種想法也許不切實際。

Alphawave 公司:如果競爭對手在單芯片市場一路領先,那就意味著錯失良機。芯粒可能不是唯一的答案。

3.我們經常會討論大型裸片的解體。那對于小型裸片呢,比如智能手表里的裸片?它們具有同樣的應用價值嗎?

Marvell 公司:芯粒有很多應用領域。

NVDIA

我們看過 Apple Watch 的拆解過程,它的基板架構上有一塊主板,這已經算是芯粒。

Alphawave 公司:很多產品都在縮小外形尺寸。

Samsung 公司:隨著產品尺寸縮小,接口成本增加了。如果接口可用于多種應用,那么直接使用沒問題。但僅僅為了芯粒而做芯粒是沒有意義的。

Ventana 公司:如果是大型數(shù)據(jù)中心芯片,那就簡單多了。成本下限在不斷降低,但也不會一直降到 10 美元。

4.現(xiàn)在有形成某種格局嗎?有些想做芯粒的客戶聯(lián)系我們,但通常不太合適。有沒有學術研究表明技術節(jié)點是否成熟?行業(yè)格局目前又如何?這樣客戶就可以知道是否會盈利。

OCP 開放成本模型是目前最好的模型。它提供了 15 到 20 個變量,是很好的初步計算工具。

Meta

Alphawave 公司:我們用一張圖表來確定盈虧平衡點。

Samsung 公司:我們參與了那個開放成本模型的開發(fā),但它是高層次的工具,不會顯示詳細的成本。它基于電子試算表,用戶可以更改變量。

Meta公司:他們很快就會發(fā)布新版本的模型。

5. 剛才提到未來該采用哪種成本模型,也許 IP 模型也是一樣的,40 多年前花 10 或 20 美元就能買到標準元件,但 FPGA 市場每個要花 10 萬美元。ASIC 的 IP 模型不適用于 FPGA。現(xiàn)在,芯粒能像40 多年前一樣,花 10 或 20 美元買到元件,然后構建一個系統(tǒng)嗎?

Alphawave 公司:如果想自主構建芯粒,那么 IP 模式還是行得通的。但對于芯粒本身,則需要購買整個產品。

Marvell

我們夢寐以求的正是無需為先進的技術掩膜付費,也無需購買相關的掩膜。掩膜成本遠遠高于 IP 成本。

Ventana 公司:不需要花大筆的錢來獲得 IP 核心許可,可以直接購買芯粒。

Samsung 公司:有一天芯粒會成為一種商品,公司可以數(shù)百萬地制造,很多客戶想要購買里面的小元件。但這一天目前還沒有到來。

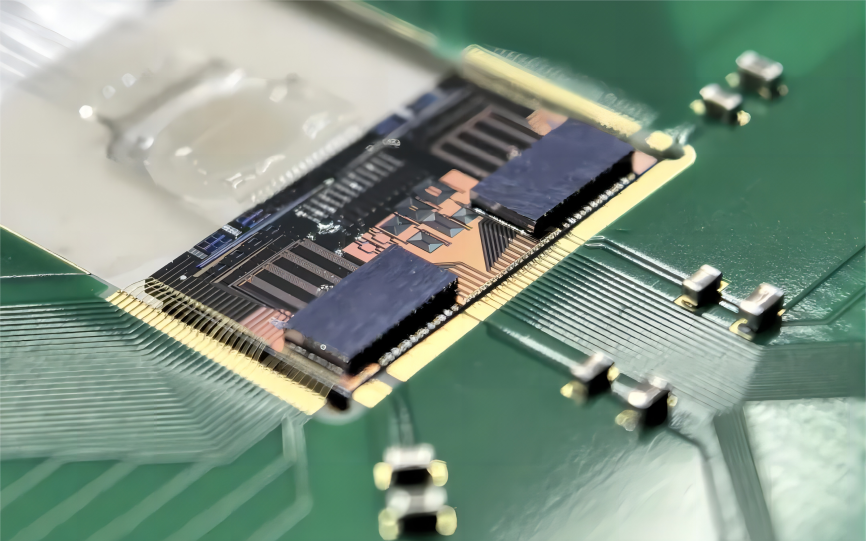

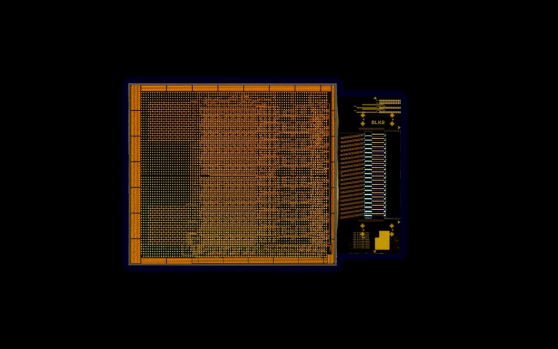

多芯粒架構為最新的設計節(jié)點提供了成本更低的選擇,同時仍然以物理芯粒的形式,提供基于 IP 的重用模型。如今,封裝設計已成為新一代電子產品的核心。

-

芯片

+關注

關注

456文章

51182瀏覽量

427273 -

測試

+關注

關注

8文章

5377瀏覽量

127063 -

cpu

+關注

關注

68文章

10904瀏覽量

213020 -

芯粒

+關注

關注

0文章

59瀏覽量

153

發(fā)布評論請先 登錄

相關推薦

國內首款2Tb/s 3D集成硅光芯粒成功出樣,華為、英偉達等巨頭爭相布局

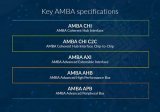

Arm宣布其芯粒系統(tǒng)架構正式推出首個公開規(guī)范

Arm發(fā)布芯粒系統(tǒng)架構首個公開規(guī)范

今日看點丨Arm 發(fā)布芯粒系統(tǒng)架構首個公開規(guī)范;納芯微推出車規(guī)級D類音頻功率放大器

集成芯片與芯粒技術詳解

Imec牽頭啟動汽車芯粒計劃

強勢入局芯粒技術鏈 東方晶源PanSys產品重磅發(fā)布

北極雄芯“啟明 935”系列芯粒成功交付流片

芯德科技揚州晶圓級芯粒先進封裝基地項目封頂

英特爾OCI芯粒在新興AI基礎設施中實現(xiàn)光學I/O(輸入/輸出)共封裝

英特爾突破技術壁壘,推出全新硅光集成OCI芯粒

英特爾實現(xiàn)光學IO芯粒的完全集成

國信光電子創(chuàng)新中心發(fā)布首款2Tb/s硅光互連芯粒

為什么選擇將AMBA CHI用于芯粒呢?

芯粒峰會:如何打通芯粒市場

芯粒峰會:如何打通芯粒市場

評論