大多數(shù)工程師對CPU和順序編程都十分熟悉,這是因?yàn)樽詮乃麄冮_始編寫CPU代碼以來,就與之密切接觸。然而,對于GPU的內(nèi)部工作原理及其獨(dú)特之處,他們的了解則相對較少。過去十年,由于GPU在深度學(xué)習(xí)中得到廣泛應(yīng)用而變得極為重要。因此,每位軟件工程師都有必要了解其基本工作原理。本文旨在為讀者提供這方面的背景知識(shí)。

本文作者為軟件工程師Abhinav Upadhyay,他在《大規(guī)模并行處理器編程》第四版(Hwu等)的基礎(chǔ)上編寫了本文大部分內(nèi)容,其中介紹了包括GPU體系結(jié)構(gòu)和執(zhí)行模型等內(nèi)容。當(dāng)然,文中GPU編程的基本概念和方法同樣適用于其他供應(yīng)商的產(chǎn)品。

01. 比較CPU與GPU

首先,我們會(huì)比較CPU和GPU,這能幫助我們更好地了解GPU的發(fā)展?fàn)顩r,但這應(yīng)該作為一個(gè)獨(dú)立的主題,因?yàn)槲覀冸y以在一節(jié)中涵蓋其所有的內(nèi)容。因此,我們將著重介紹一些關(guān)鍵點(diǎn)。

CPU和GPU的主要區(qū)別在于它們的設(shè)計(jì)目標(biāo)。CPU的設(shè)計(jì)初衷是執(zhí)行順序指令[1]。一直以來,為提高順序執(zhí)行性能,CPU設(shè)計(jì)中引入了許多功能。其重點(diǎn)在于減少指令執(zhí)行時(shí)延,使CPU能夠盡可能快地執(zhí)行一系列指令。這些功能包括指令流水線、亂序執(zhí)行、預(yù)測執(zhí)行和多級緩存等(此處僅列舉部分)。

而GPU則專為大規(guī)模并行和高吞吐量而設(shè)計(jì),但這種設(shè)計(jì)導(dǎo)致了中等至高程度的指令時(shí)延。這一設(shè)計(jì)方向受其在視頻游戲、圖形處理、數(shù)值計(jì)算以及現(xiàn)如今的深度學(xué)習(xí)中的廣泛應(yīng)用所影響,所有這些應(yīng)用都需要以極高的速度執(zhí)行大量線性代數(shù)和數(shù)值計(jì)算,因此人們傾注了大量精力以提升這些設(shè)備的吞吐量。

我們來思考一個(gè)具體的例子:由于指令時(shí)延較低,CPU在執(zhí)行兩個(gè)數(shù)字相加的操作時(shí)比GPU更快。在按順序執(zhí)行多個(gè)這樣的計(jì)算時(shí),CPU能夠比GPU更快地完成。然而,當(dāng)需要進(jìn)行數(shù)百萬甚至數(shù)十億次這樣的計(jì)算時(shí),由于GPU具有強(qiáng)大的大規(guī)模并行能力,它將比CPU更快地完成這些計(jì)算任務(wù)。

我們可以通過具體數(shù)據(jù)來進(jìn)行說明。硬件在數(shù)值計(jì)算方面的性能以每秒浮點(diǎn)運(yùn)算次數(shù)(FLOPS)來衡量。NVIDIA的Ampere A100在32位精度下的吞吐量為19.5 TFLOPS。相比之下,Intel的24核處理器在32位精度下的吞吐量僅為0.66 TFLOPS(2021年)。同時(shí),隨時(shí)間推移,GPU與CPU在吞吐量性能上的差距逐年擴(kuò)大。

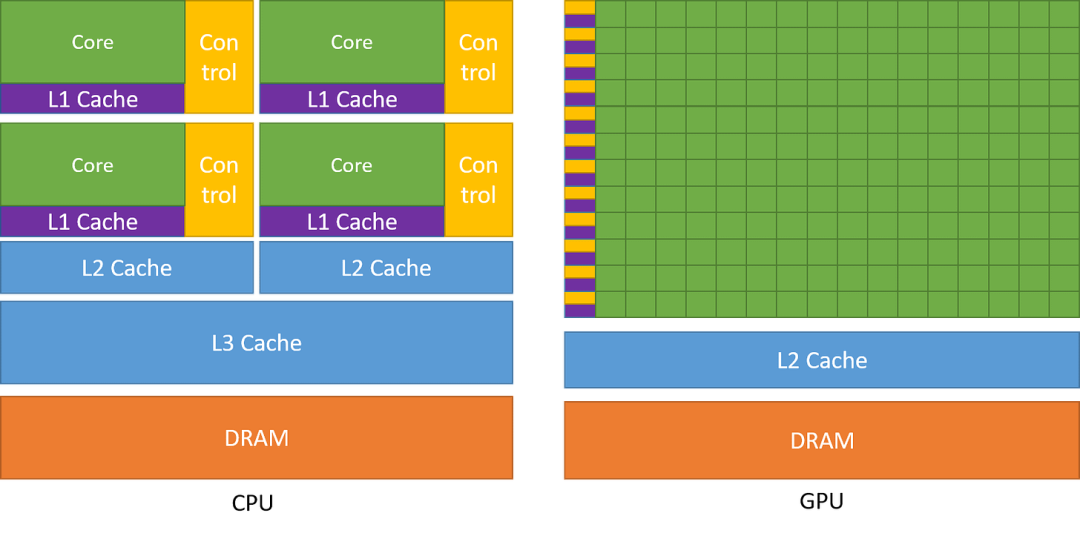

下圖對CPU和GPU的架構(gòu)進(jìn)行了比較。

圖1:CPU與GPU的芯片設(shè)計(jì)對比。引自《CUDA C++編程指南》(NVIDIA)

如圖所示,CPU在芯片領(lǐng)域中主要用于降低指令時(shí)延的功能,例如大型緩存、較少的算術(shù)邏輯單元(ALU)和更多的控制單元。與此相比,GPU則利用大量的ALU來最大化計(jì)算能力和吞吐量,只使用極小的芯片面積用于緩存和控制單元,這些元件主要用于減少CPU時(shí)延。

時(shí)延容忍度和高吞吐量

或許你會(huì)好奇,GPU如何能夠容忍高時(shí)延并同時(shí)提供高性能呢?GPU 擁有大量線程和強(qiáng)大的計(jì)算能力,使這一點(diǎn)成為可能。即使單個(gè)指令具有高延遲,GPU 也會(huì)有效地調(diào)度線程運(yùn)行,以便它們在任意時(shí)間點(diǎn)都能利用計(jì)算能力。例如,當(dāng)某些線程正在等待指令結(jié)果時(shí),GPU 將切換到運(yùn)行其他非等待線程。這可確保 GPU 上的計(jì)算單元在所有時(shí)間點(diǎn)都以其最大容量運(yùn)行,從而提供高吞吐量。稍后當(dāng)我們討論kernel如何在 GPU 上運(yùn)行時(shí),我們將對此有更清晰的了解。

02. GPU架構(gòu)

我們已經(jīng)了解到GPU有利于實(shí)現(xiàn)高吞吐量,但它們是通過怎樣的架構(gòu)來實(shí)現(xiàn)這一目標(biāo)的呢?本節(jié)將對此展開探討。

GPU的計(jì)算架構(gòu)

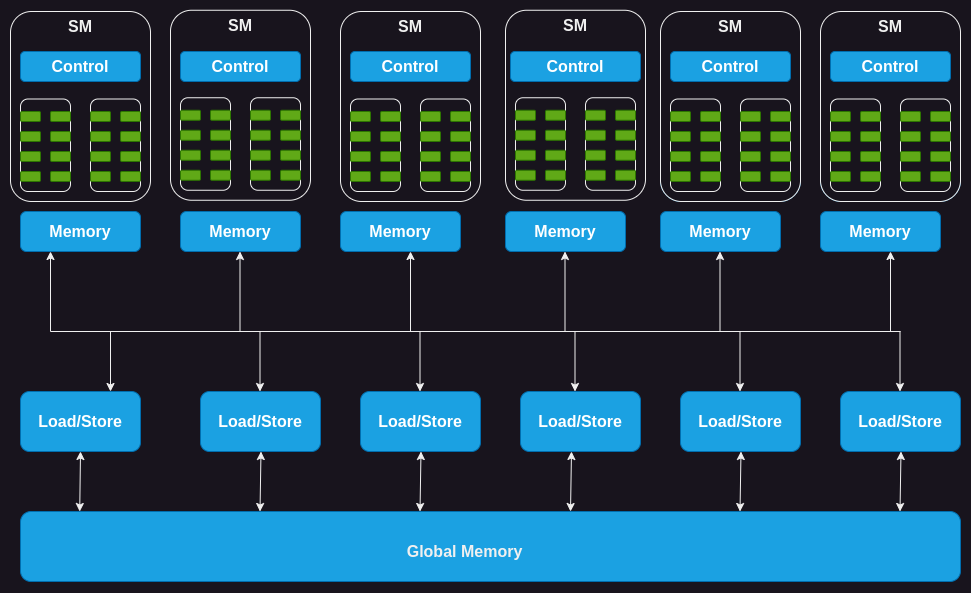

GPU由一系列流式多處理器(SM)組成,其中每個(gè)SM又由多個(gè)流式處理器、核心或線程組成。例如,NVIDIA H100 GPU具有132個(gè)SM,每個(gè)SM擁有64個(gè)核心,總計(jì)核心高達(dá)8448個(gè)。

每個(gè)SM都擁有一定數(shù)量的片上內(nèi)存(on-chip memory),通常稱為共享內(nèi)存或臨時(shí)存儲(chǔ)器,這些共享內(nèi)存被所有的核心所共享。同樣,SM上的控制單元資源也被所有的核心所共享。此外,每個(gè)SM都配備了基于硬件的線程調(diào)度器,用于執(zhí)行線程。

除此之外,每個(gè)SM還配備了幾個(gè)功能單元或其他加速計(jì)算單元,例如張量核心(tensor core)或光線追蹤單元(ray tracing unit),用于滿足GPU所處理的工作負(fù)載的特定計(jì)算需求。

圖2:GPU的計(jì)算架構(gòu)

接下來,讓我們深入剖析GPU內(nèi)存并了解其中的細(xì)節(jié)。

GPU的內(nèi)存架構(gòu)

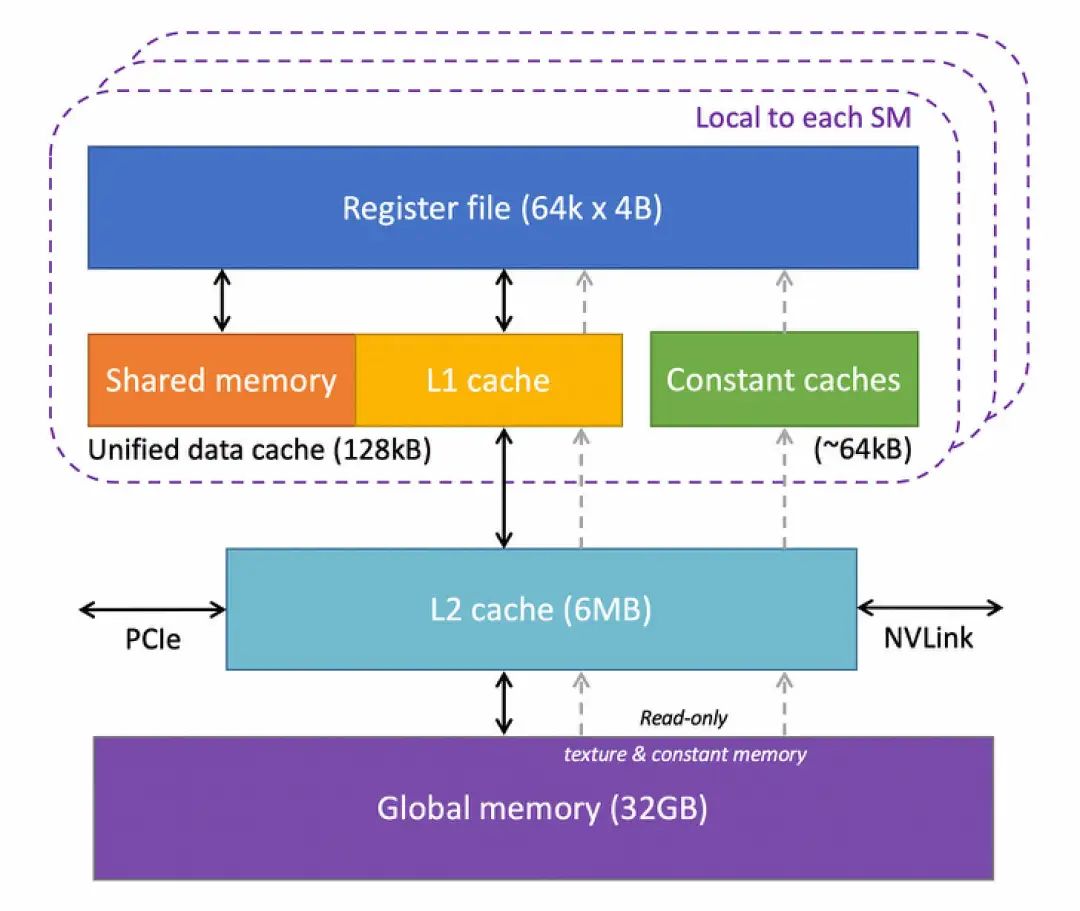

GPU具有多層不同類型的內(nèi)存,每一層都有其特定用途。下圖顯示了GPU中一個(gè)SM的內(nèi)存層次結(jié)構(gòu)。

圖3:基于康奈爾大學(xué)虛擬工作坊(Virtual Workshop)的GPU內(nèi)存架構(gòu)

讓我們對其進(jìn)行剖析:

寄存器:讓我們從寄存器開始。GPU中的每個(gè)SM都擁有大量寄存器。例如,NVIDIA的A100和H100模型中,每個(gè)SM擁有65536個(gè)寄存器。這些寄存器在核心之間共享,并根據(jù)線程需求動(dòng)態(tài)分配。在執(zhí)行過程中,每個(gè)線程都被分配了私有寄存器,其他線程無法讀取或?qū)懭脒@些寄存器。

常量緩存:接下來是芯片上的常量緩存。這些緩存用于緩存SM上執(zhí)行的代碼中使用的常量數(shù)據(jù)。為利用這些緩存,程序員需要在代碼中明確將對象聲明為常量,以便GPU可以將其緩存并保存在常量緩存中。

共享內(nèi)存:每個(gè)SM還擁有一塊共享內(nèi)存或臨時(shí)內(nèi)存,它是一種小型、快速且低時(shí)延的片上可編程SRAM內(nèi)存,供運(yùn)行在SM上的線程塊共享使用。共享內(nèi)存的設(shè)計(jì)思路是,如果多個(gè)線程需要處理相同的數(shù)據(jù),只需要其中一個(gè)線程從全局內(nèi)存(global memory)加載,而其他線程將共享這一數(shù)據(jù)。合理使用共享內(nèi)存可以減少從全局內(nèi)存加載重復(fù)數(shù)據(jù)的操作,并提高內(nèi)核執(zhí)行性能。共享內(nèi)存還可以用作線程塊(block)內(nèi)的線程之間的同步機(jī)制。

L1緩存:每個(gè)SM還擁有一個(gè)L1緩存,它可以緩存從L2緩存中頻繁訪問的數(shù)據(jù)。

L2緩存:所有SM都共享一個(gè)L2緩存,它用于緩存全局內(nèi)存中被頻繁訪問的數(shù)據(jù),以降低時(shí)延。需要注意的是,L1和L2緩存對于SM來說是公開的,也就是說,SM并不知道它是從L1還是L2中獲取數(shù)據(jù)。SM從全局內(nèi)存中獲取數(shù)據(jù),這類似于CPU中L1/L2/L3緩存的工作方式。

全局內(nèi)存:GPU還擁有一個(gè)片外全局內(nèi)存,它是一種容量大且?guī)捀叩膭?dòng)態(tài)隨機(jī)存取存儲(chǔ)器(DRAM)。例如,NVIDIA H100擁有80 GB高帶寬內(nèi)存(HBM),帶寬達(dá)每秒3000 GB。由于與SM相距較遠(yuǎn),全局內(nèi)存的時(shí)延相當(dāng)高。然而,芯片上還有幾個(gè)額外的存儲(chǔ)層以及大量的計(jì)算單元有助于掩飾這種時(shí)延。

現(xiàn)在我們已經(jīng)了解GPU硬件的關(guān)鍵組成部分,接下來我們深入一步,了解執(zhí)行代碼時(shí)這些組件是如何發(fā)揮作用的。

03. 了解GPU的執(zhí)行模型

要理解GPU如何執(zhí)行kernel,我們首先需要了解什么是kernel及其配置。

CUDA Kernel與線程塊簡介

CUDA是NVIDIA提供的編程接口,用于編寫運(yùn)行在其GPU上的程序。在CUDA中,你會(huì)以類似于C/C++函數(shù)的形式來表達(dá)想要在GPU上運(yùn)行的計(jì)算,這個(gè)函數(shù)被稱為kernel。kernel在并行中操作向量形式的數(shù)字,這些數(shù)字以函數(shù)參數(shù)的形式提供給它。一個(gè)簡單的例子是執(zhí)行向量加法的kernel,即接受兩個(gè)向量作為輸入,逐元素相加,并將結(jié)果寫入第三個(gè)向量。

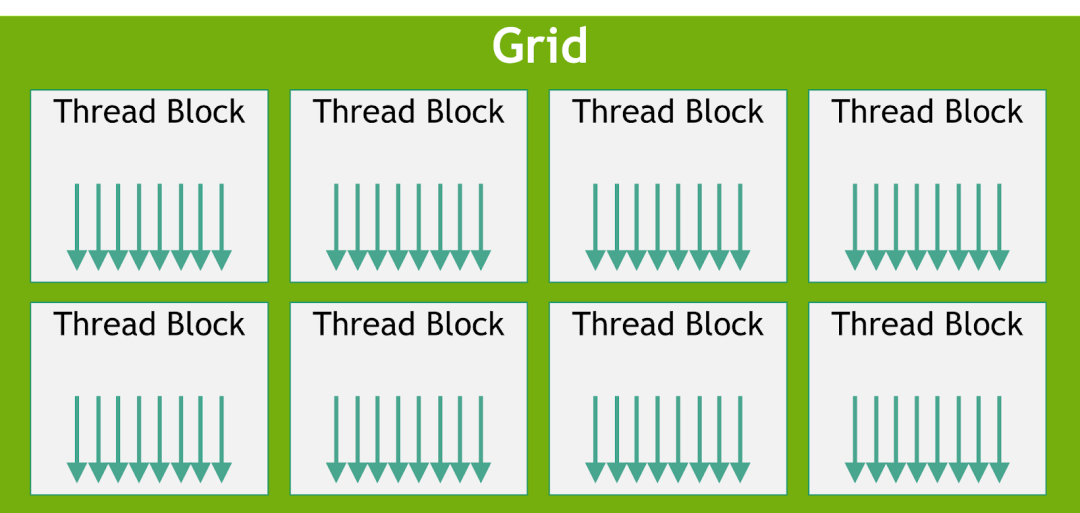

要在GPU上執(zhí)行kernel,我們需要啟用多個(gè)線程,這些線程總體上被稱為一個(gè)網(wǎng)格(grid),但網(wǎng)格還具有更多的結(jié)構(gòu)。一個(gè)網(wǎng)格由一個(gè)或多個(gè)線程塊(有時(shí)簡稱為塊)組成,而每個(gè)線程塊又由一個(gè)或多個(gè)線程組成。

線程塊和線程的數(shù)量取決于數(shù)據(jù)的大小和我們所需的并行度。例如,在向量相加的示例中,如果我們要對256維的向量進(jìn)行相加運(yùn)算,那么可以配置一個(gè)包含256個(gè)線程的單個(gè)線程塊,這樣每個(gè)線程就可以處理向量的一個(gè)元素。如果數(shù)據(jù)更大,GPU上也許沒有足夠的線程可用,這時(shí)我們可能需要每個(gè)線程能夠處理多個(gè)數(shù)據(jù)點(diǎn)。

圖4:線程塊網(wǎng)格。引自《CUDA C++編程指南》(NVIDIA)

編寫一個(gè)kernel需要兩步。第一步是運(yùn)行在CPU上的主機(jī)代碼,這部分代碼用于加載數(shù)據(jù),為GPU分配內(nèi)存,并使用配置的線程網(wǎng)格啟動(dòng)kernel;第二步是編寫在GPU上執(zhí)行的設(shè)備(GPU)代碼。

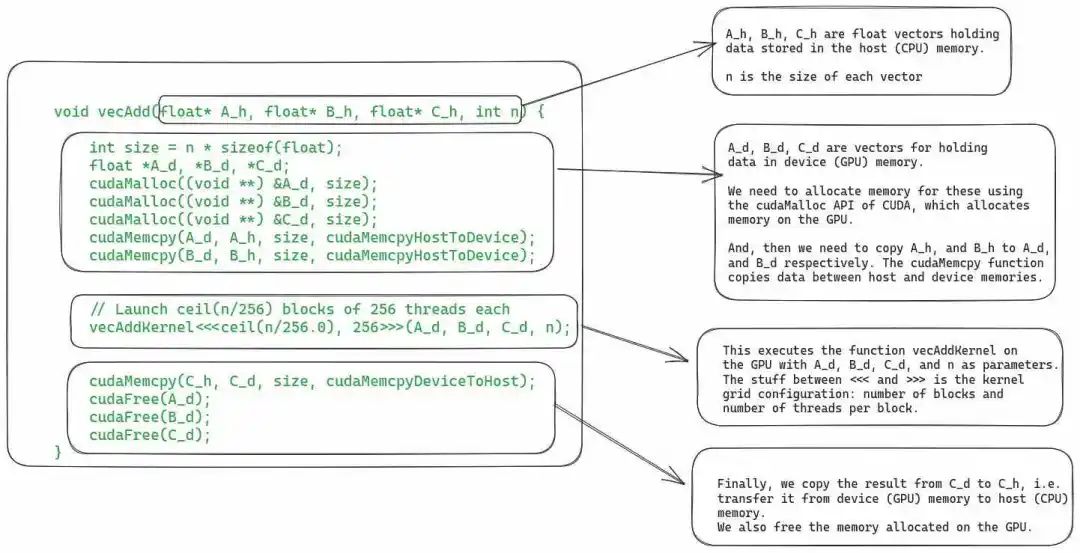

對于向量加法示例,下圖顯示了主機(jī)代碼。

圖 5:CUDA kernel的主機(jī)代碼,用于將兩個(gè)向量相加。

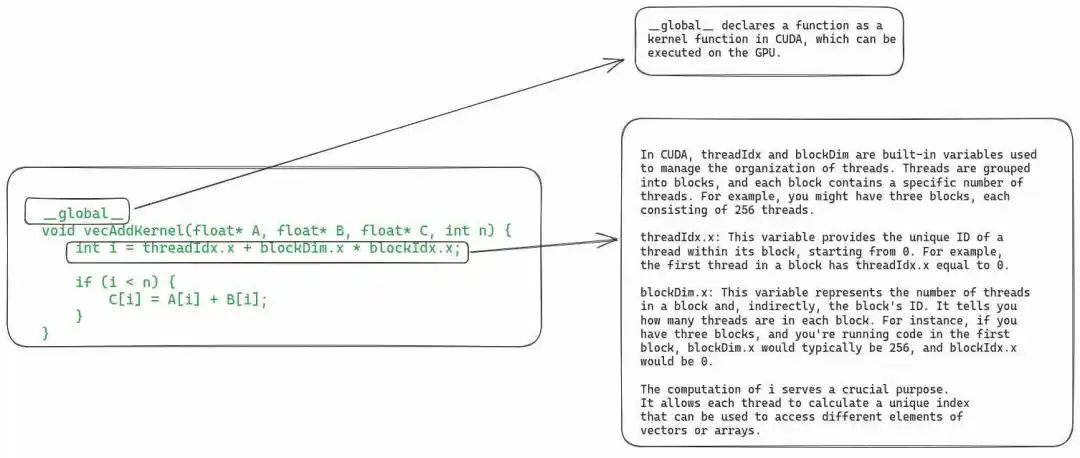

下圖為設(shè)備代碼,它定義了實(shí)際的kernel函數(shù)。

圖 6:包含向量相加kernel定義的設(shè)備代碼。

由于本文的重點(diǎn)不在于教授CUDA,因此我們不會(huì)更深入地討論此段代碼。現(xiàn)在,讓我們看看在GPU上執(zhí)行kernel的具體步驟。

04. 在GPU上執(zhí)行Kernel的步驟

1. 將數(shù)據(jù)從主機(jī)復(fù)制到設(shè)備

在調(diào)度執(zhí)行kernel之前,必須將其所需的全部數(shù)據(jù)從主機(jī)(即CPU)內(nèi)存復(fù)制到GPU的全局內(nèi)存(即設(shè)備內(nèi)存)。盡管如此,在最新的GPU硬件中,我們還可以使用統(tǒng)一虛擬內(nèi)存直接從主機(jī)內(nèi)存中讀取數(shù)據(jù)(可參閱論文《EMOGI: Efficient Memory-access for Out-of-memory Graph-traversal in GPUs》)。

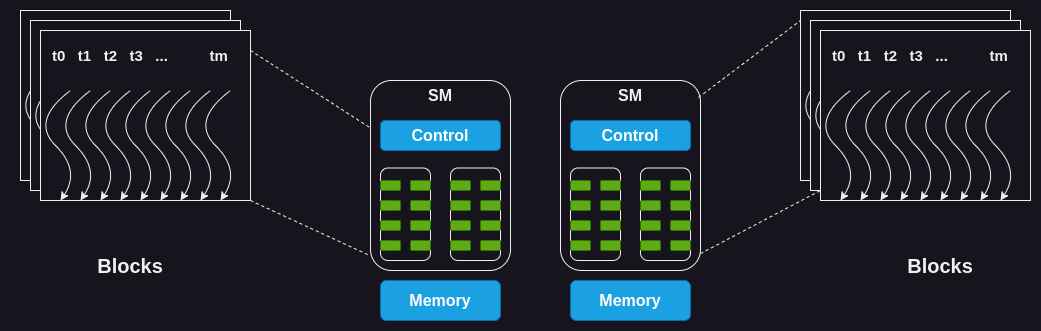

2. SM上線程塊的調(diào)度

當(dāng)GPU的內(nèi)存中擁有全部所需的數(shù)據(jù)后,它會(huì)將線程塊分配給SM。同一個(gè)塊內(nèi)的所有線程將同時(shí)由同一個(gè)SM進(jìn)行處理。為此,GPU必須在開始執(zhí)行線程之前在SM上為這些線程預(yù)留資源。在實(shí)際操作中,可以將多個(gè)線程塊分配給同一個(gè)SM以實(shí)現(xiàn)并行執(zhí)行。

圖 7:將線程塊分配給SM

由于SM的數(shù)量有限,而大型kernel可能包含大量線程塊,因此并非所有線程塊都可以立即分配執(zhí)行。GPU會(huì)維護(hù)一個(gè)待分配和執(zhí)行的線程塊列表,當(dāng)有任何一個(gè)線程塊執(zhí)行完成時(shí),GPU會(huì)從該列表中選擇一個(gè)線程塊執(zhí)行。

單指令多線程 (SIMT) 和線程束(Warp)

眾所周知,一個(gè)塊(block)中的所有線程都會(huì)被分配到同一個(gè)SM上。但在此之后,線程還會(huì)進(jìn)一步劃分為大小為32的組(稱為warp[2]),并一起分配到一個(gè)稱為處理塊(processing block)的核心集合上進(jìn)行執(zhí)行。

SM通過獲取并向所有線程發(fā)出相同的指令,以同時(shí)執(zhí)行warp中的所有線程。然后這些線程將在數(shù)據(jù)的不同部分,同時(shí)執(zhí)行該指令。在向量相加的示例中,一個(gè)warp中的所有線程可能都在執(zhí)行相加指令,但它們會(huì)在向量的不同索引上進(jìn)行操作。

由于多個(gè)線程同時(shí)執(zhí)行相同的指令,這種warp的執(zhí)行模型也稱為單指令多線程 (SIMT)。這類似于CPU中的單指令多數(shù)據(jù)(SIMD)指令。

Volta及其之后的新一代GPU引入了一種替代指令調(diào)度的機(jī)制,稱為獨(dú)立線程調(diào)度(Independent Thread Scheduling)。它允許線程之間完全并發(fā),不受warp的限制。獨(dú)立線程調(diào)度可以更好地利用執(zhí)行資源,也可以作為線程之間的同步機(jī)制。本文不會(huì)涉及獨(dú)立線程調(diào)度的相關(guān)內(nèi)容,但你可以在CUDA編程指南中了解更多相關(guān)信息。

4. Warp調(diào)度和時(shí)延容忍度

關(guān)于warp的運(yùn)行原理,有一些值得討論的有趣之處。

即使SM內(nèi)的所有處理塊(核心組)都在處理warp,但在任何給定時(shí)刻,只有其中少數(shù)塊正在積極執(zhí)行指令。因?yàn)镾M中可用的執(zhí)行單元數(shù)量是有限的。

有些指令的執(zhí)行時(shí)間較長,這會(huì)導(dǎo)致warp需要等待指令結(jié)果。在這種情況下,SM會(huì)將處于等待狀態(tài)的warp休眠,并執(zhí)行另一個(gè)不需要等待任何結(jié)果的warp。這使得GPU能夠最大限度地利用所有可用計(jì)算資源,并提高吞吐量。

零計(jì)算開銷調(diào)度:由于每個(gè)warp中的每個(gè)線程都有自己的一組寄存器,因此SM從執(zhí)行一個(gè)warp切換到另一個(gè)warp時(shí)沒有額外計(jì)算開銷。

與CPU上進(jìn)程之間的上下文切換方式(context-switching)不同。如果一個(gè)進(jìn)程需要等待一個(gè)長時(shí)間運(yùn)行的操作,CPU在此期間會(huì)在該核心上調(diào)度執(zhí)行另一個(gè)進(jìn)程。然而,在CPU中進(jìn)行上下文切換的代價(jià)昂貴,這是因?yàn)镃PU需要將寄存器狀態(tài)保存到主內(nèi)存中,并恢復(fù)另一個(gè)進(jìn)程的狀態(tài)。

5. 將結(jié)果數(shù)據(jù)從設(shè)備復(fù)制到主機(jī)內(nèi)存

最后,當(dāng)kernel的所有線程都執(zhí)行完畢后,最后一步就是將結(jié)果復(fù)制回主機(jī)內(nèi)存。

盡管我們涵蓋了有關(guān)典型kernel執(zhí)行的全部內(nèi)容,但還有一點(diǎn)值得討論:動(dòng)態(tài)資源分區(qū)。

05. 資源劃分和占用概念

我們通過一個(gè)稱為“occupancy(占用率)”的指標(biāo)來衡量GPU資源的利用率,它表示分配給SM的warp數(shù)量與SM所能支持的最大warp數(shù)量之間的比值。為實(shí)現(xiàn)最大吞吐量,我們希望擁有100%的占用率。然而,在實(shí)踐中,由于各種約束條件,這并不容易實(shí)現(xiàn)。

為什么我們無法始終達(dá)到100%的占用率呢?SM擁有一組固定的執(zhí)行資源,包括寄存器、共享內(nèi)存、線程塊槽和線程槽。這些資源根據(jù)需求和GPU的限制在線程之間進(jìn)行動(dòng)態(tài)劃分。例如,在NVIDIA H100上,每個(gè)SM可以處理32個(gè)線程塊、64個(gè)warp(即2048個(gè)線程),每個(gè)線程塊擁有1024個(gè)線程。如果我們啟動(dòng)一個(gè)包含1024個(gè)線程的網(wǎng)格,GPU將把2048個(gè)可用線程槽劃分為2個(gè)線程塊。

動(dòng)態(tài)分區(qū)vs固定分區(qū):動(dòng)態(tài)分區(qū)能夠更為有效地利用GPU的計(jì)算資源。相比之下,固定分區(qū)為每個(gè)線程塊分配了固定數(shù)量的執(zhí)行資源,這種方式并不總是最有效的。在某些情況下,固定分區(qū)可能會(huì)導(dǎo)致線程被分配多于其實(shí)際需求的資源,造成資源浪費(fèi)和吞吐量降低。

下面我們通過一個(gè)例子說明資源分配對SM占用率的影響。假設(shè)我們使用32個(gè)線程的線程塊,并需要總共2048個(gè)線程,那么我們將需要64個(gè)這樣的線程塊。然而,每個(gè)SM一次只能處理32個(gè)線程塊。因此,即使一個(gè)SM可以運(yùn)行2048個(gè)線程,但它一次也只能同時(shí)運(yùn)行1024個(gè)線程,占用率僅為50%。

同樣地,每個(gè)SM具有65536個(gè)寄存器。要同時(shí)執(zhí)行2048個(gè)線程,每個(gè)線程最多有32個(gè)寄存器(65536/2048 =32)。如果一個(gè)kernel需要每個(gè)線程有64個(gè)寄存器,那么每個(gè)SM只能運(yùn)行1024個(gè)線程,占用率同樣為50%。

占用率不足的挑戰(zhàn)在于,可能無法提供足夠的時(shí)延容忍度或所需的計(jì)算吞吐量,以達(dá)到硬件的最佳性能。

高效創(chuàng)建GPU kernel是一項(xiàng)復(fù)雜任務(wù)。我們必須合理分配資源,在保持高占用率的同時(shí)盡量降低時(shí)延。例如,擁有大量寄存器可以加快代碼的運(yùn)行速度,但可能會(huì)降低占用率,因此謹(jǐn)慎優(yōu)化代碼至關(guān)重要。

06. 總結(jié)

我理解眾多的新術(shù)語和新概念可能令讀者望而生畏,因此文章最后對要點(diǎn)進(jìn)行了總結(jié),以便快速回顧。

GPU由多個(gè)SM組成,每個(gè)SM又包含多個(gè)處理核心。

GPU上存在著一個(gè)片外全局內(nèi)存,通常是高帶寬內(nèi)存(HBM)或動(dòng)態(tài)隨機(jī)存取內(nèi)存(DRAM)。它與芯片上的SM相距較遠(yuǎn),因此時(shí)延較高。

GPU中有兩個(gè)級別的緩存:片外L2緩存和片上L1緩存。L1和L2緩存的工作方式類似于CPU中的L1/L2緩存。

每個(gè)SM上都有一小塊可配置的共享內(nèi)存。這塊共享內(nèi)存在處理核心之間共享。通常情況下,線程塊內(nèi)的線程會(huì)將一段數(shù)據(jù)加載到共享內(nèi)存中,并在需要時(shí)重復(fù)使用,而不是每次再從全局內(nèi)存中加載。

每個(gè)SM都有大量寄存器,寄存器會(huì)根據(jù)線程需求進(jìn)行劃分。NVIDIA H100每個(gè)SM有65536個(gè)寄存器。

在GPU上執(zhí)行kernel時(shí),我們需要啟動(dòng)一個(gè)線程網(wǎng)格。網(wǎng)格由一個(gè)或多個(gè)線程塊組成,而每個(gè)線程塊又由一個(gè)或多個(gè)線程組成。

根據(jù)資源可用性,GPU會(huì)分配一個(gè)或多個(gè)線程塊在SM上執(zhí)行。同一個(gè)線程塊中的所有線程都會(huì)被分配到同一個(gè)SM上執(zhí)行。這樣做的目的是為了充分利用數(shù)據(jù)的局部性(data locality),并實(shí)現(xiàn)線程之間的同步。

被分配給SM的線程進(jìn)一步分為大小為32的組,稱為warp。一個(gè)warp內(nèi)的所有線程同時(shí)執(zhí)行相同的指令,但在數(shù)據(jù)的不同部分上執(zhí)行(SIMT)(盡管新一代GPU也支持獨(dú)立的線程調(diào)度)。

GPU根據(jù)每個(gè)線程的需求和SM的限制,在線程之間進(jìn)行動(dòng)態(tài)資源劃分。程序員需要仔細(xì)優(yōu)化代碼,以確保在執(zhí)行過程中達(dá)到最高的SM占用率。

審核編輯:湯梓紅

-

處理器

+關(guān)注

關(guān)注

68文章

19408瀏覽量

231186 -

cpu

+關(guān)注

關(guān)注

68文章

10903瀏覽量

213018 -

gpu

+關(guān)注

關(guān)注

28文章

4775瀏覽量

129357 -

深度學(xué)習(xí)

+關(guān)注

關(guān)注

73文章

5515瀏覽量

121551

原文標(biāo)題:GPU架構(gòu)與計(jì)算入門指南

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

聊聊Rust與C語言交互的具體步驟

【「算力芯片 | 高性能 CPU/GPU/NPU 微架構(gòu)分析」閱讀體驗(yàn)】--了解算力芯片GPU

CPU和GPU擅長和不擅長的地方

CPU和GPU擅長和不擅長的地方

請問UCGUI中移植觸摸的具體步驟是什么?

請問matlab生成TMS C6747可執(zhí)行的代碼具體步驟是什么?

LiteOS在RISC-V架構(gòu)上的適配過程的具體步驟有哪些

MAVLink學(xué)習(xí)之路04_MAVLink移植到STM32具體步驟

西門子V20變頻器PID控制恒壓供水的具體步驟

CPU與GPPU架構(gòu)比較分析 在GPU上執(zhí)行Kernel的具體步驟

CPU與GPPU架構(gòu)比較分析 在GPU上執(zhí)行Kernel的具體步驟

評論