Analog On Top的SOC如何做Top設計?

簡介:

在片上系統(SOC)的世界里,模擬運算(AOT)方法為設計過程帶來了獨特的風味。與數字邏輯處于頂端的傳統方法不同,AOT顛覆了層次結構,模擬組件占據主導地位。本文旨在詳細了解如何為AOT SOC設計Top,并在此過程中提供重要的見解和注意事項。

1.了解AOT SOC架構:

AOT SOC架構的特點是將模擬組件放在頂部,然后是下面的數字邏輯塊。這種布置允許更好的連接性、減少噪聲干擾和最小化信號退化。關鍵模擬組件包括ADC、DAC、PLL、LDO和特定于應用程序的自定義模擬模塊。

2.確定模擬性能要求:

在深入頂層設計之前,確定模擬組件的性能要求至關重要。必須徹底分析噪聲、線性、帶寬、功耗和熱特性等參數。仔細考慮這些要求將有助于做出適當的設計決策。

3.定義通信接口:

接下來,需要定義數字域和模擬域之間的通信接口。這涉及到選擇合適的協議并設計用于電壓和信號轉換的緩沖器或電平移位器。重要的是要確保數字邏輯在適當的電壓電平下工作,并且在轉換期間信號不被破壞。

4.設計模擬塊:

設計模擬塊包括選擇合適的電路拓撲、確定晶體管大小和設計布局結構。模擬塊應小心放置和布線,以最大限度地減少寄生效應并確保信號完整性。原理圖捕獲工具,如Cadence Virtuoso,可用于創建初始電路設計。

5.布局設計:

頂部布局應考慮模擬組件的獨特要求。必須結合足夠的間距、屏蔽和專門的模擬電源/接地網絡設計。AOT SOC對敏感的模擬信號給予更高的優先級,因此必須小心將任何可能降低性能的潛在耦合或串擾問題降至最低。

6.配電網規劃:

由于模擬部件對噪聲的敏感性,AOT SOC的PDN至關重要。每個模擬塊都需要一個專用的LDO或一個隔離的電源域,以確保干凈穩定的電源。應戰略性地放置適當的去耦電容器和電感器,以抑制噪聲并保持信號完整性。

7.信號完整性和串擾分析:

為了保證最佳性能,必須在AOT SOC設計中對信號完整性進行深入分析。EMXPert和Spice等工具可以幫助識別潛在的串擾和噪聲耦合問題。在分析過程中發現的任何設計問題都應及時解決,同時牢記對模擬性能的影響。

8.模擬和驗證:

仿真工具,如Cadence Spectre或Synopsys HSPICE,對于驗證整體系統級性能至關重要。每個模擬塊都應該單獨模擬,然后必須將整個SOC作為一個整體進行模擬,以評估模擬域和數字域之間的相互作用。模擬行為建模(ABM)可以用于快速準確的模擬。

9.制造設計(DFM):

在AOT SOC中,不應忽視DFM考慮因素。必須注意確保模擬塊滿足工藝變化,對溫度變化具有魯棒性,并保持制造成品率。適當的靈敏度分析和蒙特卡羅模擬將有助于識別任何需要注意的關鍵領域。

10.硅后驗證:

一旦SOC設計完成,就必須進行硅后驗證,以驗證模擬性能是否符合所需規范。應仔細規劃測試設置和方法,以確保準確測量噪聲、線性和效率等參數,為SOC設計的成功提供證據。

結論:

為模擬On Top SOC設計Top需要對細節給予細致的關注,并對模擬性能要求有全面的了解。從確定性能規范到設計布局和進行硅后驗證,每一步都在確保SOC的最佳性能方面發揮著至關重要的作用。通過遵循本文提供的指導方針,設計師可以有效應對挑戰,并成功實現AOT SOC。

-

片上系統

+關注

關注

0文章

186瀏覽量

26881 -

隔離電源

+關注

關注

6文章

285瀏覽量

36374 -

DFM

+關注

關注

8文章

465瀏覽量

28362

發布評論請先 登錄

相關推薦

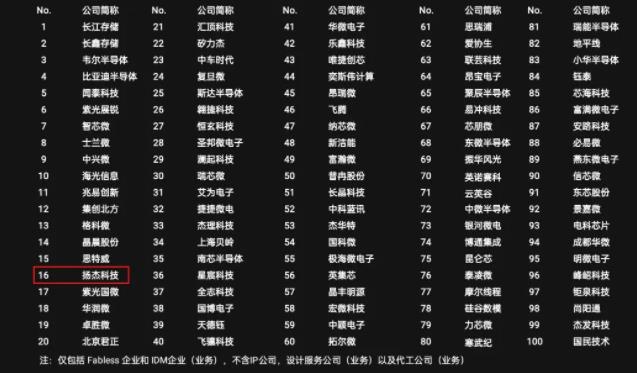

揚杰科技登榜“2024中國半導體企業TOP100”

Analog On Top的SOC如何做Top設計?

Analog On Top的SOC如何做Top設計?

評論