【設計要求】

實現占空比為50%的奇數分頻器(示例以三分頻為例).

【原理分析】

在進行數字電路設計的過程中,分頻器是設計中使用頻率較高的一種基本設計之一,雖然很多廠家都提供特定的電路模塊對時鐘進行分頻、倍頻以及特定相移等,但是對于時鐘要求不高的邏輯,特別是在仿真過程中,使用硬件描述語言實現分頻還是較為方便快捷的,同時通過硬件描述語言實現的時鐘分頻器對于鞏固和加深對于硬件描述語言理解不無裨益.

常用的分頻器有偶數分頻和奇數分頻,因為偶數分頻相較奇數分頻實現較為方便,此處路過不進行贅述.而奇數分頻又有占空比(占空比是指在一個脈沖循環內,高電平持續時間在所在整個周期中占據的比例)為50%和不為50%的情況,為了加深理解,本文僅以占空比為50%的奇數分頻為例進行說明.

占空比為50%的奇數分頻器:當需要進行(2N+1)分頻時,偶數分頻所使用的的方法已經不適用了,這是因為2N+1的一半是N+0.5,單獨對一個時鐘計數是得不到0.5個時鐘,因為一個計數器只能在時鐘的上升沿或者下降沿被采樣,所以一個周期之內只能計數一次,無法得到0.5個計數.但是需要注意的是在一個時鐘周期內時鐘上升沿和下降沿之間剛好相差0.5個時鐘周期.

那么結合上升沿和下降沿相差的0.5個時鐘周期,就可以得到設計奇數分頻器的思路:采用兩個完全一樣的時鐘,其中一個計數器通過上升沿計數,一個計數器通過下降沿計數,然后利用兩個計數器的計數值結合偶數分頻的方法分別得到兩個中間時鐘(兩個中間時鐘的相差為原時鐘周期的奇數倍),因為要獲取的最終的奇數分頻后的時鐘的半周期為原時鐘周期半周期的奇數倍,所以通過兩個中間時鐘進行邏輯操作,即可衍生出奇數倍個原時鐘的半周期,從而獲取到最終的時鐘.

即奇數分頻器的分頻出時鐘的特點是:時鐘周期的半周期為原時鐘周期半周期的奇數倍。

【源代碼】

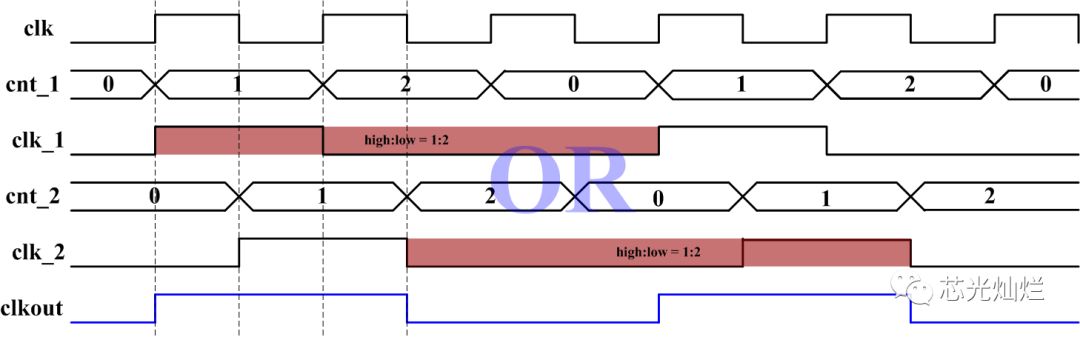

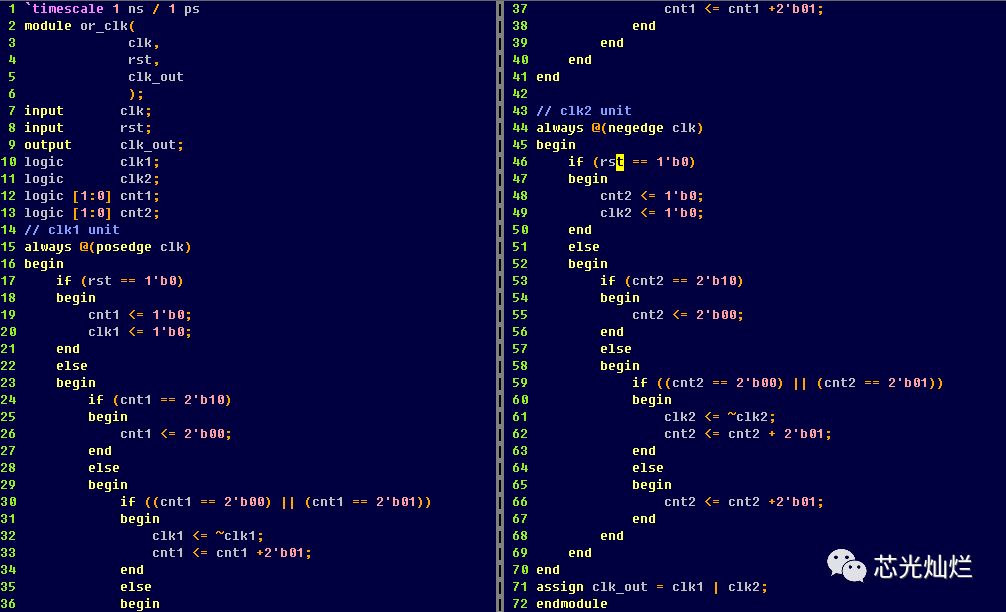

方法一:時鐘相或產生

第一步:分別使用原時鐘上升沿和下降沿產生兩個兩位計數器(基于上升沿計數的cnt1和基于下降沿計數的cnt2),計數器在計數到2(即2N)時,計數器歸零重新從零開始計數,依次循環;

第二步:cnt1計數到0或者計數到1(即N)時,clk1翻轉,從而得到占空比為1:3的clk1;

第三步:cnt2計數到0或者計數到1(即N)時,clk2翻轉,從而得到占空比為1:3的clk2;

第四步:因為clk1和clk2相差半個原時鐘周期,兩個中間時鐘進行或操作后,即可得到輸出時鐘clk_out;

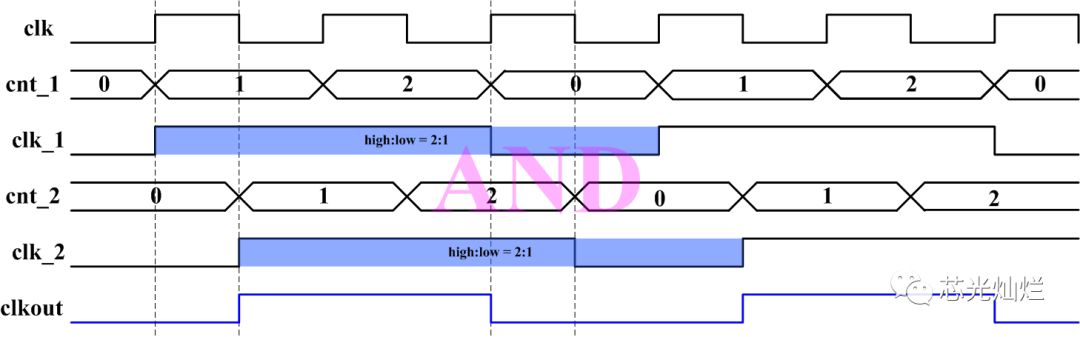

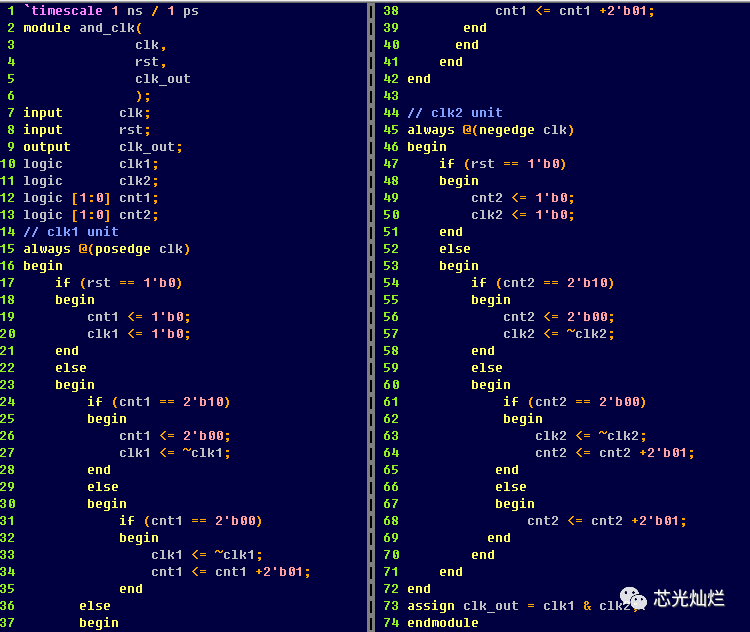

方法二:時鐘相與產生

第一步:分別使用原時鐘上升沿和下降沿產生兩個兩位計數器(基于上升沿計數的cnt1和基于下降沿計數的cnt2),計數器在計數到2(即2N)時,計數器歸零重新從零開始計數,依次循環.

第二步:cnt1計數到0或者計數到2(即2N)時,clk1翻轉,從而得到占空比為2:3的clk1;

第三步:cnt2計數到0或者計數到2(即2N)時,clk2翻轉,從而得到占空比為2:3的clk2;

第四步:因為clk1和clk2相差半個原時鐘周期,兩個中間時鐘進行與操作后,即可得到輸出時鐘clk_out;

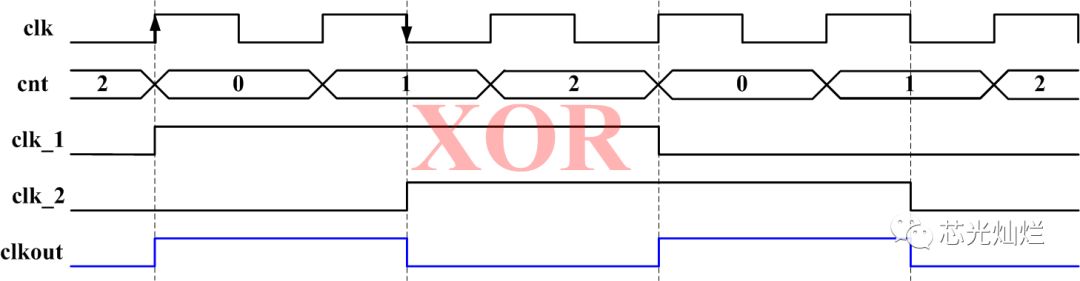

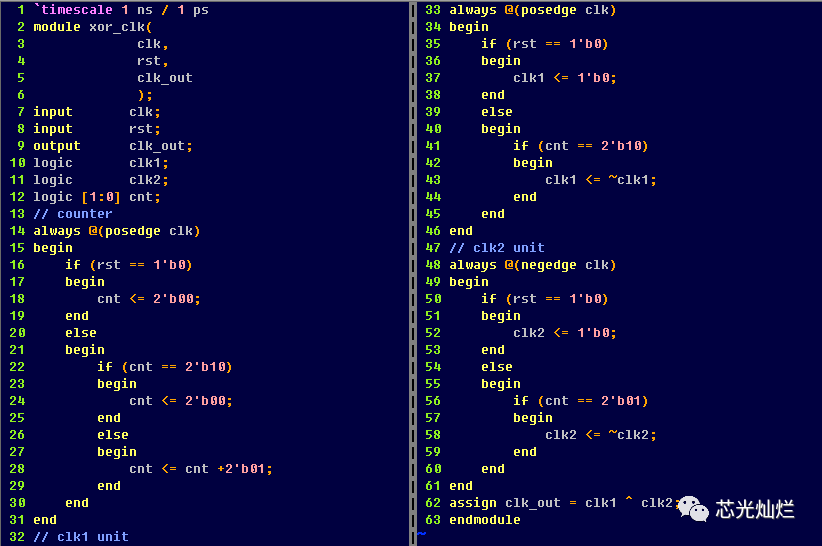

方法三:時鐘異或產生

第一步:實現計數功能;

通過時鐘上升沿實現計數器功能,在計數到2(即2N)時,計數器歸零重新從零開始計數,依次循環;

第二步:上升沿產生中間時鐘clk1;

在計數器計數到2時,clk1翻轉,實現周期為6(2*(2N+1))的clk1;

第三步: 下降沿產生中間時鐘clk2

時鐘下降沿采樣計數器的計數值,在計數器計數到1(N)時,clk2翻轉,實現周期為6的clk2,此時clk1和clk2相位差為1(N)個原時鐘周期加半個愿時鐘周期;

第四步:clk1和clk2異或,即可得到輸出時鐘clk_out;

前兩種方法使用了兩個計數器,最后一種方法使用了一個計數器.因為偶數分頻的半時鐘周期為原時鐘周期的偶數倍,奇數分頻時鐘周期的半周期為原來時鐘周期整數倍加半個時鐘周期,因此在進行奇數分頻時一定要注意獲取到原時鐘周期的半個周期,這樣才能在進行各種邏輯操作后獲取到期望的奇數分頻器.

【仿真結果】

【總結】

奇數分頻器實際上就是通過兩個分頻器輸出邏輯操作后獲得,關鍵點在于兩個分頻器需通過待分頻時鐘的上升沿和下降沿分別進行設計。

-

分頻器

+關注

關注

43文章

447瀏覽量

50075 -

計數器

+關注

關注

32文章

2261瀏覽量

94984 -

占空比

+關注

關注

0文章

109瀏覽量

29160 -

CLK

+關注

關注

0文章

127瀏覽量

17236

發布評論請先 登錄

相關推薦

奇數分頻如何得到呢? 解讀奇數分頻和邏輯分析儀(ILA)的使用

需要講解一個占空比50%的奇數分頻器的原理

基于FPGA 的等占空比任意整數分頻器的設計

分頻器的作用是什么 半整數分頻器原理圖分析

基于復雜可編程邏輯器件和VHDL語言實現半整數分頻器的設計

FPGA學習-分頻器設計

如何實現一種占空比為50%的奇數分頻器設計呢?

如何實現一種占空比為50%的奇數分頻器設計呢?

評論