時鐘抖動是相對于理想時鐘沿實際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動,可以用抖動頻率和抖動幅度對時鐘抖動進行定量描述。通常希望一個周期性波形(特別是時鐘)跨過特定門限的時間非常精確,與該理想值的偏差稱為抖動.

時鐘的抖動可以分為隨機抖動(random jitter,簡稱rj)和固有抖動(deterministic jitter),隨機抖動的來源為熱噪聲、shot noise和flick noise,與電子器件和半導體器件的電子和空穴特性有關,比如ecl工藝的pll比ttl和cmos工藝的pll有更小的隨機抖動;

固定抖動的來源為:開關電源噪聲、串擾、電磁干擾等等,與電路的設計有關,可以通過優化設計來改善,比如選擇合適的電源濾波方案、合理的pcb布局和布線。

在通信網絡、無線傳輸、CPRI和SONET等高速系統中,時鐘或振蕩器波形的時序誤差會限制一個數字I/O接口的最大速率。不僅如此,它還會導致通信鏈路的誤碼率增大,甚至限制A/D轉換器的動態范圍。

在數字系統中時鐘邊沿決定了每個基本單元的開始和結束時間。當抖動改變了時鐘邊沿從而導致時鐘周期變化時,每個基本單元的有效工作時間也會發生變化,可能會導致信號的建立時間和保持時間不能滿足要求,從而影響電路的正常工作。

當使用Serdes發送或者接收串行bit流時,時鐘是用于對傳輸的數據進行編碼,并將時鐘信息嵌入到傳輸的數據中。接收器會從傳輸的比特流中分離出單獨的時鐘,用于對數據進行采樣和捕捉。在該系統中累計抖動決定了bit到達與采樣之間的時間差,因此它是最重要的。

在模數轉換器(ADC)和數模轉換器(DAC)中,對信號的采樣可以轉換為信號與時鐘時域乘積。

時鐘決定了信號采樣時間,如果時鐘抖動導致采樣時間偏離了理想采樣時間,會導致采樣到的信號值相比于理想的信號值發生變化,從而惡化信噪比和動態范圍,降低轉換器的有效分辨率。

抖動可以通過許多方式測量(不同方式測量到的抖動被分別加以定義),以下是主要的抖動分類:周期抖動(Period Jitter);相鄰周期間的抖動(Cycle to Cycle Period Jitter);長時間抖動(Long Term Jitter);相位抖動(Phase Jitter);單位時間間隔抖動(TIE,Time Interval Error)。

周期抖動是時鐘信號的實際周期長度與理想周期長度之間的偏差,測量樣本為數目不定(隨機)的一組周期。如果給定一定數目的單個時鐘周期,我們就可以通過測量每個周期的長度并計算平均的周期長度,以及這些時鐘周期的標準差和峰峰值。

相鄰周期抖動,根據 JEDEC 標準 65B,是通過一定數量的相鄰周期隨機樣本的計算得出相鄰周期的時間變化。JEDEC 標準進一步規定:每個樣本的大小應大于或等于 1,000。相鄰周期抖動一般體現為以ps為單位的峰值,用于定義任意兩個連續時鐘上升沿之間的最大偏差。

此類型的抖動規范常用于體現擴頻時鐘的穩定性,因為周期抖動對頻率擴展特性更加敏感,而相鄰周期抖動則不然。時間間隔誤差 (TIE) 是指實際信號的事件邊沿時間點相對于理想信號的事件邊沿時間點的時間偏差。實際上,TIE 是相位噪聲頻譜在時域離散信號序列的表達,以秒或 ps 為單位。理想信號通常是信號處理軟件利用對實際信號周期的平均估算而得到的參考信號。

為成功地設計高速數字系統,不僅需要理解什么是抖動,計算抖動的大小,還需要對不同的抖動分量進行隔離和分解,分析造成抖動的原因,進而避免在高速系統中出現抖動造成的系統故障。在了解抖動測試前,明智選擇合適的抖動測試工具和方法成為整個抖動測試工作的第一步。

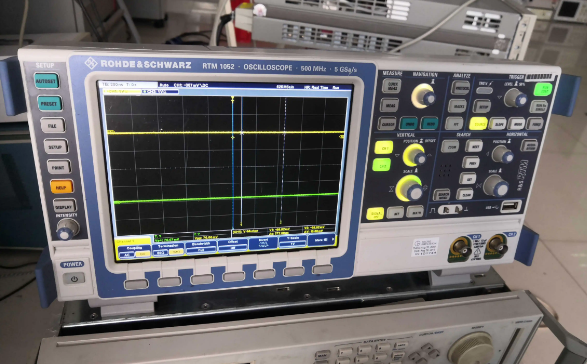

目前有幾種抖動測試工具可供選擇,誤碼儀(BERT)直接測試系統的誤碼率,但是價位昂貴,功能單一,不適合設計人員和調試人員;采用時間間隔分析儀測試抖動也存在功能單一,抖動分析能力不足的限制。高性能數字示波器成為當前最流行的抖動測試工具。示波器采樣系統中定時元件的穩定性直接影響著定時測量精度。

如果時基有誤差,那么基于該時基進行的測量會具有同等或更大的誤差。示波器中的時基穩定性包括參考時鐘、倍頻器、計數器等相關電路的穩定性。當通過實時采集模式進行抖動測試時,由于示波器工作在單次觸發模式,連續實時采集所有信號,所以它不受儀器多次觸發帶來的觸發抖動影響。

另外兩個誤差源分別是ADC孔徑不確定性和量化誤差。這些誤差可以表現為幅度噪聲和定時噪聲,具體取決于取樣數據使用的方式。很難區分該誤差的實際來源,因為模數轉換的時間不同。

抖動測試時不僅需要對示波器整體性能進行評估,例如示波器的帶寬,采樣率,還需要與之匹配的高采樣率下的采集內存長度,這樣才能測量從接近DC直流到儀器帶寬的抖動,同時保持各種相位和諧波關系,對被測信號的抖動有一個全面的分析。

時鐘抖動是設計中常見的問題,可能對系統的性能和可靠性產生負面影響為了減少時鐘偏差和抖動,我們需要選擇高質量的時鐘源,加強時鐘同步與校準,降低電磁干擾和噪聲,控制溫度變化,優化時鐘電路設計,以及使用時鐘補償技術通過遵循這些設計指導原則,可以提高系統的時鐘準確性和穩定性,確保系統的性能和可靠性。

-

IC設計

+關注

關注

38文章

1302瀏覽量

104280 -

時鐘抖動

+關注

關注

1文章

62瀏覽量

15969 -

數字示波器

+關注

關注

6文章

527瀏覽量

33697 -

數模轉換器

+關注

關注

14文章

1024瀏覽量

83374 -

倍頻器

+關注

關注

8文章

80瀏覽量

35621

發布評論請先 登錄

相關推薦

ADI推出業界最低抖動RF時鐘IC AD9525

正確理解時鐘器件的抖動性能

用模擬時鐘IC替代昂貴的高頻率VCO,改善抖動性能

時鐘抖動的影響

IC設計必須關注的時鐘抖動

IC設計必須關注的時鐘抖動

評論