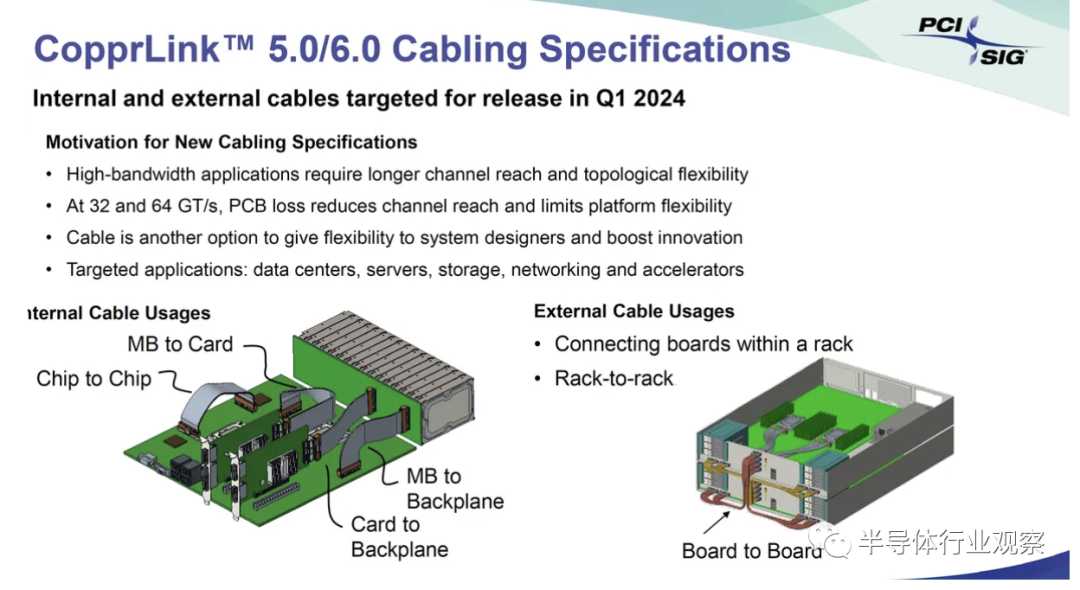

PCI SIG 本周表示,它正在開發 PCIe 5.0 和PCIe 6.0接口的布線規范,數據傳輸速率為 32 GT/s 和 64 GT/s。新的電纜規格將于 2024 年第一季度發布,并將命名為 CopprLink,可能是為了避免與現有OCuLink電纜混淆,并強調其銅質特性。

CopprLink 5.0 和 6.0 規范專為數據中心和服務器而設計。它們旨在連接主板到背板、卡到背板、主板到擴展卡(例如加速器)、機架到機架、機架內的板到板,甚至 PCIe 5.0 (32 GT/s) 和 PCIe 的芯片到芯片6.0 (64 GT/s) 速度。其目的是為印刷電路板上典型 PCIe 鏈路效率低下或由于某種原因無法建立的情況提供一些額外的靈活性。上述情況不包括長距離連接,因此我們這里討論的可能是幾十厘米。

由于噪聲和信號丟失,通過電纜以 32 GT/s 或 64 GT/s 的速度運行數據是一項艱巨的任務,但在許多情況下,電纜的使用是不可避免的,這就是業界開發 CopprLink 的原因。值得注意的是,PCI SIG 僅提及數據中心級應用,并未提及客戶端 PC 或汽車應用。也許,CopprLink 最終也會被這些應用采用(因為為什么不呢?),但目前 PCI SIG 還沒有提及它們。

關于 CopprLink 需要注意的另一件事是,該名稱暗示銅纜,而不是光纖互連,這是 PCI SIG 正在開發的另一個規范。也就是說,我們不能排除這樣的可能性:如果有需要并且光學 PCIe 規范尚未準備好,那么在某些時候有人會構建具有光學互連的 CopprLink 以實現更遠距離的連接。

PCIe 接口的普及需要不斷的發展,不僅是標準本身,還包括其布線規范。有用于消費類應用的基于 PCIe 協議的 Thunderbolt 和 USB4 技術,還有用于服務器和工作站的內部和外部 PCIe 3.0 和 PCIe 4.0 電纜連接的 OCuLink。CopprLink 是成熟的基于 PCIe 的互連系列的自然補充。

其實關于CopprLink ,PCI-SIG并沒有披露太多,但很多人認為,CopprLink 可能與帶寬改進和數據傳輸有關,而不一定用于供電,但它確實引起了人們對 12VHPWR 電纜或連接器的潛在繼任者可能是什么樣子的好奇。

從相關報道我們可以看到,OCuLink 是內部/外部 PCI 電纜技術的名稱,其規范涵蓋電信號方法(名稱的 Cu 部分,即銅)和光學版本(當然是 O 位)。它支持 PCIe 4.0,并使用多達八個通道來傳輸數據,但規范不包括電力傳輸。

盡管該公告沒有直接說明這一點,但我認為可以肯定地假設 CopprLink 將僅用于 PCIe 5.0 和 6.0 布線,而最適合這些的市場是 HPC 市場。不過,我認為它還有空間用于未來的項目,例如GDP G1)和最近的OneXGPU。

該單元配有一個外部 GPU、一個 M.2 SSD 和大量 IO 端口。一次性使用所有這些功能受到我們此類系統當前選項的極大限制,例如 USB4 Gen 2 或 OCuLink。簡而言之,它們無法提供足夠的帶寬來防止 GPU+SSD+IO 受到性能限制。

不過,具有 8 個 PCIe 5.0 通道的電纜應該具有足夠的帶寬,如果它還可以供電,那么這將是擴展筆記本電腦或手持設備功能的好方法。實現這一點有多容易完全是另一回事,因為 PCIe 5.0 在 PC 領域仍然相當新。

審核編輯:劉清

-

連接器

+關注

關注

98文章

14656瀏覽量

137238 -

加速器

+關注

關注

2文章

807瀏覽量

38087 -

PCIe接口

+關注

關注

0文章

121瀏覽量

9788

原文標題:PCIe重磅公布:用CopprLink 取代 OCuLink?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何選擇適合的PCIe配置

PCIe 4.0與3.0的區別 PCIe設備的故障排除方法

pcie 4.0與pcie 5.0的區別

pcie帶寬對計算性能的影響

PCIe與NVMe存儲的關系

如何測試PCIe插槽的速度

PCIe 4.0與PCIe 3.0的性能對比

PCIe接口的工作原理 PCIe與PCI的區別

家用電腦的PCIe接口如何設計PCB?

PCIe 5.0 SerDes 測試

pcie4.0和pcie3.0接口兼容嗎

PCIe:用CopprLink取代OCuLink?

PCIe:用CopprLink取代OCuLink?

評論