Hardware 設計

對于 Intel 平臺,自 ICL Lake 開始,就不再支持 LPC,僅支持 eSPI。

以 TGL 平臺為例,硬件設計上需要注意如下兩點。

一,Hardware Strap Pin

GPP_C5、GPP_H0、GPP_H1、GPP_H2,四個 pin 按順序組成 4-Bit Boot Strap Pin。配置規則如下表格:

| 0000 = Master Attached Flash Configuration (BIOS / CSME onSPI). eSPI is enabled |

|---|

| 0010 = Master Attached Flash Configuration (BIOS / CSME onSPI). eSPI is disabled |

| 0100 = BIOS on eSPI Peripheral Channel; CSME on masterattached SPI |

| 1000 = Slave Attached Flash Configuration (BIOS / CSME oneSPI attached device). |

| 1100 = BIOS on eSPI peripheral Channel; CSME on slaveattached SPI. |

常規設計都是 MAF,eSPI Enable。正常的配置需要 0000,四個 pin 內部都有 20K 的下拉,因此 Strap Pin 保持 Floating 即可。

注意:不同 CPU 平臺,Strap Pin 有差異,以對應平臺 EDS 文檔描述為準。

二,Flash Access

為了降低硬件設計 BOM 成本,CPU 設計上提出 MAF 和 SAF 兩種 Flash 共享方式,以節省 EC Flash。

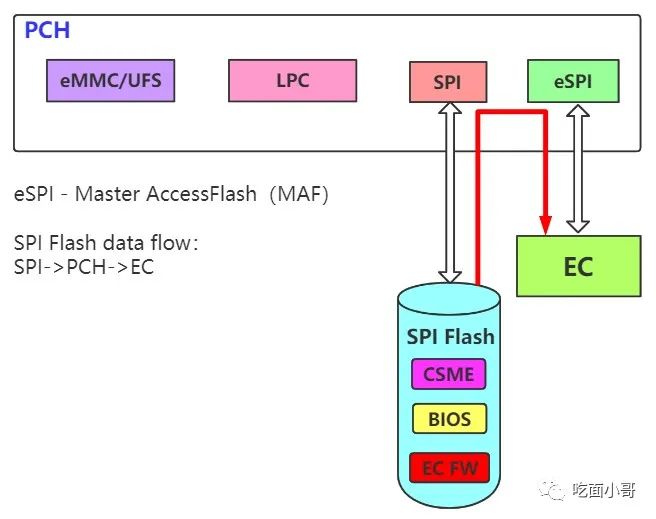

Master Attached Flash Sharing,如下圖。EC 通過 eSPI 訪問 PCH 下 SPI 總線上的 Flash,以獲取 EC Firmware。

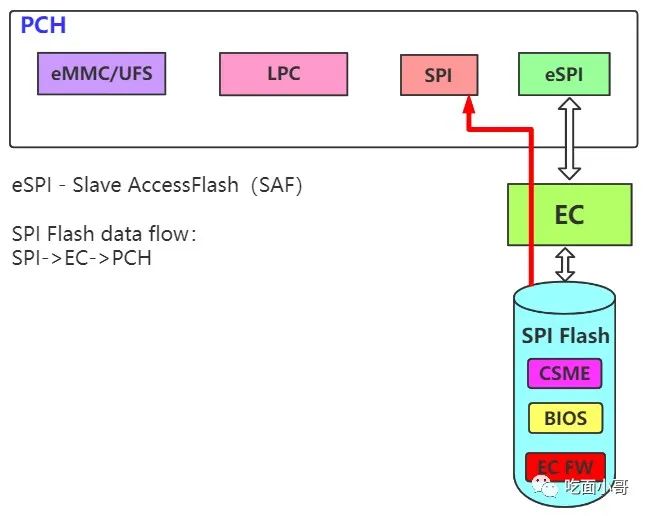

Slave Attached Flash Sharing,如下圖。PCH 通過 eSPI 透過 EC 訪問

BIOS、CSME Firmware。

對于 MAF 設計,需要保持 CPU 部分電打開,確保 PCH 內 eSPI 和 SPI 可以工作。EC 才有了透過 PCH eSPI Master 訪問 Flash 的基礎。

對于 SAF 設計,BIOS、CSME Firmware 體量大,PCH 透過 EC 訪問,對 EC SPI Controller 要求比較高。

事實上,PCH 通過 自己的 SPI Controller 獲取 BIOS、CSME,就稱之為 MAF。PCH 通過 eSPI 獲取 BIOS、CSME,就稱之為 SAF。

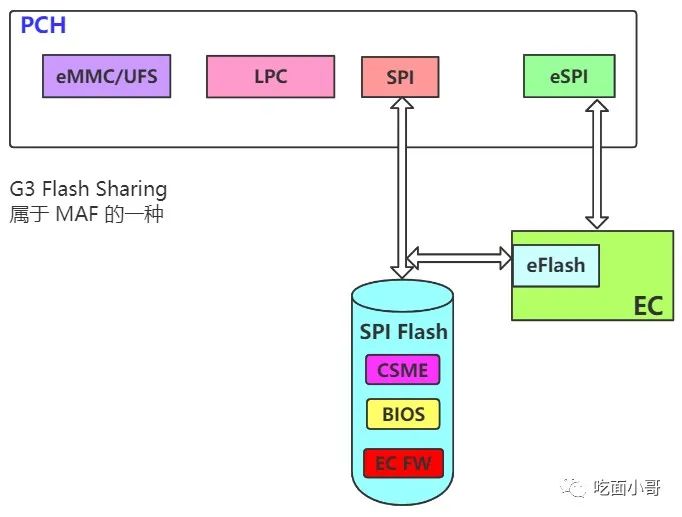

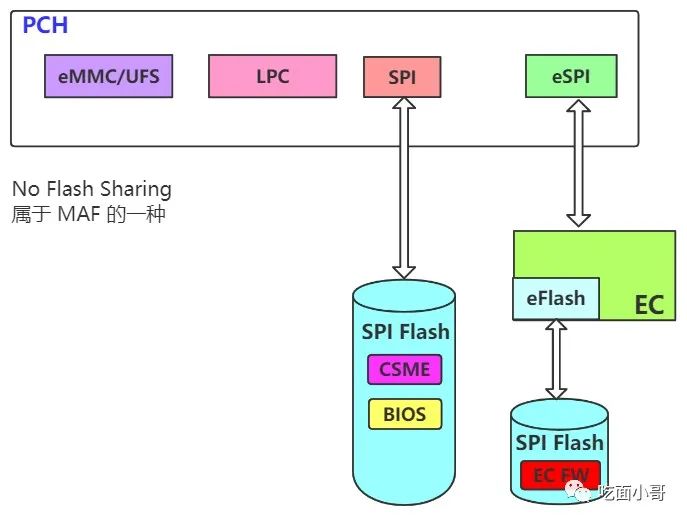

實際應用中,MAF 和 SAF 這兩種 Flash Sharing 方式都沒有采用。而是選擇

G3 Flash Sharing 或者 No Flash Sharing。

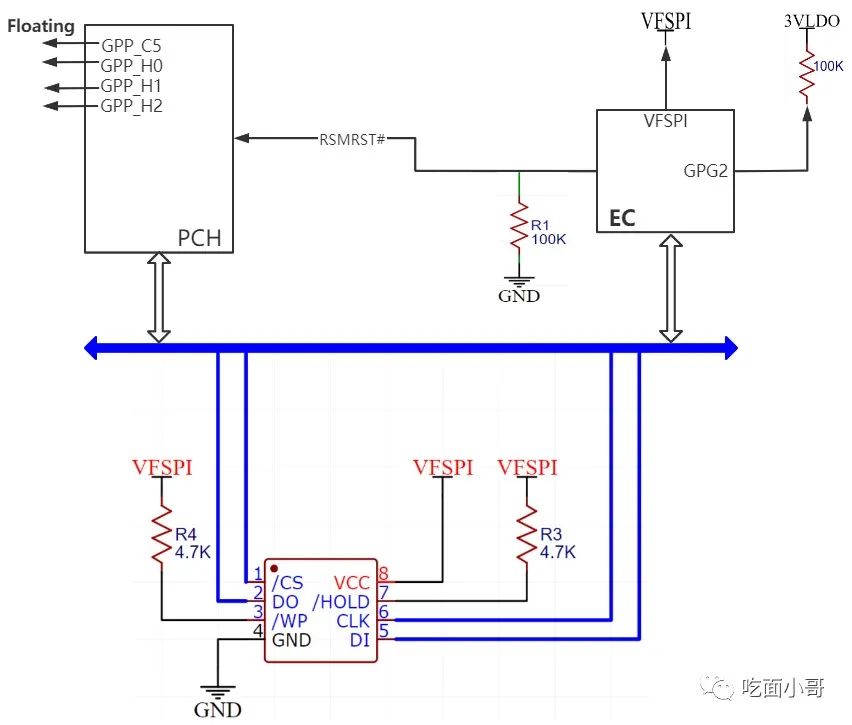

G3 Flash Sharing,如下圖。PCH 的 SPI 和 EC 的 SPI 接在一起,PCH 上電前或者 RSMRST# 拉高前,EC 直接從 SPI 接口讀取 EC Firmware。

No Flash Sharing,如下圖。PCH 的 SPI 和 EC 的 SPI 分別掛一個 Flash,互不干涉。

基于上述 G3 Flash Sharing 設計,通常硬件設計如下。

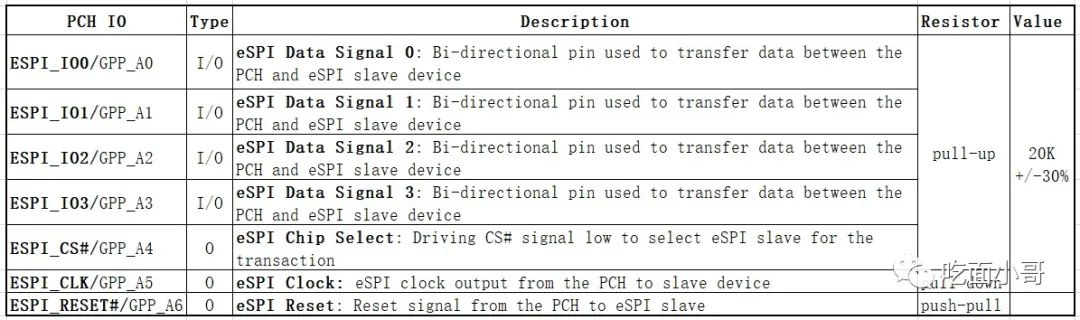

三,eSPI Pin List

PCH 和 EC 端的 eSPI 直接連線即可,上下拉在 chip 內部完成。

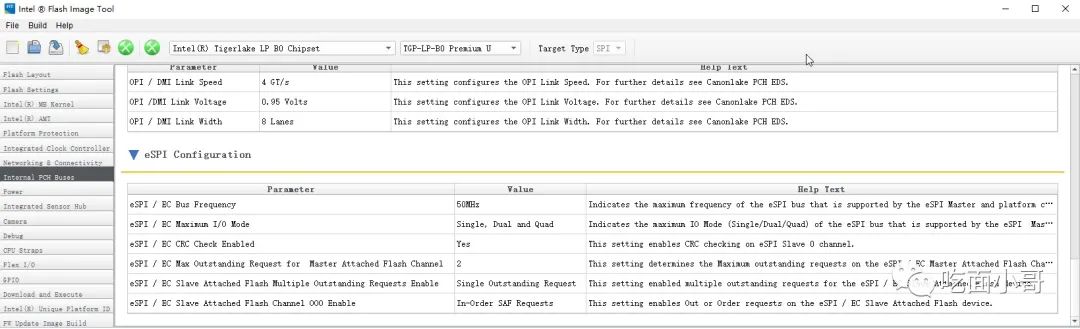

BIOS/ME 配置

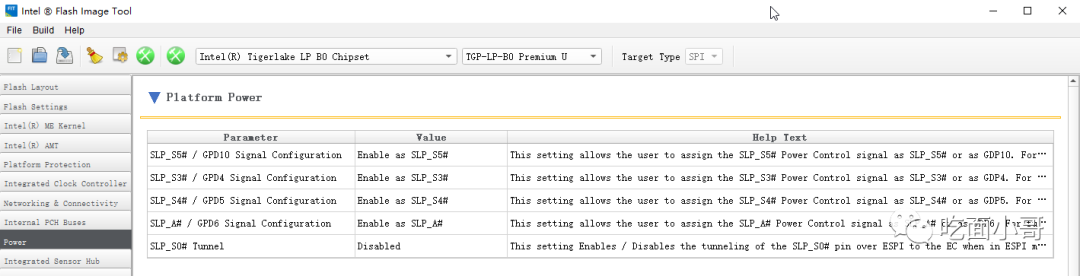

使用 FIT 配置 ME 參數,即設置 PCH 作為 eSPI Master 的工作參數,也稱之為 Soft-Strap。eSPI 通訊參數最終以和 EC 溝通結果為準。

關于 FIT 更詳細的配置,需要根據項目實際情況設定。

Boot 流程

eSPI 的 Boot 流程包括 Channel Config、Flash Access、Virtual Wire Communication。MAFS 和 SAFS 啟動過程略有差異,此處以 MAFS 啟動為例。

eSPI 通道配置

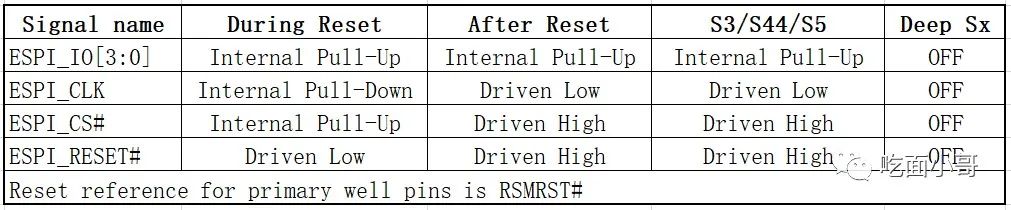

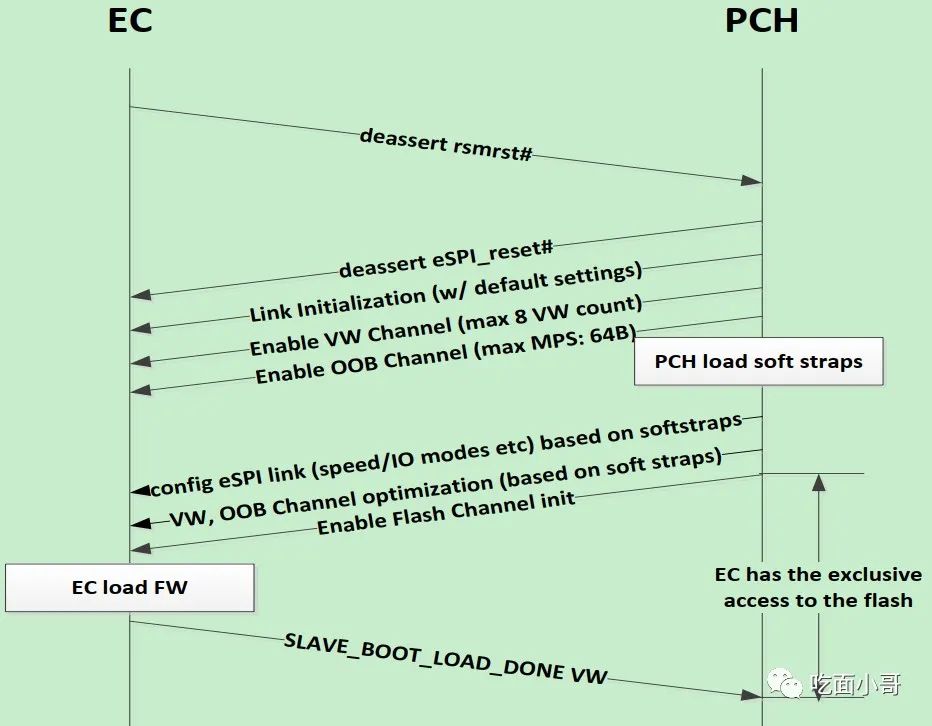

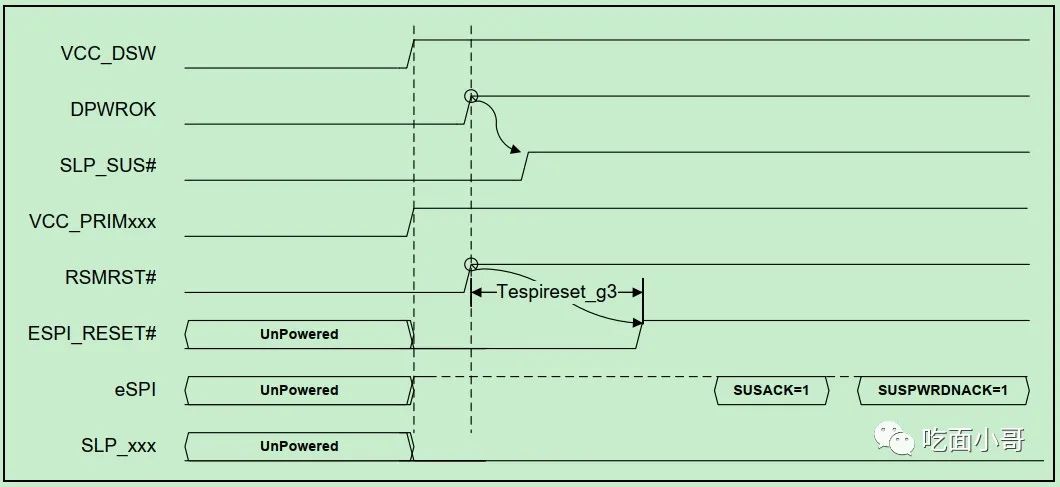

第一步,EC 拉高 RSMRST#(之前的時序按要求操作,同時 EC 端 的 eSPI Slave 需要復位完畢,準備待命)。然后 PCH 拉高 eSPI_Reset#。

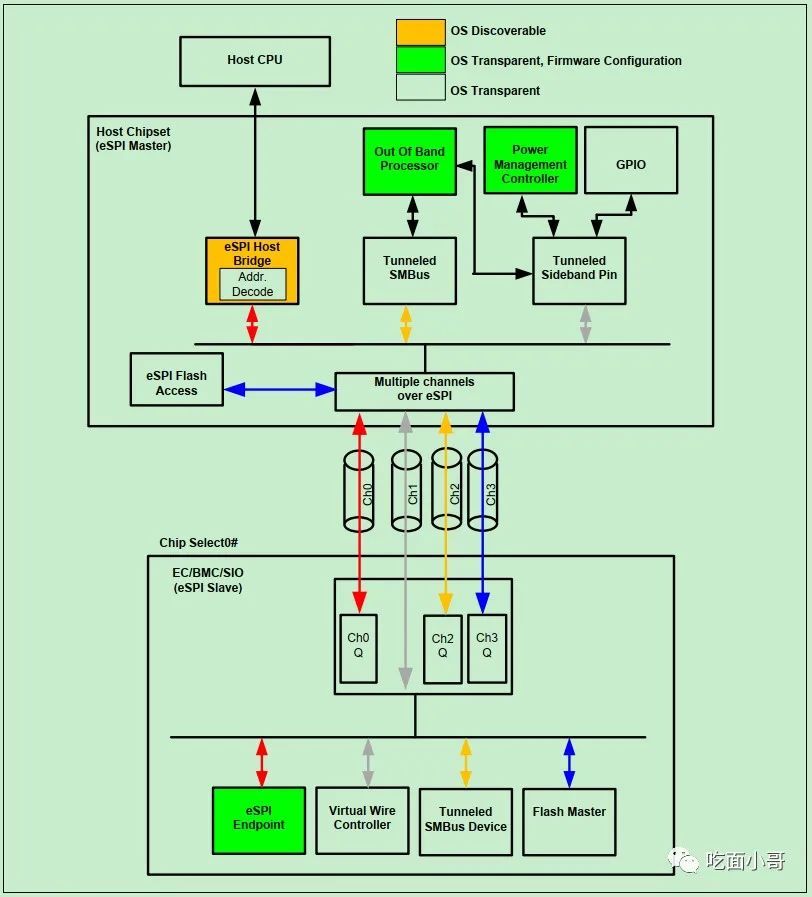

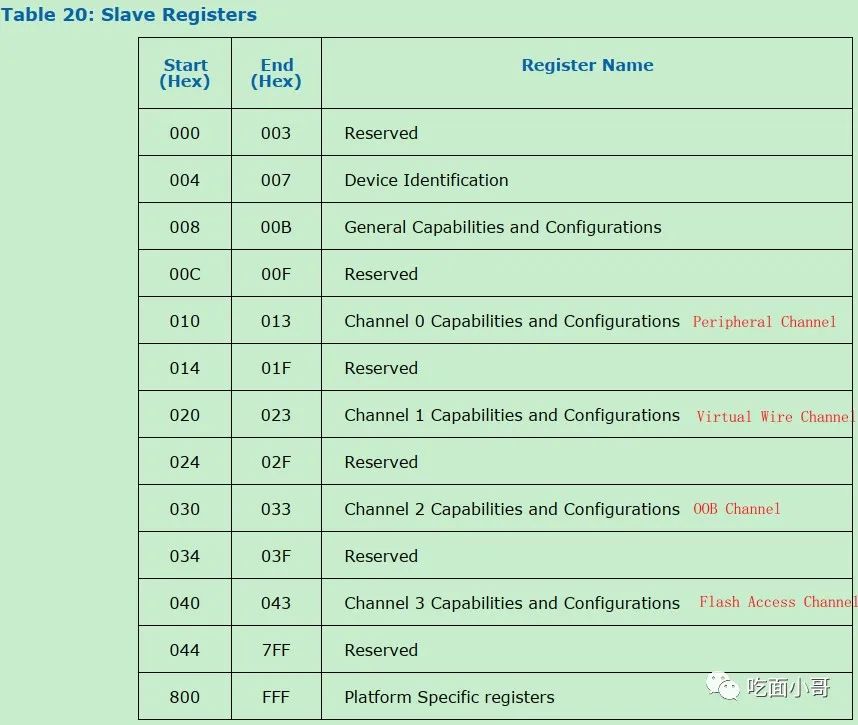

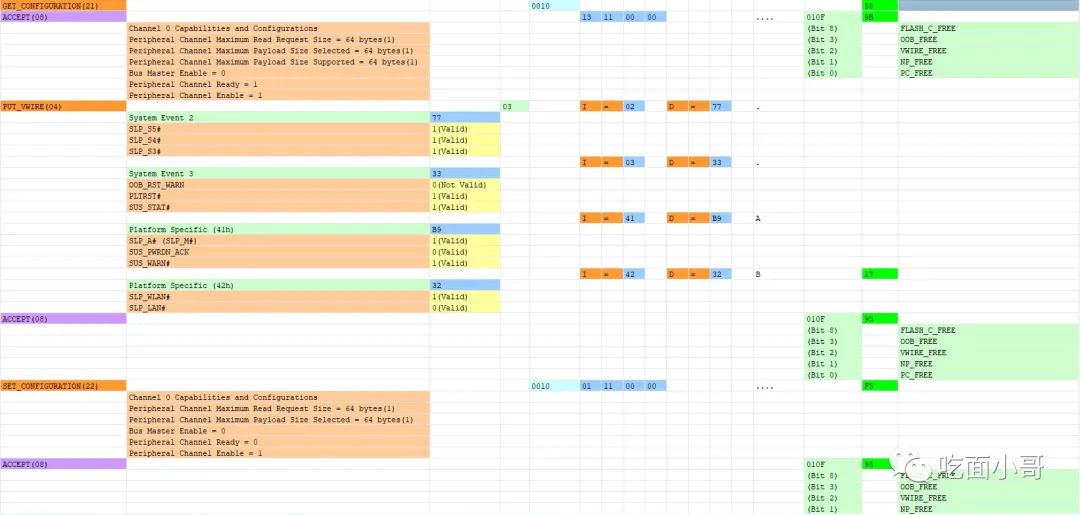

第二步,eSPI-Master 配置 Peripheral、Virtual Wire、OOB、Flash Access 四個 Channel。eSPI Master 端對 Channel 的配置,就是讀取 Slave Channel 配置寄存器。然后根據 Soft-Strap(ME配置)改寫 Slave 端配置寄存器,以配置實際需求的通道通訊參數。如下圖,Ch-0/1/2/3 分別是 Peripheral、Virtual Wire、OOB、Flash Access Channel。

PCH 作為 eSPI Master 配置 Channel,基本邏輯就是 eSPI Master 讀取 eSPI Slave寄存器,改寫寄存器,回讀確認。寄存器操作最小單位是 4Byte。使用到的指令是 GET_CONFIGURATION 和 SET_CONFIGURATION。

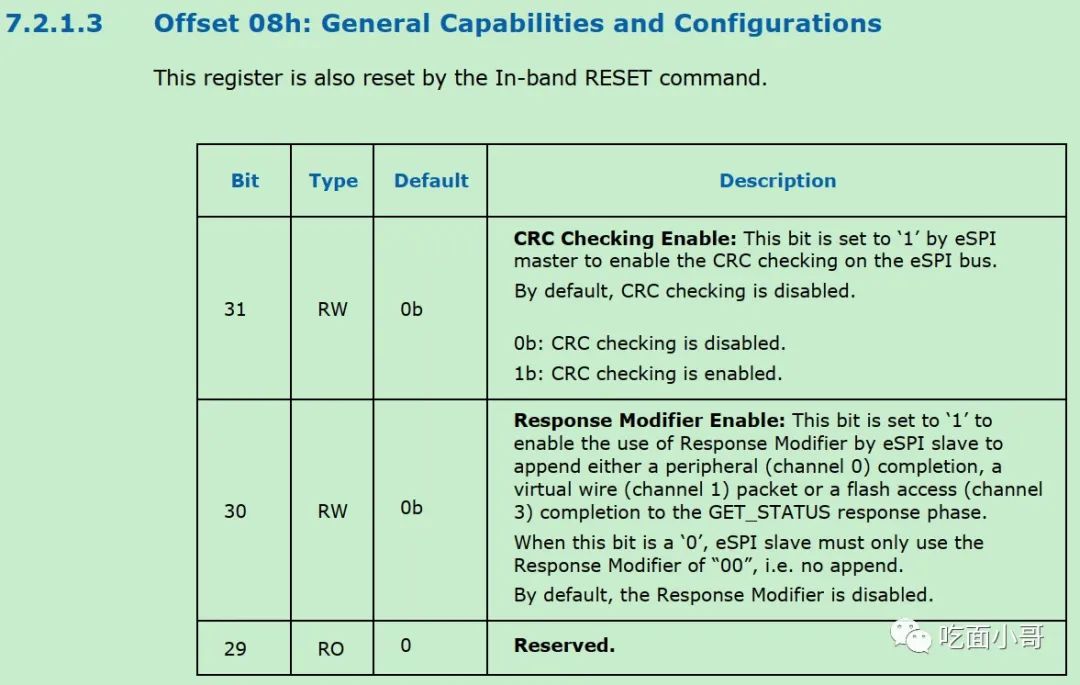

eSPI Slave 端需要配置的寄存器只有如下 5個,即 Offset 08、10、20、30、40,分別對應 4 個 Channel。

寄存器配置細節可以參考《Enhanced Serial PeripheralInterface (eSPI) V1.0》

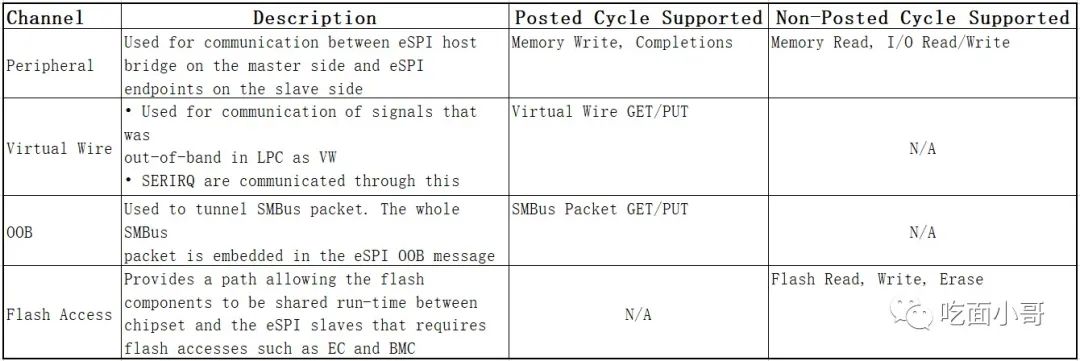

每個 Channel 的功能如下表

第三步,Slave Boot Done

配置完 Flash Access Channel,對于 MAFS 結構來說,EC 就可以通過 eSPI 訪問 PCH 下的 SPI Flash了。EC 應當根據實際需要通過 eSPI 訪問 PCH SPI Controller 下連接的 Flash,讀取 EC Firmware。

實際上,目前通用的設計是 Flash Sharing 的接線方式,EC 雖然不通過 eSPI 讀取 Firmware。但是依舊需要給 Host 發送一個 Virtual Wire Signal,即 SLAVE_BOOT_LOAD_DONE。

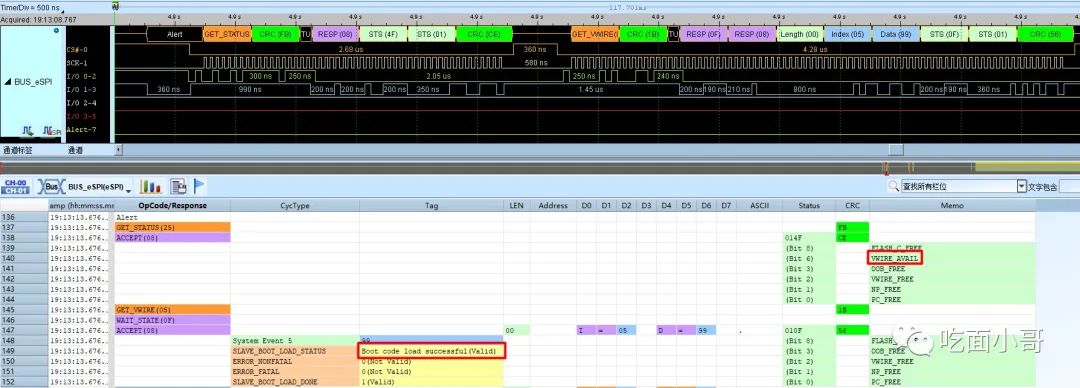

Slave 端發送 SLAVE_BOOT_LOAD_DONE 信號給 Host。由于是 Slave 主動給 Host 發送,因此在 CS# 高電平期間,Slave 拉低 I/O 1 產生一個 ALERT# 直到 Host 端拉低 CS# 為止。下圖 ALERT# 拉低時間就為 360ns。

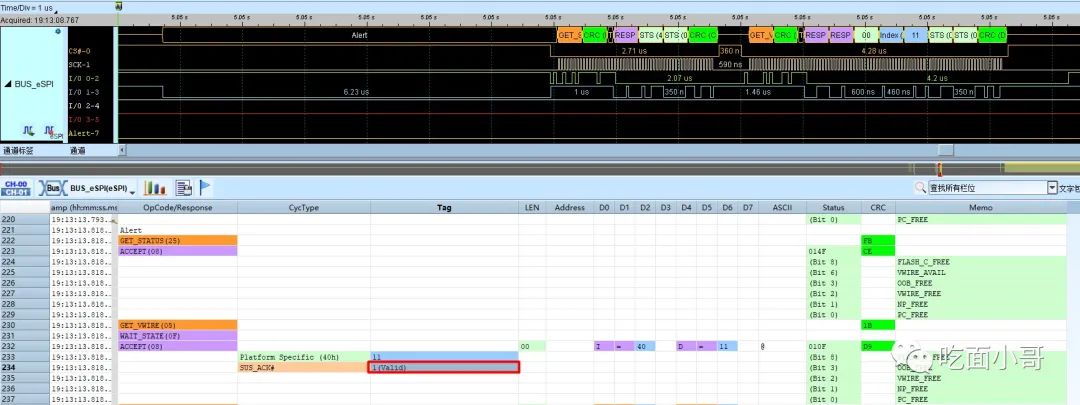

Host 緊接著發送 GET_STATUS 命令,查看 Slave 的 Event,Slave 置位 BIT-6,表明發生了 Virtual Wire 事件。

Host 發送 GET_VWIRE 獲取實際的 Virtual Wire 狀態。

Host 讀取 Virtual Wire 狀態。發現 SLAVE_BOOT_LOAD_DONE 置位,Host 即可進行下一步 Boot。

Virtual Wire 交互

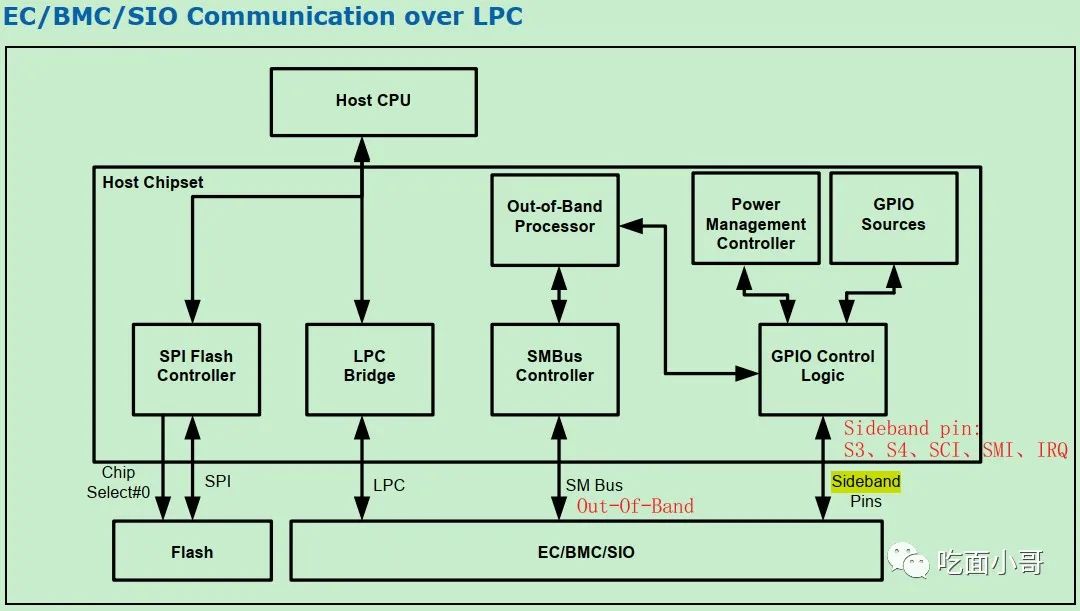

eSPI 設計的一個優勢就在于減少引腳資源,把 Sideband pin 轉換為 in-band Message。因此 PCH 輸入或者輸出的一些 pin 已經轉為 in-band Message。

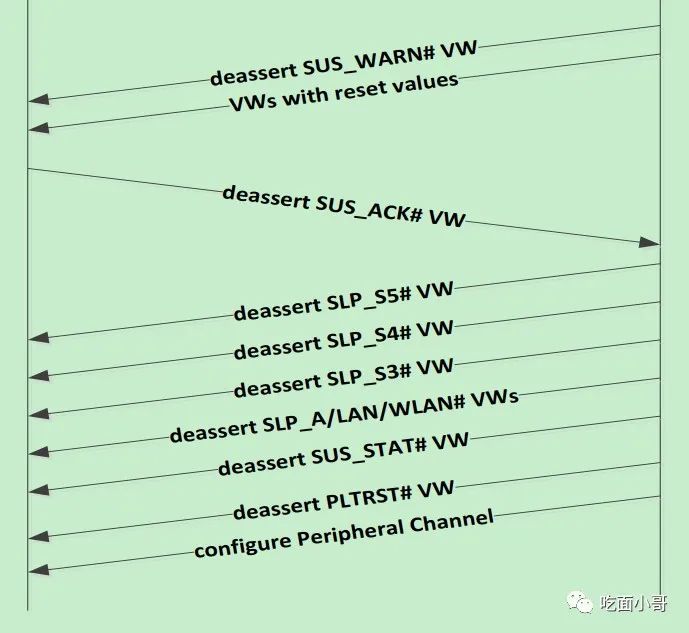

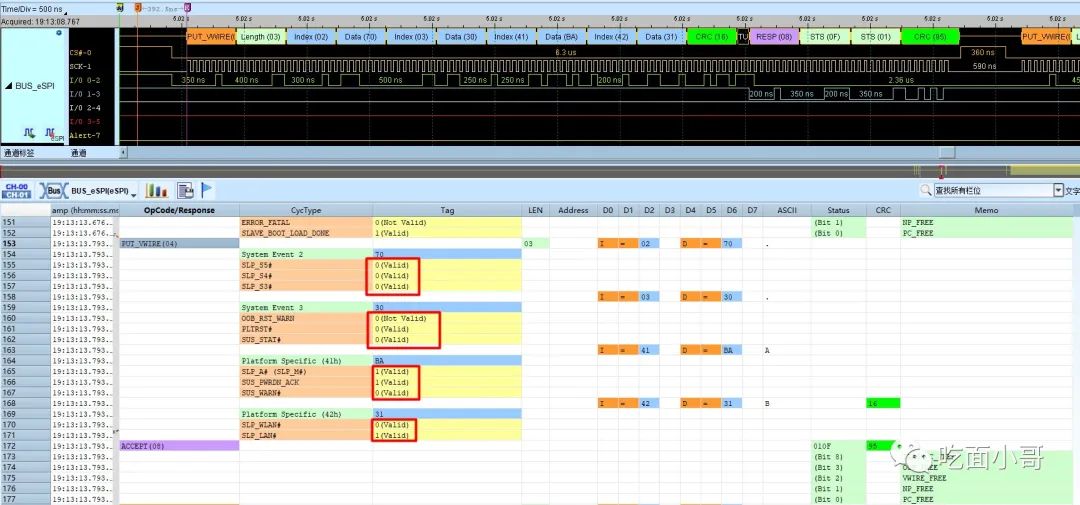

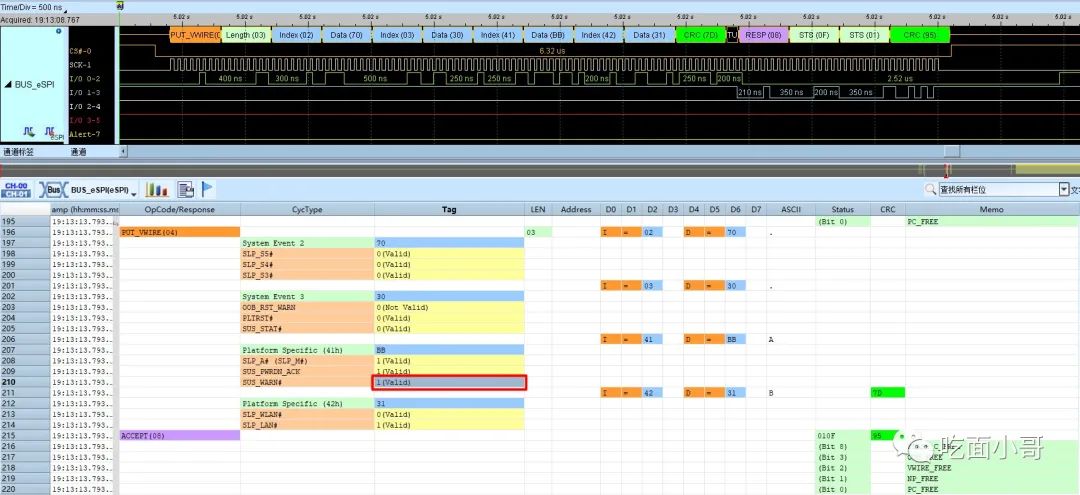

第四步,eSPI Master(PCH) 通過 PUT_VWIRE 指令把所有 VW 信號設置為復位值。

第五步,eSPI Master(PCH)發送 SUS_WARN# = 1 到 eSPI Slave。EC 回復 SUS_AC# =1 到 PCH

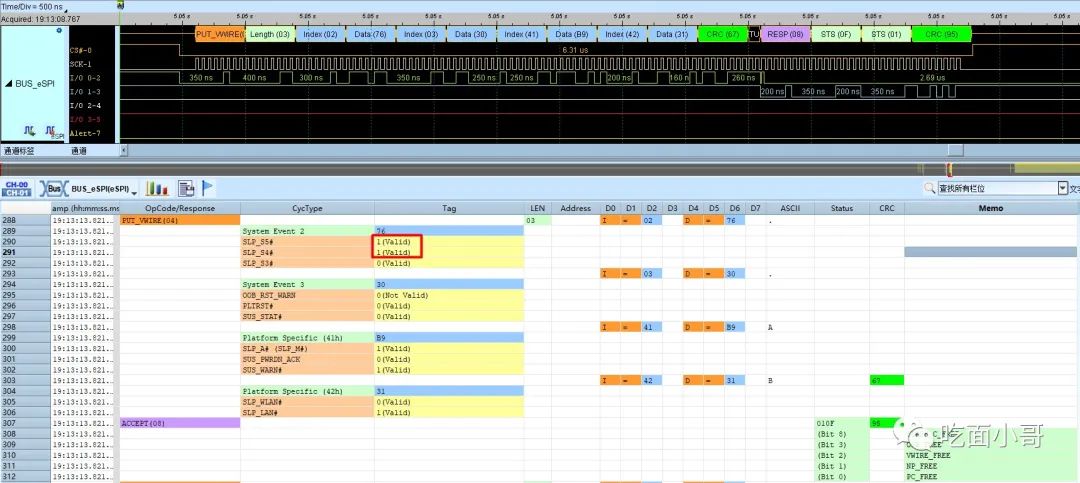

第六步,eSPI Master(PCH)挨個兒發送 SLP_S5 / 4 / 3,SLP_A / LAN / WLAN 高信號到 EC。下圖僅展示了 SLP_S4/5。

第七步,eSPI Master(PCH)發送 SUS_STAT# 和 RPLTRST# 信號到 EC。這將會使能 Peripheral Channel。

緊接著 eSPI Master 根據 Soft-Strap(ME)配置 Peripheral Channel。

至此,eSPI 啟動就已經完成,接下來就是 Memory、IO、OOB 通訊。

以上流程為個人理解,僅供參考。

-

cpu

+關注

關注

68文章

10902瀏覽量

212995 -

intel

+關注

關注

19文章

3483瀏覽量

186433 -

SPI

+關注

關注

17文章

1721瀏覽量

92108 -

總線

+關注

關注

10文章

2903瀏覽量

88384 -

硬件設計

+關注

關注

18文章

399瀏覽量

44663

發布評論請先 登錄

相關推薦

eSPI協議抓包分析

ESPI3 回收ESPI3 EMI測試接收機

tft_espi和nodemcu連接

主流的通訊總線LPC 和 eSPI介紹

eSPI接口通道功能解析

eSPI啟動流程詳解

eSPI啟動流程詳解

評論