硬件木馬

硬件木馬,硬件木馬會攻擊硬件本身,引起自身的安全問題

這里主要講述了 SoC 的設計制造流程中的硬件木馬(Hardware Trojan) 插入威脅、HT 特性、FPGA 中的 HT、HT 的分類、信任基準、硬件木馬的防御。

由于硬件木馬的硬件級別的植入,軟件級別的對應措施,可能不足以應對由硬件造成的威脅。

一、SoC 的設計制造流程中的硬件木馬(Hardware Trojan)插入威脅

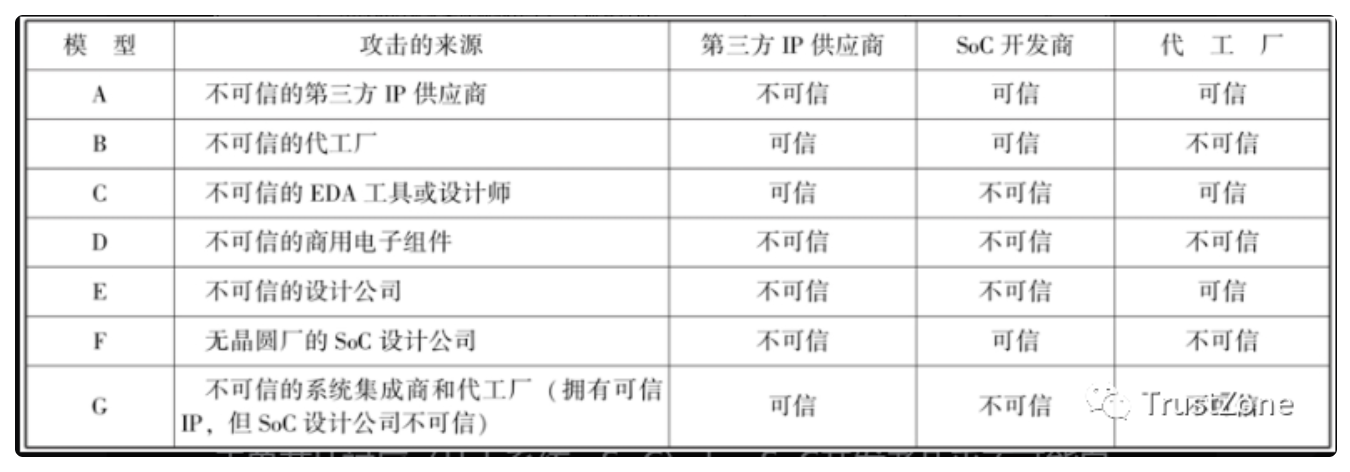

隨著尖端工藝的代工成本和現代片上系統(system-on-a-chip,SoC)平臺設計復雜性的不斷提高,曾經局限于一個國家甚至一家公司的IC供應鏈已經遍布全球。

在這種形式下,硬件電路設計中的第三方資源(主要指用于外包芯片制造和SoC開發的第三方知識產權,即intellectual property,簡稱IP核,包括軟核和硬核)在現代電路設計和制造中得到了廣泛的應用。

這類資源的利用雖然在很大程度上減少了設計工作量、降低了制造成本、 縮短了產品上市時間(time to marketing,TTM) ,但是對第三方資源及服務的高度依賴也引發了安全問題,打破了“攻擊者無法輕松訪問封閉的IC供應鏈”的幻想。

例如, 惡意代工廠可能會將硬件木馬程序插入所制造的芯片中 ,交付的IP核可能包含惡意邏輯和設計缺陷,這些缺陷在IP核集成到SoC平臺后會被攻擊者利用。

硬件安全的概念在硬件木馬出現后被正式引入。學術界和工業界開始采取措施緩解或防止相關威脅。硬件安全最初指的是硬件木馬的設計、分類、檢測和隔離。

硬件木馬威脅與不受信任的代工廠密切相關。 因此,研究者開發的硬件 木馬檢測方法往往側重于IC制造過程的流片后階段 ,強調增強現有檢測方法的安全性。

鑒于第三方IP核 可能是惡意邏輯插入的另一個攻擊向量 ,對綜合前設計的保護也變得同樣重要。據此,研究者還開發了流片前電路保護方法。

除了硬件木馬檢測,硬件安全的概念還從測試解決方案延伸到形式化驗證方法。 形式化驗證方法不僅在保證軟件程序安全時得到廣泛應用,還被證明在硬件代碼的安全驗證中頗為有效 ,因為硬件代碼通常是使用硬件描述語言(hardware description language,HDL)編寫的。

形式化驗證方法的發展不僅有助于為硬件設計提供高水平的安全保證,即便在 攻擊者可能有權訪問原始設計的情況下也是如此 ,也有助于克服黃金模型在許多硬件木馬檢測方法中的局限性。然而,在實現形式化驗證方法時,安全屬性的構建卻成為硬件安全研究者嘗試解決的一個開放性問題。

二、硬件木馬的特性

硬件木馬(Hardware Trojan)指對電路 設計的惡意的、故意的修改 ,在部 署電路時會導致惡意行為(例如通過I/O輸出密鑰、通過側信道功率輸出重要信息、增加系統延遲、減半加密輪數) 。

- 1、結構:基本結構有兩個: 觸發器和攻擊載荷 。當 觸發器監測到預期的事件 , 攻擊載荷就會執行惡意行為 。觸發條件可以是某內部節點上 的n位值 、重復發生 某事件 2^10^次 、到達某個溫度等,以增加反檢測能力。

- 2、硬件木馬示例:

- ①加密引擎中的木馬: 攻擊載荷可以是由攻擊者自定義的虛擬密鑰而不是用于敏感加密的實際加密密鑰 ,通過側信道泄露硬件密鑰。例如惡意片 外泄露技術(MOLES),通過功率側信道泄露硬件密鑰 。

- ②通用處理器中的木馬: 攻擊者在系統中植入后門,根據攻擊者的命令輸入禁用安全啟動機制 。并在硬件木馬的幫助下實現深層次攻擊,如利用緩沖區溢出攻擊繞過內存保護機制或通過認證繞過漏洞來訪問特定資產。

硬件安全研究的演進已經從硬件木馬的檢測轉移至可信硬件的開發, 即構建信任根 。雖然硬件設備的一些固有特性對電路性能有負面影響,但是可以將這些特性用于安全保護。

一個典型的例子是 物理不可克隆函數(physical unclonable function,PUF)的開發,借助電路制作過程中的工藝偏差,以“激勵—響應”對的格式生成特定芯片的指紋 。除金屬—氧化物半導體場效應晶體管(MOSFET)外,研究者正在研究新型的晶體管,如自旋轉移矩(spin transfer torque, STT)器件、憶阻器和自旋疇壁器件等,利用器件性能的特殊性來實現新型的硬件安全應用。

現有的硬件木馬設計可分為基于觸發機制和基于有害功能機制兩類。

硬件木馬的識別主要依賴于識別觸發機制和有害功能機制。

因此,硬件安全的研究者重點關注這兩種機制,以這兩種機制為突破口,探索和評估新的硬件木馬。

三、FPGA 中的硬件木馬

FPGA用途廣泛,從電信系統到導彈制導都有應用。但 FPGA的木馬可以通過IP核的形式載入通用FPGA結構中,并且有大量可被控制的可重構邏輯單元, 攻擊者從而利用FPGA通用系統進行攻擊。

存在IP依賴木馬和非IP依賴木馬。

IP依賴木馬是一種攻擊手段,其中攻擊者將惡意代碼嵌入到FPGA的IP(知識產權)模塊中。 這些IP模塊是FPGA設計中使用的現成模塊,它們被集成到設計中,并在運行時執行特定的任務。攻擊者可以利用這些IP模塊中的漏洞,將惡意代碼注入到FPGA中,從而控制整個系統。

非IP依賴木馬則是一種更高級的攻擊手段,它不需要依賴FPGA中的IP模塊。 這種類型的木馬利用了FPGA的物理層特性,例如電壓波動、時鐘偏差等,來制造錯誤,從而篡改系統行為。這種類型的木馬很難檢測和防御,因為它不依賴于特定的IP模塊或設計,而是利用了FPGA的通用特性。

四、硬件木馬的分類

分類的主要依據是硬件木馬的物理、激活、功能特性。

硬件木馬是指故意對電路設計進行惡意修改,導致電路在運行時產生意外行為。

受硬件木馬影響的IC可能會發生功能或規范被更改、泄露敏感信息、性能下降及系統不可靠等情況 。目前有些文獻已對硬件木馬提出了詳細的分類,涵蓋廣泛的具有潛在風險的硬件木馬。

比如: 根據插入階段、抽象級別、激活機制、效果和位置這五個不同的屬性將硬件木馬進行分類 。

- 硬件木馬與制造缺陷完全不同。制造缺陷具有無意、隨機的特點,數十年來已被廣泛研究,其行為可以通過Stuck-at故障、延遲故障等模型來反映。

- 但對于硬件木馬,研究者卻難以創建適合所有類型的模型。

- 此外,缺陷只在制造過程中產生,而硬件木馬可以在IC開發的任何階段插入。

因此,硬件木馬問題比制造缺陷的表現更為復雜。

五、信任基準

信任基準是一種用于檢測和評估電子系統安全性的方法。它涉及到在系統中故意引入一些錯誤或“木馬”,以觀察它們對系統性能和穩定性的影響。

這種方法可以幫助評估不同檢測技術的有效性,并確定最有效的防御策略。

- 1、基準命名約定:DesignName - Tn#$,e.g.,MC8051-T1010:木馬10號被插入MC8051的1號位置,版本為0

- 2、信任基準樣例:

- ①開發制造階段的基準樣例:EthernetMAC10GE-T710,由組合器觸發的木馬程序,查找特定的16位向量

- 基準命名約定:DesignName - Tn#$,e.g., MC8051-T1010:木馬10號被插入MC8051的1號位置,版本為0。這是一種標準的命名約定,用于標識在特定設計中的信任基準測試。

例如,MC8051-T1010表示在MC8051設計的第1號位置插入了木馬10號,版本為0。

- 信任基準樣例:信任基準測試可以用在不同的階段,例如開發制造階段。以下是一個樣例:EthernetMAC10GE-T710,這是一個由組合器觸發的木馬程序,它查找特定的16位向量。

這個樣例表明,在EthernetMAC10GE的設計中,已經插入了一個由組合器觸發的木馬程序,該程序會查找特定的16位向量。這種類型的木馬可能會對系統性能產生重大影響,尤其是如果它能夠成功地干擾系統的關鍵部分。

在硬件設計中, 信任基準測試是一種重要的安全評估方法 。它通過對系統進行故意攻擊來測試其防御能力,從而提供了一種度量防御策略有效性的方法。

同時,通過比較不同木馬的影響和各種木馬檢測技術的效果,設計師可以了解到哪種方法最有效,從而改進他們的設計。

為了防止信任基準測試帶來的潛在風險,設計師通常會在測試后對系統進行詳盡的檢查和驗證,以確保沒有留下任何可能影響系統性能或穩定性的隱患。同時,也會努力改進設計,以增強系統對未來攻擊的防御能力。

六、硬件木馬設計

對于設計良好的硬件木馬,傳統的功能測試方法很難檢測[7]。通常,硬件木馬包含兩個基本部分:木馬觸發器(實施木馬激活)和有害電路(實施有害功能)。

- 木馬觸發器是一個可選部件,用于監控電路中的各種信號或一系列事件。

- 有害電路通常從原始(無木馬)電路和木馬觸發器的輸出中獲取信號。

一旦木馬觸發器檢測到預先確定的事件或條件,就會激活有害電路執行惡意行為。通常情況下,木馬觸發器會在極為罕見的情況下被激活,因此有害電路大部分時間均保持非活動狀態。

當有害電路處于非活動狀態時,IC就像一個無木馬的電路,很難將木馬檢測出來。

根據木馬觸發機制的不同,硬件木馬可分為:組合木馬和時序木馬。一些木馬觸發機制采用組合和順序混合機制設計。圖展示了組合硬件木馬的抽象模型。惡意電路行為由同時發生的一組觸發條件激活。組合硬件木馬不使用觸發器或鎖存器來存儲狀態信息。

下圖展示了時序硬件木馬的抽象模型。木馬被一系列狀態轉換激活。

下圖給出了硬件木馬的觸發機制和有害功能機制。

現有的硬件木馬設計可分為基于觸發機制和基于有害功能機制兩類。

硬件木馬的識別主要依賴于識別觸發機制和有害功能機制。

因此,硬件安全的研究者重點關注這兩種機制,以這兩種機制為突破口,探索和評估新的硬件木馬。

七、硬件木馬的防御

1、木馬檢測

木馬檢測時最簡單、常用的方法,分為硅前、硅后兩階段。

- ①硅后檢測:

- 1、破壞性逆向工程:檢測能力強,可以檢測到任意惡意修改

- 2、功能測試:檢測能力弱,難以觸發木馬

- 3、側信道信號分析:測量硬件參數來檢測硬件木馬(如延遲、功率、溫度、輻射),將其與正常的(破壞性逆向工程得到的結果)進行對比

- ②硅前檢測:

- 1、代碼覆蓋率分析:即在設計階段的功能驗證期間執行代碼行的百分比。木馬可能逃脫

- 2、形式驗證:如符號執行、模型檢查、信息流,在驗證3PIP方面有效。

- 3、結構分析:用定向指標將低激活概率的信號或門電路標記為可疑。

主要是從兩個角度詳細展開:

芯片流片前的硬件木馬檢測

與軟件病毒、軟件木馬不同,硬件木馬無法通過固件更新輕易消除。 因此,硬件木馬對計算機系統的危害更大。硬件木馬由攻擊者設計。攻擊者往往采取在IC設計中添加不需要的功能的方法植入硬件木馬。

硬件木馬的設計沒有標準流程,所采取的方法 取決于攻擊者的目標及可用資源 。盡管如此,硬件安全研究者還是對不同的硬件木馬進行了分類。

基于硬件木馬的隱蔽性及其可能造成的影響,研究者還提出了多種硬件木馬設計方案。 雖然硬件木馬大多是在寄存器傳輸級(register transfer level,RTL)層面插入的,但有些是通過半導體摻雜操作插入的 。

這種在一開始就種下了不安全的種子

由于傳統的電路測試方法在檢測惡意邏輯方面存在不足,因此近年來研究者專門開發了硬件木馬檢測方法和可信集成電路設計。研究者已經提出了大量的硬件木馬檢測和防范方法。這些方法主要可以分為四大類:

- ①增強功能測試;

- ②側信道指紋識別;

- ③硬件木馬防范;

- ④電路強化。

①增強功能測試

由于增強功能測試方法是基于“硬件木馬通常由小概率事件觸發”這一思想的,因此,研究者提出以下兩種建議:

- ①將這些小概率事件包含在測試模式中,以便在測試階段觸發木馬程序[5];

- ②在門級網表中分析所有小概率事件,以識別可能充當觸發器的可疑節點[19]。

增強功能測試方法的局限性在于不存在對于小概率事件的標準定義 ,使得在標準測試模式和小概率事件模式之間留有巨大的缺口。同時也會給測試帶來工作量的提升。

②側信道指紋識別

側信道指紋識別是另一種流行的硬件木馬檢測方法。盡管在測試階段硬件木馬不易被觸發,可能會逃避功能測試,但插入的硬件木馬必然會改變被攻擊電路的參數[21,39,49]。

該方法的有效性取決于區分硬件木馬入侵電路和無硬件木馬電路的側信道信號的能力。

因此,利用先進的數據分析方法,通過消除不斷增加的工藝誤差和測量噪聲,可以幫助生成側信道指紋[14,48]。在指紋生成和硬件木馬檢測中,有些研究成果選擇使用多種側信道參數及其組合,包括全局功耗跟蹤[48]、局部功耗跟蹤[3,4]、路徑延遲[7,50]等。

基于側信道指紋識別的硬件木馬檢測方法因具有非侵入性而得到了廣泛的應用 ,由于是依據黃金模型可供比較的假設發展而來的,在很多情況下,黃金模型不容易獲取,所以不容易實現。

③硬件木馬防范

硬件木馬防范和電路強化技術方法試圖利用 附加邏輯修改電路結構,以消除小概率或可疑事件 ,或者使目標電路對惡意修改更加敏感。這類方法往往與其他硬件木馬檢測方法結合使用,可提高檢測精度或降低檢測成本。

即使在目標設計中使用了電路協同設計技術來降低附加邏輯的影響,附加保護邏輯仍然會影響電路的性能。此外,強化結構本身也可能成為硬件木馬攻擊的目標。

這不就是成了一個無限套娃的場景,比如說安全的架構TEE,讓更多地安全目的與服務進入到了安全側,安全側的代碼量于是極大的增加了,這樣安全側代碼被攻擊的面也就越來越廣了。

芯片流片后的硬件木馬檢測

盡管現有的檢測方法已能成功檢測到某些硬件木馬,但檢測范圍仍十分有限, 其原因在于依賴于過度簡化甚至有時是錯誤的假設 。這些假設往往包括以下方面:

- (1)硬件 木馬設計者使用傳統、簡單的電路結構,會使硬件木馬的功能受到限制 ;

- (2)硬件木馬設計者 試圖占用盡可能小的片上區域 ,在芯片側信道信息中難以發現硬件木馬產生的側信道信息;

- (3)被測電路存在黃金模型來檢測側信道信息的變化;

- (4)攻擊者只會攻擊數字電路,因為模擬和射頻電路對惡意篡改更為敏感。

這些假設很長時間內都被硬件安全研究者所接受,成為開發先進硬件木馬檢測和預防方法以及相關研究工作的主要指導原則。很可惜,這些假設并不完整,甚至帶有誤導性。筆者現在已經明顯意識到, 硬件安全和硬件木馬檢測的問題比之前設想的更加復雜、更加普遍 ,特別是:

- (1)類似于現代電路設計中的進步,硬件木馬可以利用先進的設計技術,在不犧牲功能的情況下增強隱蔽性;

- (2)增強的硬件木馬程序設計可以使用大量的芯片空間,相對于整個側信道信息仍保持隱藏狀態;

- (3)包含第三方資源的集成系統不一定都存在黃金模型;

- (4)模擬和射頻電路同樣容易受到硬件木馬攻擊。

上述情況推翻了許多先前提出的硬件木馬檢測和預防方法,導致無論在數字領域還是在模擬和射頻領域,集成系統都容易受到硬件木馬的攻擊。

因此,研究者開始研究芯片流片后的檢測方法,主要利用流片后側信道指紋識別和片上等效性檢查等技術。

這里的關鍵思想是在測試階段,隱藏的硬件木馬可能很容易避開檢測,如果被觸發,將會對側信道指紋識別或電路功能造成重大影響。

2、信任設計

- 檢測靜默的、低功率消耗的硬件木馬更有效的一種方式。

- ①促進測試:字面意思,如增加運行時監控模塊

- ②木馬植入防范:邏輯混淆、偽裝、功能性填充單元(將布局填滿)。通過重新排序邏輯門、加入額外的邏輯功能或者使用不同的設計方法來實現。

- ③可信計算:軟件級別的檢測,是基于不可信元件的可信計算,是最后一道防線。主要有TPM (受信任的平臺模塊)、安全啟動 (Secure Boot)、遠程驗證 (Remote Attestation)、封裝 (Sealing)組成。

- ④分割制造:字面意思,降低代工廠的不可信水平

3、小結

一般來說,硬件木馬防護對策分為三大類。每個大類還可進一步分為幾個子類。硬件木馬防護對策的分類如圖:

這一部分是最常用于芯片的設計中的,比如在最近的項目中,就做了很多防止側信道攻擊的設計,這里留著后面值得展開學習一下。

電子供應鏈

本章主要講述電子供應鏈上的安全隱患及應對措施。簡要羅列一下會在哪些點出現安全問題。

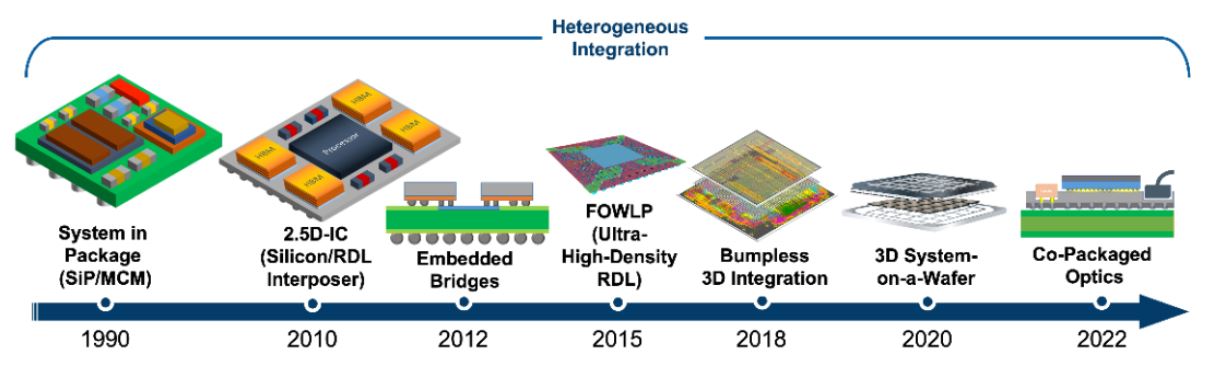

隨著集成電路的制造工藝發展至深亞微米級和納米級,集成電路設計和制造的復雜性急劇增加。

專用集成電路(application-specific integrated circuit, ASIC)或片上系統(SoC)組件通常需經過復雜的工藝過程。

該過程首先將規范轉換為行為描述,通常使用硬件設計語言(hardware design language,HDL),如Verilog或VHDL。

接下來,執行合成,根據網表(邏輯門)將行為描述轉換成設計實現。在完成設計實現后,數字GDSII文件被交給代工廠進行IC制造。

一旦代工廠生產出實際的IC,將通過測試過程確保其正確。

那些通過測試的IC通過組裝、重新測試后發送至市場,最終被部署到電子系統中。

先進的半導體制造技術在IC開發過程的每一個階段都需要投入大量的資金。

例如,2015年擁有一家代工廠的成本約為50億美元[2]。因此,大多數半導體公司無力維持從設計到包裝的全部IC供應鏈。

為了降低研發成本、縮短開發周期,半導體公司通常將部分工作外包給第三方代工廠,購買第三方IP核,使用第三方供應商的EDA(electronic design automation,電子設計自動化)工具。

顯然,第三方可能不可信或具有潛在惡意,第三方的加入增加了系統的安全風險。

有研究表明,IC供應鏈容易受各種攻擊,如硬件木馬、逆向工程、IP盜版、IC篡改、IC克隆、IC生產過剩等。其中,硬件木馬可以說是最大的威脅,引起了廣泛關注。

一、安全隱患

- 1、硬件木馬

- 2、CAD工具:CAD 工具只注意可能無意間引入漏洞,CAD 設計主要考慮傳統指標(如面積、產量、可測試性),而忽略了安全性。

- 3、測試/調試工具:無法避免其在電子元件上的使用,但其允許攻擊者觀察或控制其內部狀態

二、信任問題

- 1、IP濫用:即生產超過約定數量的元件

- 2、IP盜版:非法復制和修改

- 3、零件不合格:

- 4、集成電路 *** * 逆向工程:RE

- 5、文檔偽造:即數據造假

- 6、集成電路再標記、回收:放圖

三、對策

- 1、木馬檢測、安全檢查:

- 2、IP加密

- ①硬件鎖:硬 件鎖通常是一個外部USB設備,其內部包含了一個芯片,這個芯片具有獨特的識別碼 、加密功能和存儲能力。軟件開發者可以將授權信息、加密算法和關鍵數據存儲到硬件鎖中,然后將這些功能與其開發的軟件綁定在一起。軟件啟動時,會與連接的硬件鎖進行通信,驗證硬件鎖的身份。這通常包括向硬件鎖發送請求, 硬件鎖返回唯一的識別碼供軟件進行驗證 。只有在硬件鎖通過驗證后,軟件才會繼續運行。

- ②時間鎖: 類似硬件鎖,通常與硬件鎖結合使用 。

- ③追蹤/水印技術: 將特定的標識信息嵌入到IP中 ,以便在未經授權使用的情況下進行追蹤。提取水印后進行水印比對,例如 物理不可克隆函數(Physical Unclonable Function, PUF)利用微小的物理變異來生成唯一的標識信息。這些微小的變異是由制造過程中的隨機性和不均勻性引起的 ,使得每個硬件實例都具有獨特的特性。PUF可以用于實現設備的唯一標識、認證和密鑰生成。

-

處理器

+關注

關注

68文章

19409瀏覽量

231193 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26632 -

場效應晶體管

+關注

關注

6文章

365瀏覽量

19587 -

觸發器

+關注

關注

14文章

2003瀏覽量

61350 -

SoC系統

+關注

關注

0文章

52瀏覽量

10727

發布評論請先 登錄

相關推薦

SOC設計領域的核心技術-軟/硬件協同設計

SoC設計中遇到的難題急需解決

soc芯片的相關資料推薦

用SystemC進行SoC的系統級設計與仿真

利用FPGA軟硬件協同系統驗證SoC系統的過程和方法

【Soc級系統防御】Soc硬件木馬與電子鏈學習

【Soc級系統防御】Soc硬件木馬與電子鏈學習

評論