1. Integrity 3D-IC 早期三維布圖綜合

? 早期布圖綜合(Early Floorplan Synthesis,EFS)

? 三維布圖綜合

? 線網長度與芯片間互連信號數目的折中

? 異構芯片的堆疊

早期布圖綜合(Early Floorplan Synthesis,EFS)

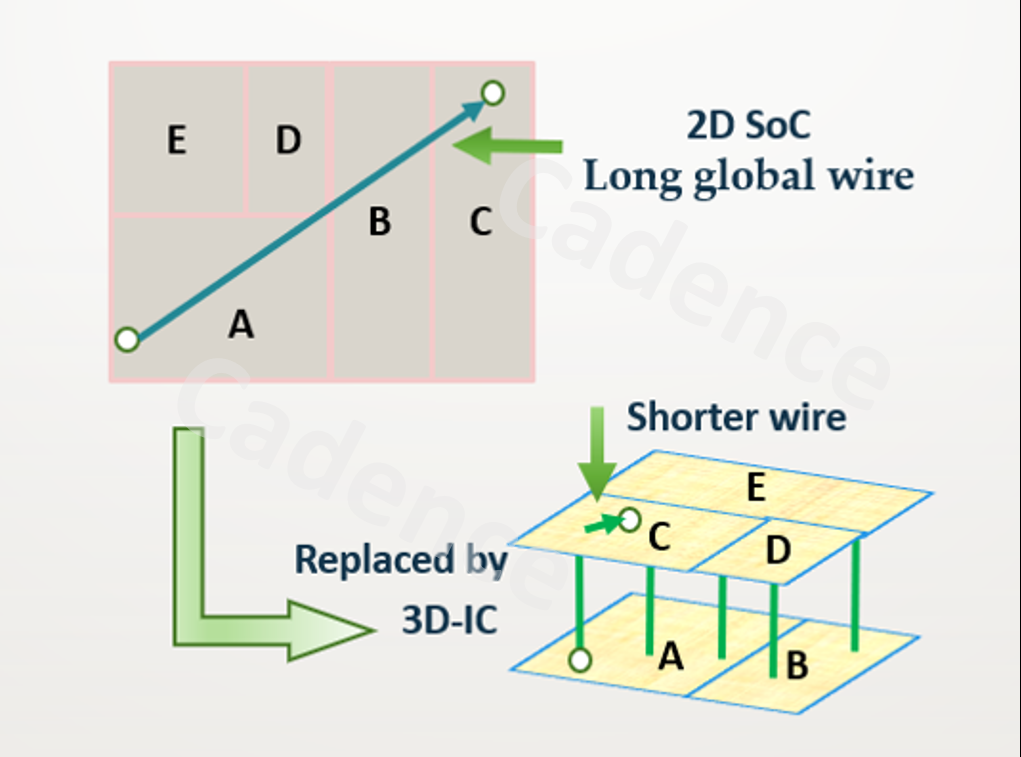

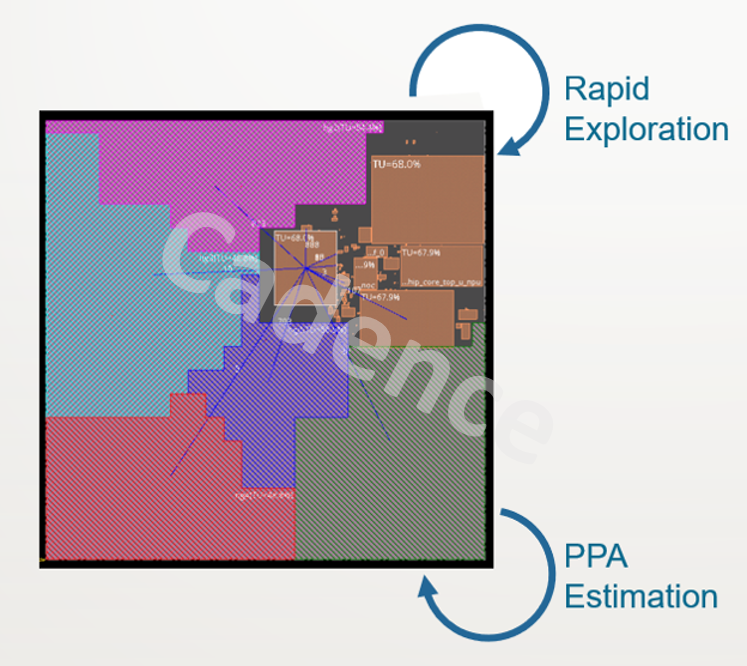

對于大規模的芯片設計,各個模塊的布局布線會在 RTL 開始了一段時間之后進行,而芯片頂層的設計規劃需要在網表成熟之前就開始,這個階段的頂層規劃往往很難創建,尤其是這個時候各個模塊還在不斷地優化。所以我們提供了早期布圖綜合這樣一個功能,去自動且快速地進行模塊布局,幫助用戶在有完整網表、部分網表、甚至還沒有網表的時候,對布局進行一系列的探索。

使用 EFS,工具可以做時序驅動的模塊布局,優化模塊的形狀,在滿足模塊的利用率的前提下,盡量壓縮減小芯片面積。同時 EFS 也支持其他約束,包括模塊的寬長比、利用率、是否允許直通(feedthrough),以及布線通道的寬度等。

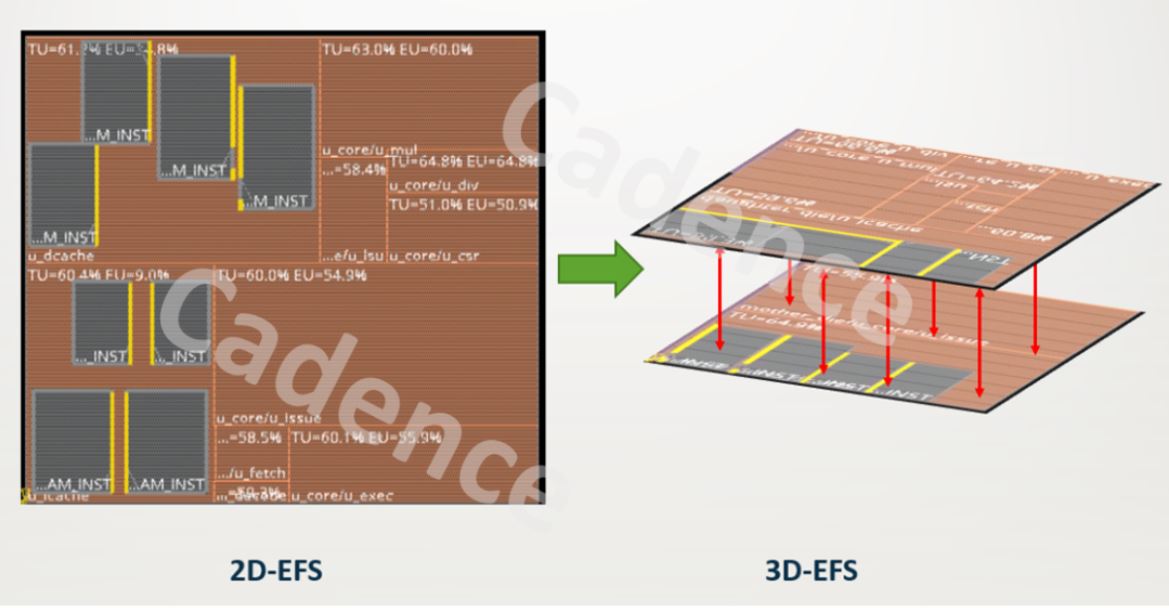

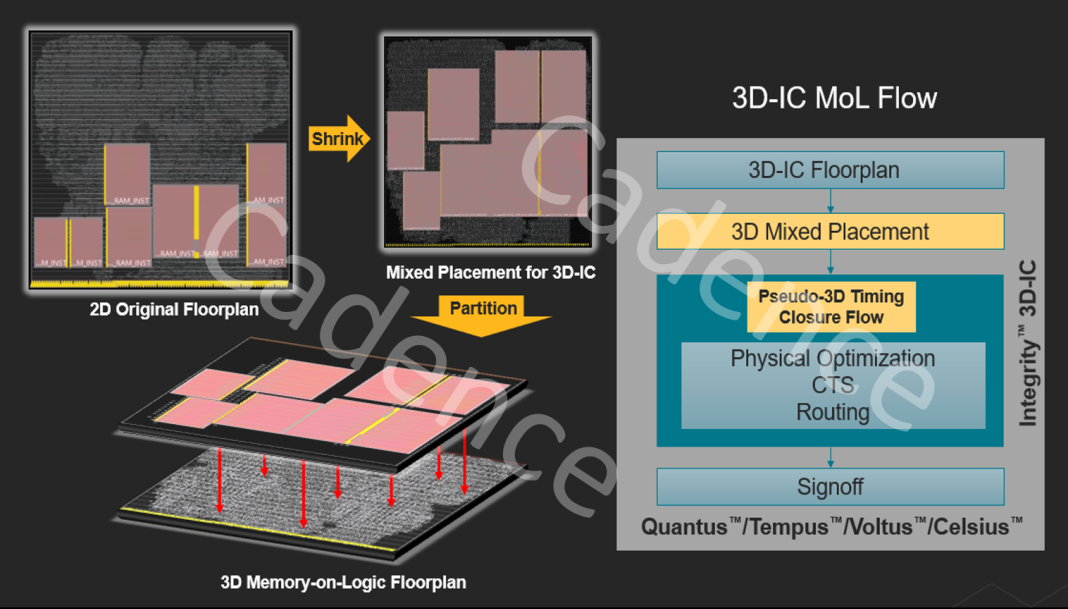

三維布圖綜合

芯片層數的增加擴大了解空間,使得三維集成電路布圖規劃更加困難。

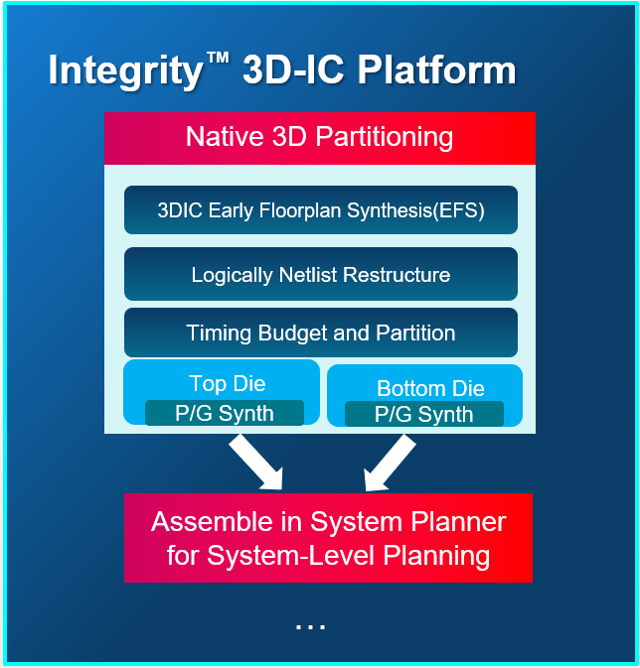

基于 EFS,Integrity 3D-IC 進一步增強并推出了三維布圖綜合功能,在三維空間內對模塊進行自動布局,并且進行各模塊的形狀調整,從而優化芯片面積,線網長度和層間過孔數據。另外,Integrity 3D-IC 還支持用戶預分配模塊到某層芯片或者預擺放到某個位置。

線網長度與芯片間互連信號數目的折中

減小系統線網長度會不可避免地增加芯片間的互連信號數目。而由于 Bump / TSV 間距以及面積的限制,在做三維布圖綜合時需要控制芯片之間互連信號的數目。Integrity 3D-IC 可以很好地權衡二者,通過參數調整,幫助用戶快速地預覽結果并進行三維布局以及分割的探索。

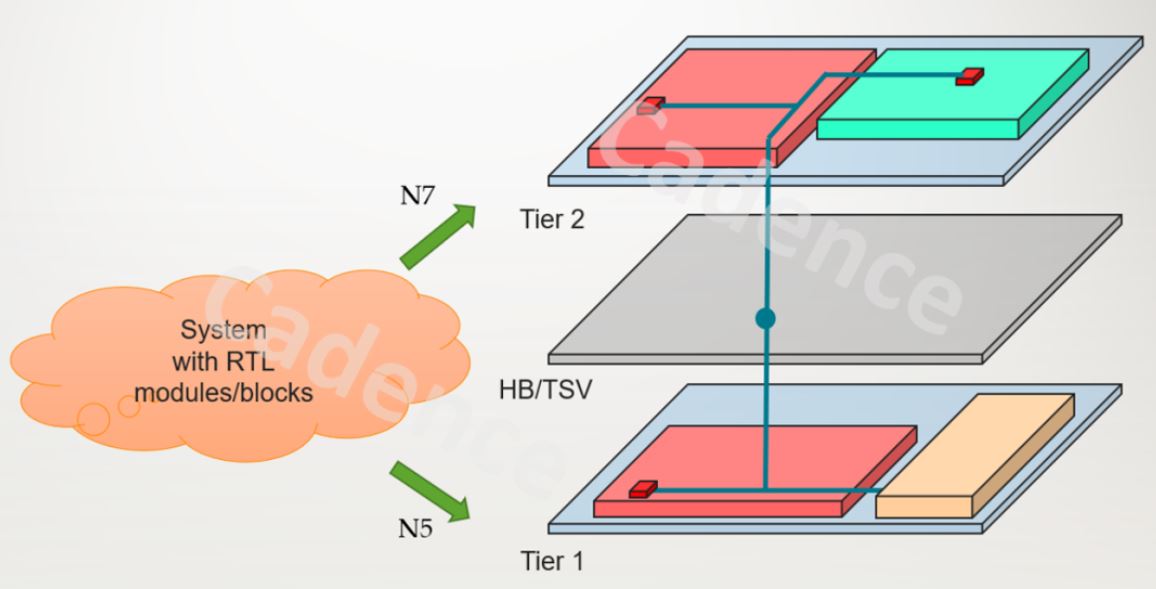

異構芯片的堆疊

把不同制程的邏輯芯片堆疊在一起,既可以滿足性能需求,也能有更好的良率及更低的制造成本。Integrity 3D-IC 同樣支持異構三維集成電路的布圖綜合,給不同的模塊分配合適的工藝制程。

2. 層次化設計方法

? 層次化結構重建

? 基于邏輯深度的時序預算

層次化結構重建

基于三維空間模塊布局的結果,Integrity 3D-IC 會將原來二維的網表進行層次化結構的重建,在系統頂層產生 Top Die 和 Bottom Die 兩個層次化結構,把各個模塊分配給上層芯片和下層芯片,得到新的三維集成電路的網表。在此過程中,Integrity 3D-IC 可以自動創建上層芯片與封裝 PKG 相連所需要的 Feed Through,并且更新系列相關的時序約束信息、翻轉計數格式文件等。

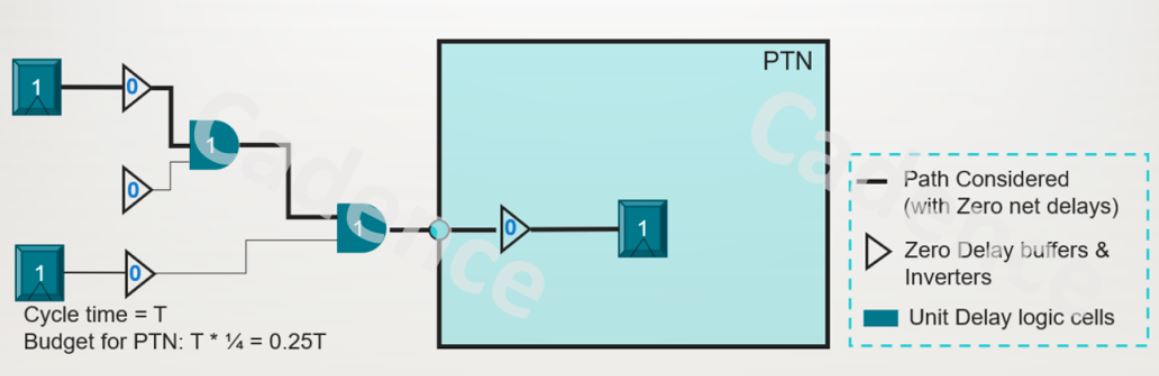

基于邏輯深度的時序預算

在層次化設計流程中,系統的時序約束需要正確地映射到相對應的各層芯片中。在早期,可以通過基于時鐘周期的方法做快速的時序預算,給上下層芯片按指定比例分配合適的時序約束文件。為了得到更加準確的時序預算,可以在 Integrity 3D-IC 使用基于邏輯深度的時序預算。基于邏輯深度的時序預算會根據最長的邏輯路徑給芯片做好時序的裕量的分配,并且允許用戶靈活地對邏輯路徑上的組合邏輯單元、時序邏輯單元等設置權重,另外扇出也會被考慮在內。

從設計初始就充分考慮三維實現的自由度能提供最佳系統性能。Integrity 3D-IC 助力架構和布圖規劃設計師從全局考慮不同模塊在三維空間多層級上的邏輯物理分布。通過 Cadence 強大的的層次化早期布圖規劃算法實現不同單元、模塊、IP 在不同層次晶粒的最優分配,將 3D-IC 優勢發揮到極致。

- 審核編輯 黃宇

-

集成電路

+關注

關注

5392文章

11624瀏覽量

363199 -

IC

+關注

關注

36文章

5983瀏覽量

176226 -

3D

+關注

關注

9文章

2912瀏覽量

108009 -

芯片設計

+關注

關注

15文章

1028瀏覽量

55010

發布評論請先 登錄

相關推薦

3D-IC設計之系統級版圖原理圖一致性檢查

SMARTSCAN三維掃描儀電子產品配件三維掃描服務

三維可視化的應用和優勢

Cadence 憑借突破性的 Integrity 3D-IC 平臺加速系統創新

3D園區可視化建模三維有哪些類型,都有哪些功能

3D智慧城市三維可視化的特點

智慧園區可視化三維大屏展示綜合管理平臺的價值

工業工廠3D沉浸式三維數字化管理系統

Integrity 3D-IC早期三維布圖綜合功能

3D-IC未來已來

產品資訊 | 3D-IC 設計之自底向上實現流程與高效數據管理

3D-IC 設計之早期三維布圖綜合以及層次化設計方法

3D-IC 設計之早期三維布圖綜合以及層次化設計方法

評論