今天想來聊一下芯片設計中的一個重要macro——PLL,全稱Phase lock loop,鎖相環。我主要就介紹一下它是什么以及它是如何工作的。

芯片的時鐘可以自己產生,可以由幾個反相器接在一起構成一個簡單的振蕩器產生時鐘,它的頻率可以到很快的速度,但是時鐘周期卻沒那么固定,一會快一會慢的。

而從芯片外面來的晶振一般具有穩定的時鐘周期,但頻率只能是在兆赫茲的量級。PLL就是利用外部晶振作為參考時鐘,來輸出一個周期穩定的高頻率的時鐘,這個時鐘供芯片的時序電路使用。

可以說PLL是整個芯片的源頭,從PLL出來的時鐘我們認為就是干凈的、后端可以直接用的時鐘了。

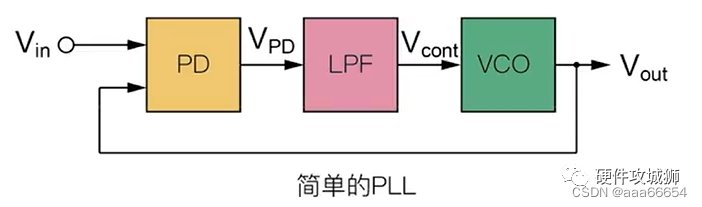

最基本的PLL構成如下:它有一個最主要的元件——壓控振蕩器VCO,VCO的振蕩頻率是隨著輸入電壓變化的,它的輸出就是整個PLL的輸出,也就是我們最終拿到的時鐘。

而VCO的輸出也會由一個反饋電路接回PLL,經過除頻電路得到一個與外部晶振頻率差不多的時鐘信號,而后比較他們二者的相位。

如果晶振相位稍快,就把VCO輸入電壓調低,如果晶振相位稍慢,就把VCO輸入電壓調高,這樣就可以根據輸入晶振反饋調整VCO的輸出,從而得到穩定的高頻時鐘信號。

這只是PLL基本思想,實際實現起來,需要有一個電荷泵調整VCO的輸入,而VCO的輸入也需要濾掉諧波,如果不過濾的話反映到最終時鐘上就是時鐘抖動了。

從上面的簡單介紹就可以看出,PLL是一個模擬器件,所以他本質上對噪聲和干擾特別敏感,現在做PLL的重要課題之一就是如何減弱噪聲影響。

一般后端在物理實現的時候,也會對PLL做額外的特殊照顧,盡量減弱干擾。PLL就類似芯片中的心臟,用以供給跳動的時鐘。

但是在數字電路中照顧模擬器件的噪聲干擾是十分復雜、困難的一件事,需要考慮很多東西。首先在PLL內部,就需要采用類似差分電路的方法來做VCO,當然這是最基本的,但是更多方法我也不太了解。

在PLL外面,我們也會加很大的blockage,還有加很強壯的shielding等,PG供電也是怎么強怎么來,還有等等一系列額外的QoR檢查、ESD檢查等。總之一句話,就是會犧牲很大的代價也要把PLL的抗噪聲做好。

-

鎖相環

+關注

關注

35文章

590瀏覽量

87895 -

芯片設計

+關注

關注

15文章

1028瀏覽量

55006 -

VCO

+關注

關注

13文章

190瀏覽量

69346 -

壓控振蕩器

+關注

關注

10文章

134瀏覽量

29369 -

PLL電路

+關注

關注

0文章

92瀏覽量

6475

發布評論請先 登錄

相關推薦

鎖相環是什么意思

可編程晶振的鎖相環原理

鎖相環PLL的噪聲分析與優化 鎖相環PLL與相位噪聲的關系

鎖相環PLL的常見故障及解決方案

鎖相環PLL在無線電中的應用 鎖相環PLL與模擬電路的結合

鎖相環PLL與頻率合成器的區別

鎖相環PLL的工作原理 鎖相環PLL應用領域

將 Hercules 鎖相環(PLL)咨詢SSWFO21#45的影響降至最低

簡述鎖相環的基本結構

鎖相環PLL是什么?它是如何工作的?

鎖相環PLL是什么?它是如何工作的?

評論