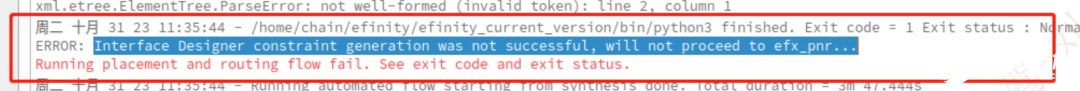

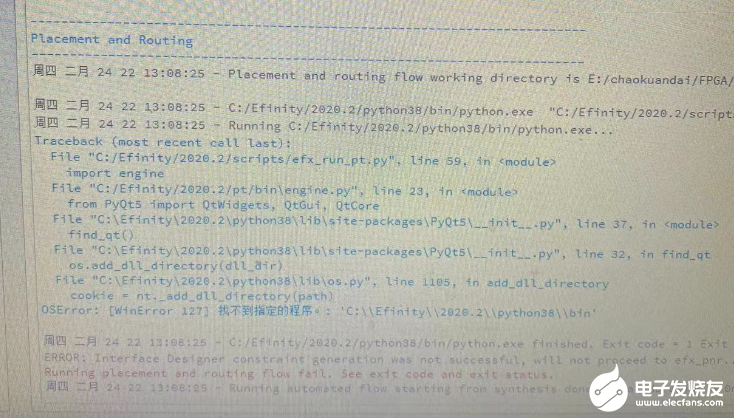

(1)ERROR:Interface Designer constraint generation was not successfull,will not proceed to efx_pnr...

原因:(1)有些客戶使用Win7版本,目前Efinity對Win7的支持不好。建議升級成win10。

(2)殺毒軟件刪除了文件,實際interface生成約束是沒有問題的,客戶pnr的時候就報錯,需要重新安裝軟件。

(3)電腦存在加密系統(tǒng) 。造成的現(xiàn)象是新建工程時interface可以打開,但是生成xxx.peri.xml文件之后再次打開就會報錯。

(2)Interface打不開。

現(xiàn)象:(1)打開interface的時候指示: Efinity Interface Designer finished. Exit code = 1 Exit status : Normal Interface design file exists, check and migrate done (2)新建工程第一次可以打開interface Designer (3)刪除xxx.peri.xml之后,第一次也可以打開Interface Designer. 原因:電腦存在加密 (3) interface打不開 打開interface Designer時會報以下錯誤。 EfinityIPCatalogfinished.Exit code = 0Exit status:Normal

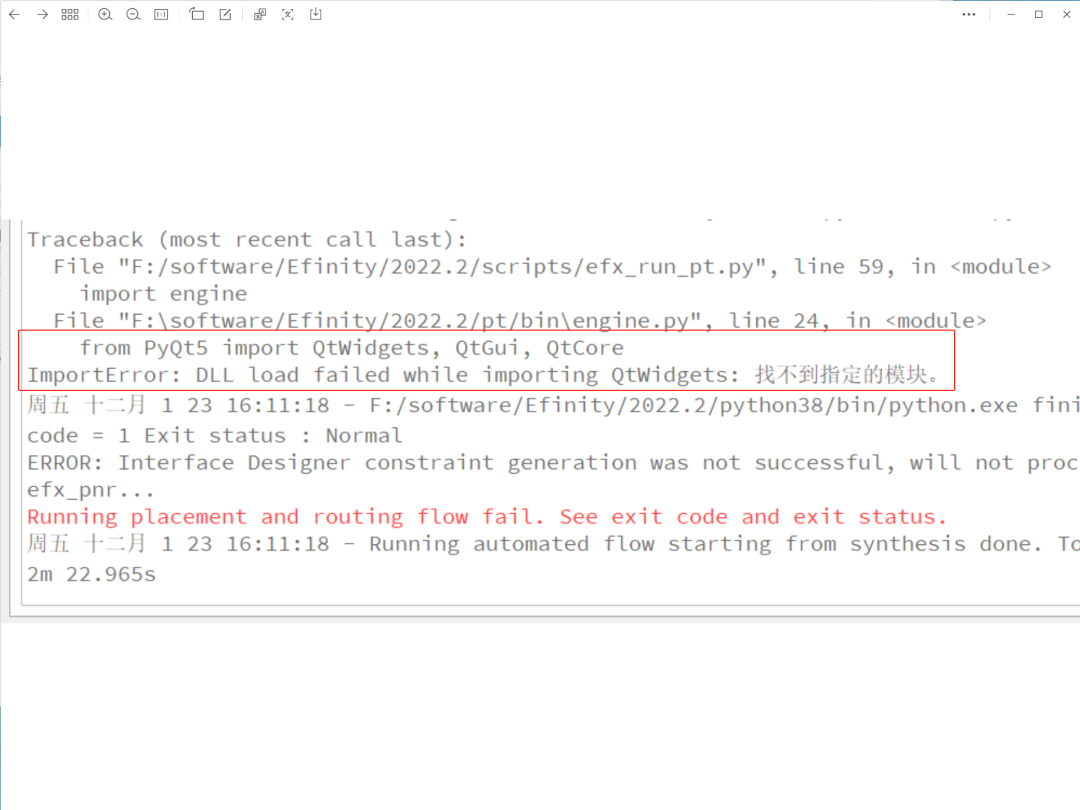

編譯過程可能報以下錯誤:

ERROR: Interface Designer constraint generation was not successful, will not processpnr..

解決方案:安裝VC_redist.x64.exe,注意參考軟件安裝指導的版本。

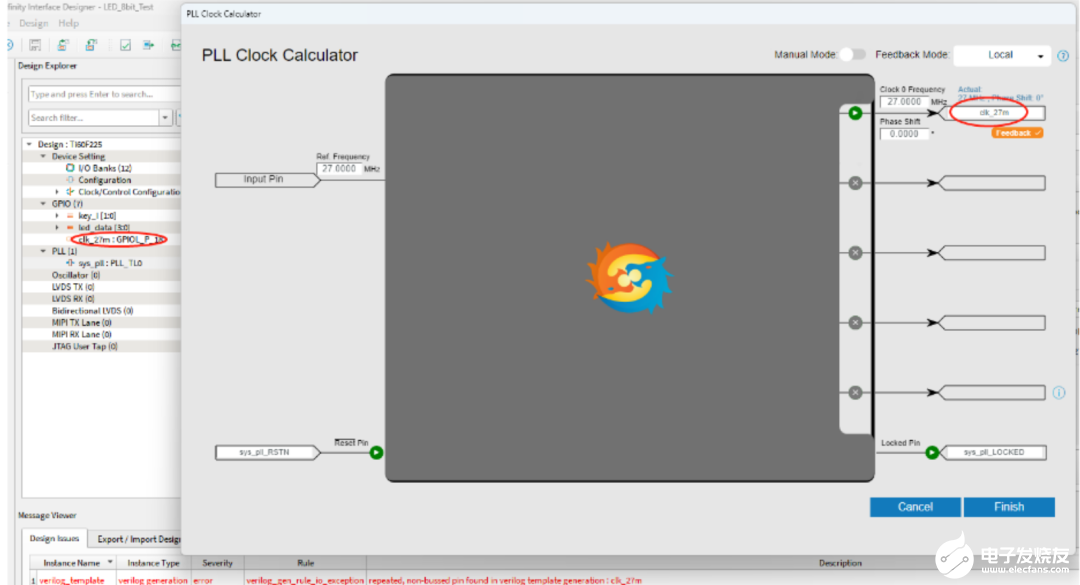

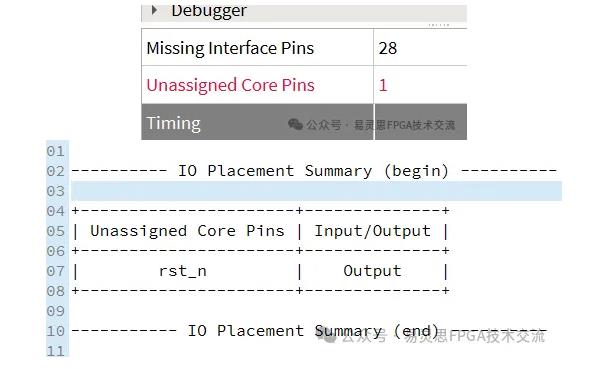

(4)repeated,non-bussed pin found in verilog template generation:clk_27m

說明:在GPIO處定義了一個clk_27m,在pll的輸出上又定義了一個clk_27m,兩個信號名沖突。

(5)ERROR: Interface Designer constraint generation was not successful, will not processpnr..

原因:1)一般是軟件有360或者別的殺毒軟件的相關(guān)文件刪除了,需要找回文件或者重新安裝軟件。

2)客戶使用Win7版本,目前Efinity對Win7的支持不好。建議升級成win10。

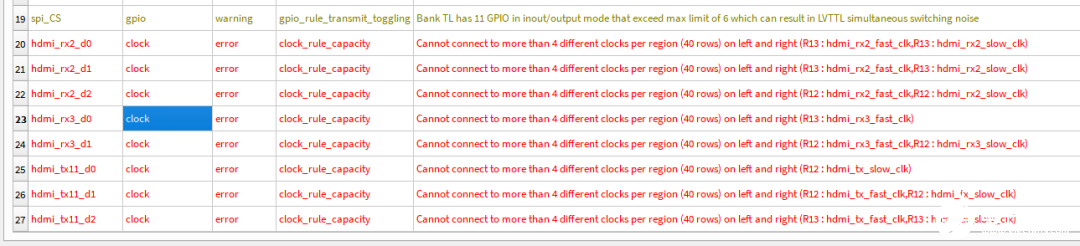

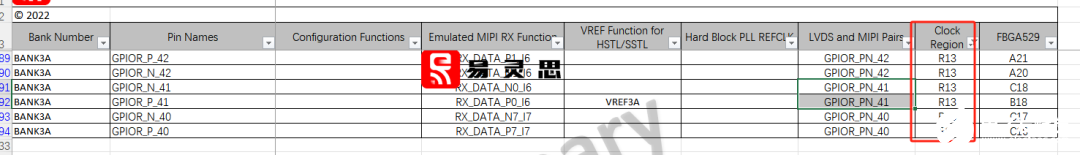

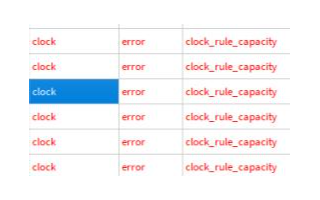

(6)cannot connect to more than 4 different clocks per region on left and right

原因是在pinout文件中對應的Clock Region中,不能超過4個時鐘去驅(qū)動。

也就是GPIOR_PN_42,41,40三組差分對,不能由兩組LVDS來驅(qū)動,因為每組LVDS時鐘有l(wèi)vds_fast_clk和lvds_slow_clk兩個,兩組就會有4個時鐘在Region clock R13區(qū)域。

結(jié)論就是把LVDS差分對放在同一個Clock Region.

審核編輯 黃宇

-

Designer

+關(guān)注

關(guān)注

0文章

122瀏覽量

35864 -

Interface

+關(guān)注

關(guān)注

0文章

103瀏覽量

38645

發(fā)布評論請先 登錄

相關(guān)推薦

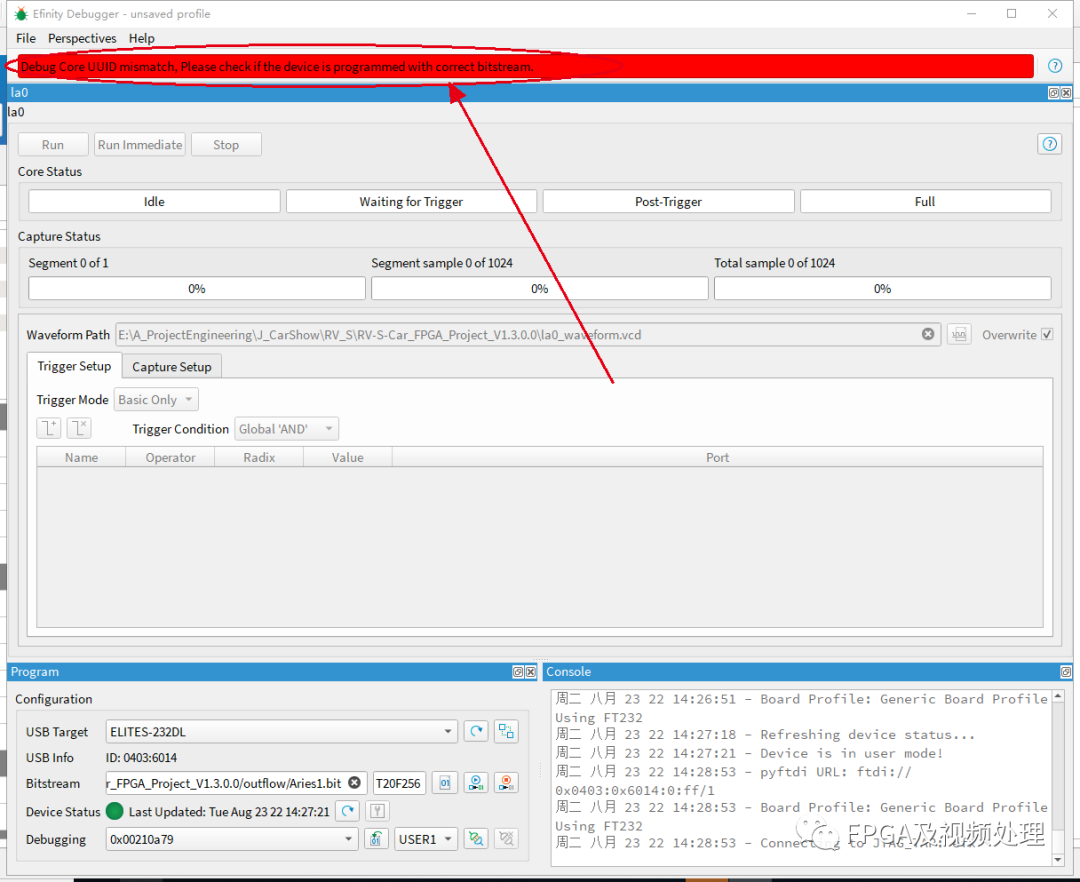

Efinity debuger常見問題總結(jié)-v3

Efinity入門使用-v2

Efinity入門使用-v3

Efinity入門使用-v4

Efinity RISC-V IDE入門使用-4

Efinity軟件安裝-v5

Efinity FIFO IP仿真問題 -v1

TINA仿真OPA846的頻率響應時,大信號(V0=2VPP),小信號(V0=0.2VPP)響應一樣,是怎么回事呢?

Efinity編譯生成文件使用指導-v1

LMV331如何讓前級電路不輸出V0波形的時候保證比較器輸出低電平?

Efinity debuger常見問題總結(jié)-v2

Efinity RISC-V IDE入門使用-3

Efinity Interface Designer報錯案例-v2

Altium Designer電氣規(guī)則設(shè)置后無報錯原因解析

Efinity Interface Designer報錯案例-v0

Efinity Interface Designer報錯案例-v0

評論