AD9249的SPI控制模塊包含4根信號線,即CSB1、CSB2、SDIO以及SCLK。但CSB1、CSB2可以一起由CSB來控制,實際上就是3線SPI。由于3線SPI數據的讀、寫操作在同一根信號線SDIO上實現,因此其配置方式與4線的配置稍微有些不一樣。下面我們將詳細介紹讀寫操作:

CSB:SPI控制讀寫使能信號;

SDIO:SPI的數據、地址讀寫端口;

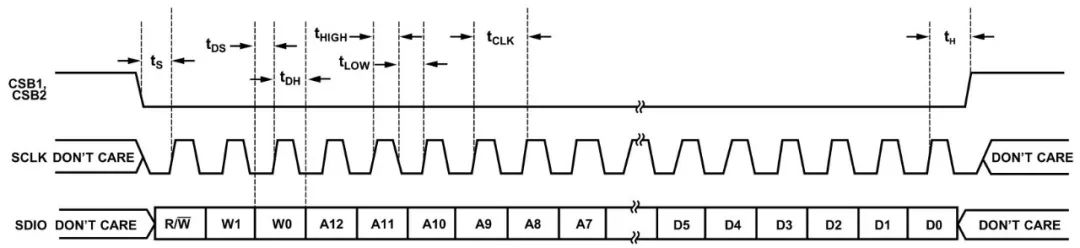

如下圖1所示為該ADC的SPI讀、寫配置時序圖。其中CSB和SCLK的操作和上篇介紹的4線SPI配置相同,圖上的時序參數在其datasheet上也有明確的說明,這里就不介紹了。

3線SPI與4線SPI配置的主要不同之處在傳輸的數據格式以及I/O轉換上。其讀寫數據格式由控制命令+地址+數據組成,而上篇提到的4線配置只有地址+數據。

圖1:SPI讀、寫時序圖

其中R/~W為高電平時,表示讀操作,低電平表示寫操作。W1,W0表示要讀寫的數據字節數,一般都設為0,代表每次讀寫一個寄存器地址的數據。A12~A0表示13bit的寄存器地址。D7~D0表示要讀寫的8bit寄存器數據。

因此我們在SPI寫操作時,只需寫入1bit 1+ 2bit 0 +13bit地址+ 8bit數據即可。其配置的方法和上篇的4線SPI寫操作相同。但當我們在執行SPI讀操作時,就需要注意了:

首先需寫入1bit 0+ 2bit 0 +13bit地址,當最后1bit的地址A0在SCLK的上升沿寫入SDIO后,SDIO會由輸入口變為輸出口,然后在接下來的8個SCLK下降沿,SDIO會輸出寄存器的8bit數據。因此,在ADC的SDIO由輸入變為輸出口時,FPGA端的SDIO必須同步由輸出口變為輸入口,并在SCLK上升沿接收這8bit數據最穩定,FPGA端口的這種I/O轉換可以通過其內置的三態門來實現。

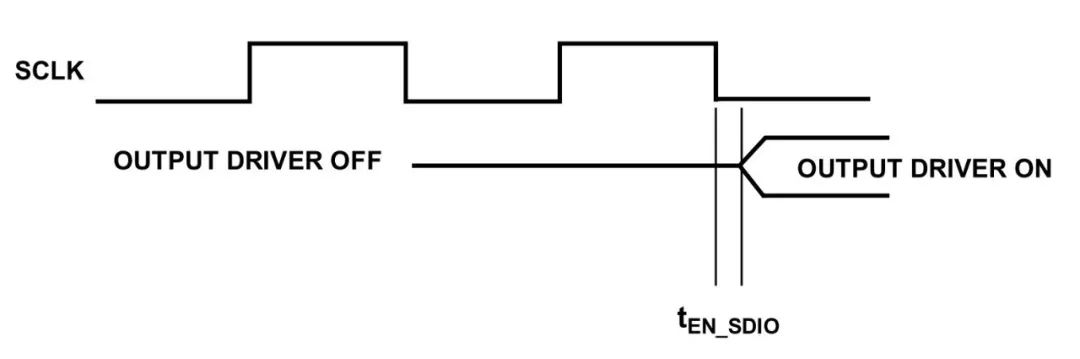

如圖2所示為SDIO由輸入口變為輸出口的時序控制圖,tEN_SDIO為轉換時間,其最小時間為10ns,參考零點為SCLK下降沿。

圖2:SDIO輸入轉換為輸出的時序圖

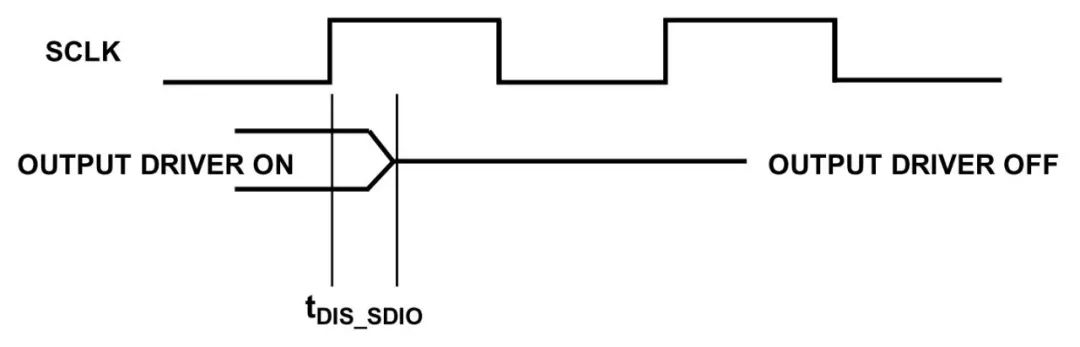

如圖3所示為SDIO由輸出口變為輸入口的時序控制圖,tDIS_SDIO為轉換時間,其最小時間也為10ns,參考零點為SCLK上升沿。

圖3:SDIO輸出轉換為輸入的時序圖

3線SPI的讀寫時序分析就介紹到這里了,同樣強調幾個關鍵點:

關鍵點1:CSB在讀寫操作時,必須拉低。讀寫完成之后,必須拉高。

關鍵點2:SDIO作為輸入口時,數據每次必須在SCLK的上升沿寫入SPI。

關鍵點3:SDIO作為輸出口時,寄存器數據每次在SCLK的下降沿輸出SPI,FPGA端在SCLK的上升沿處捕獲數據最穩定。

關鍵點4:一定要滿足datasheet給出的SPI的時序參數,并在代碼實現時要留有適當的時序裕量。

關鍵點5:注意FPGA端的SDIO口的三態控制邏輯,以便正確讀寫ADC寄存器。

本篇以Analog Device(ADI)的多通道高速ADC芯片AD9249為例,簡要介紹了ADC的3線SPI配置時序,希望我們能一起學習、一起進步!下篇將具體介紹如何用verilog實現FPGA通過SPI對ADC進行配置。

審核編輯:劉清

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

寄存器

+關注

關注

31文章

5363瀏覽量

121155 -

時序分析

+關注

關注

2文章

127瀏覽量

22615 -

SDIO

+關注

關注

2文章

73瀏覽量

19399

原文標題:FPGA通過SPI對ADC配置簡介(三)---3線SPI配置時序分析

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA中SPI復用配置的編程方法

FPGA中SPI復用配置的編程方法

FPGA通過SPI對ADC配置簡介-----什么是SPI?

ADC的4線SPI配置時序介紹與分析

在FPGA上編寫通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序

在FPGA上編寫的通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序

FPGA通過SPI對ADC配置簡介(三)3線SPI配置時序分析

FPGA通過SPI對ADC配置簡介(三)3線SPI配置時序分析

評論