引言

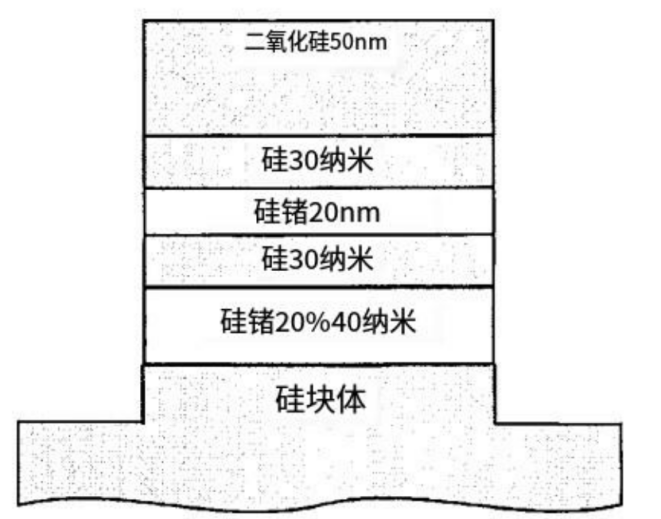

近年來,硅/硅鍺異質結構已成為新型電子和光電器件的熱門課題。因此,人們對硅/硅鍺體系的結構制造和輸運研究有相當大的興趣。在定義Si/SiGe中的不同器件時,反應離子刻蝕法(RIE)在圖案轉移過程中起著重要的作用。這種制造過程通常需要與埋著的SiGe薄膜接觸。與這些埋地區域接觸需要蝕刻硅并在薄薄的SiGe層中停止。

因此,為了實現精確的圖案轉移,我們需要一種可控蝕刻的方法。不幸的是,針對SiGe選擇性的RIE技術尚未被發現。幸運的是,利用光學發射光譜(OES)可以克服這種對硅蝕刻選擇性的不足。因此,我們研究了外延Si/SiGe多堆疊在Cl /SiCl /N氣體混合物中的干法蝕刻機理。

實驗與討論

RIE實驗是在傳統的反應離子蝕刻系統中進行的。在RIE之前,背景壓力低于10 Pa,晶片被放置在13.56 MHz射頻驅動的鋁陰極(直徑= 250 mm)覆蓋的一個石英板上。根據Si RIE的經驗,我們選擇了以下流速的Cl2/SiCl/N2、Cl2-8sccm、SiCl - 35 sccm、N2-50 sccm。使用氯是因為由于離子輔助蝕刻機制,它可以產生垂直的側壁。四氯化硅的加入有助于通過同時解吸來更好地控制溝槽的形成。

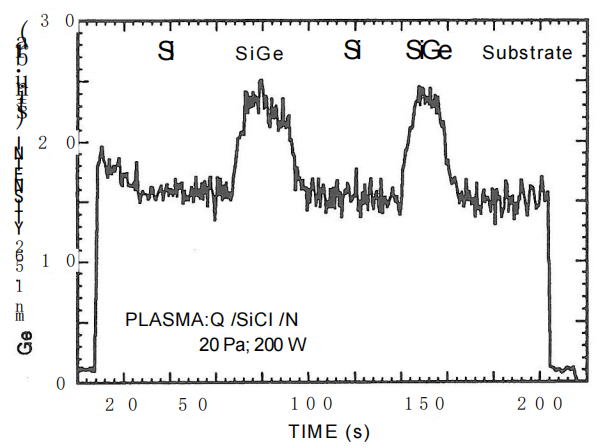

圖1顯示了樣品結構的蝕刻演變。在等離子體點火后約60秒,其中去除天然氧化物膜和硅帽發生時,我們觀察到265 nm Ge發射線的強度從其基線上升。在第一次SiGe層蝕刻過程中近似恒定,如果RIE過程繼續進入硅層,它則會減小到初始值。第二層掩埋SiGe膜的蝕刻特征是鍺發射線的反復增加強度。SiGe的蝕刻速率是Ge含量的函數,并隨著Ge含量的增加而增加。

圖1:SiGe/Si/SiGe/Si堆棧在RIE過程中,265nmGe譜線的發射強度隨時間的函數

圖1:SiGe/Si/SiGe/Si堆棧在RIE過程中,265nmGe譜線的發射強度隨時間的函數

結論

為了了解這種小的Ge富集蝕刻,英思特對表面進行了XPS分析,并與足夠的未蝕刻樣品進行了比較。英思特研究表明這種富集一些可能的原因有:與純硅的測量速率相比,SiGe合金中Ge的存在顯著增加了Si原子的揮發速率。此外,SiCln的較高揮發性(與GeCln相比)應該會導致該化合物更快的去除,并導致表面輕微的Ge富集。此外,在完成RIE過程后或在AES測量之前的空氣接觸期間,高活性的SiGe表面氧化也會導致薄氧化物層下的Ge富集。

審核編輯 黃宇

-

晶圓

+關注

關注

52文章

4973瀏覽量

128313 -

SiGe

+關注

關注

0文章

63瀏覽量

23506 -

蝕刻

+關注

關注

9文章

419瀏覽量

15508

發布評論請先 登錄

相關推薦

干法刻蝕的概念、碳硅反應離子刻蝕以及ICP的應用

芯片濕法蝕刻工藝

SiGe與Si選擇性刻蝕技術

干法刻蝕工藝的不同參數

濕法蝕刻的發展

鋰電池行業中干法研磨與濕法研磨的應用

源漏嵌入SiGe應變技術簡介

基于光譜共焦技術的PCB蝕刻檢測

消息稱SK海力士測試東京電子低溫蝕刻設備

關于兩種蝕刻方式介紹

影響pcb蝕刻性能的五大因素有哪些?

多層PCB工藝包含哪些內容和要求呢?

多層PCB板的基本結構 多層PCB板提高電路布線密度的優勢簡析

鍺化硅(SiGe)和硅(Si)之間的各向同性和選擇性蝕刻機制

Si/SiGe多層堆疊的干法蝕刻

Si/SiGe多層堆疊的干法蝕刻

評論