上一篇文章簡單講解了什么是AMBA總線,簡單來說,AMBA總線是一系列協(xié)議。定義了適用于不同場景的總線家族。今天我們就來講AMBA總線中最簡單的APB總線。

什么是APB協(xié)議/總線

APB的全稱為Advanced Peripheral Bus。顧名思義,其設計之初的主要目的就是用該協(xié)議連接外設。但由于APB總線自發(fā)布至今已經過去了20多年了,因此以現(xiàn)在的眼光看,該總線沒有什么高級一說,其連接的外設也往往是低速且低功率的外設,如I2C、UART、SPI等,除了連接低速外設之外,APB總線還廣泛用于配置各種IP的寄存器(這些IP預留用戶控制信號,由軟件進行配置,這個時候就可以選擇使用APB總線來配置這些寄存器)。

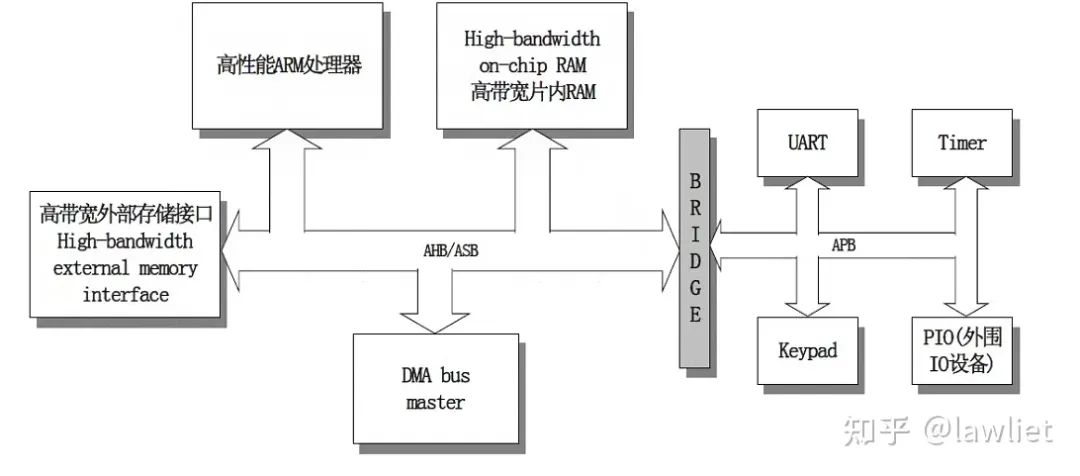

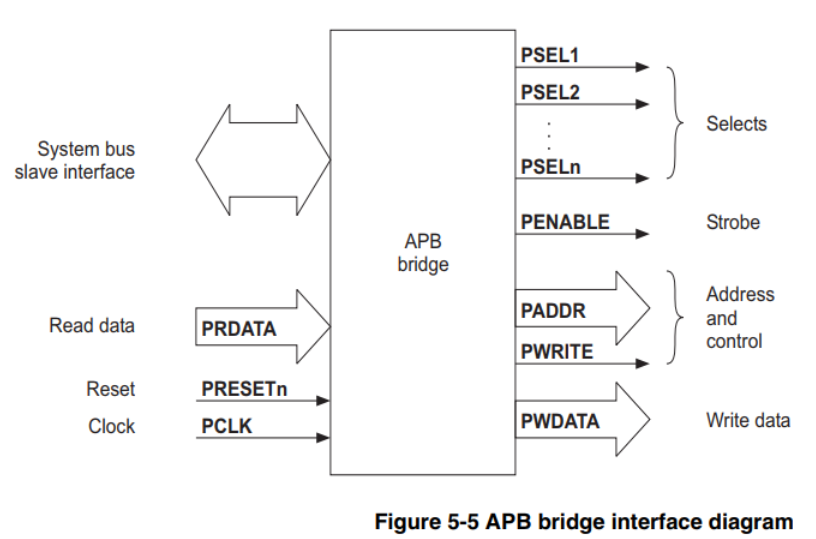

下圖為一個典型的AMBA總線的系統(tǒng)架構:其中APB總線是AHB總線的擴展,方便外設連接到系統(tǒng)總線上,其中AHB和APB之間有一個轉接橋來進行連接。

此外為了使得APB能夠容易的被整合進大部分的設計流程中,APB規(guī)定所有的信號必須在時鐘的上升沿進行傳遞。

下面簡單介紹一下APB的發(fā)展歷史,ARM公司于1998年發(fā)布了APB2,又于2003年發(fā)布了APB3,在2010年又發(fā)布了APB4。目前最常見的為APB3或APB4,其主要區(qū)別如下:

APB2:APB總線的基礎版本。

APB3:

增加PREADY信號:用于反壓master(其在讀和寫兩個場景中含義略有不同,過會講解)。

增加PSLVERR:用于代表傳輸是否發(fā)生錯誤。

APB4:

增加PPROT保護信號。

增加PSTRB代表字節(jié)選通。

APB2協(xié)議

APB2信號列表

對于AMBA協(xié)議,APB的信號都是以P開頭,AHB的信號都是以H開頭,而AXI的信號都是以A開頭。大家自己設計的時候也應該遵循這一規(guī)則。這樣一看信號名就知道使用的是什么協(xié)議。APB2的信號列表如下表所示:

| Signal name | Direction | Description |

| PCLK | Global | 時鐘信號,上升沿同步 |

| PRESETn | Global | APB總線復位信號為低有效并且通常將該信號直接連接到系統(tǒng)總線的復位信號 |

| PADDR | M-->S | 地址總線,最多可高達32位 |

| PSEL | M-->S | 選通信號,當該信號拉高意味著要發(fā)起一次傳輸了 |

| PENABLE | M-->S | 使能信號,用于表示一次APB傳輸?shù)牡诙€周期(在阻塞情況下為第二個及以上的周期,該信號的存在完全是歷史遺留問題,后面詳細講) |

| PWRITE | M-->S | 該信號為高標志這次是寫傳輸,反之則為讀傳輸 |

| PWDATA | M-->S | 寫數(shù)據(jù)總線,由Master在寫周期進行持續(xù)性驅動(PWRITE為高),最高可達32位。 |

| PRDATA | S-->M | 讀數(shù)據(jù)總線,由Slave在讀周期進行持續(xù)性驅動(PWRITE為低),最高可達32位。 |

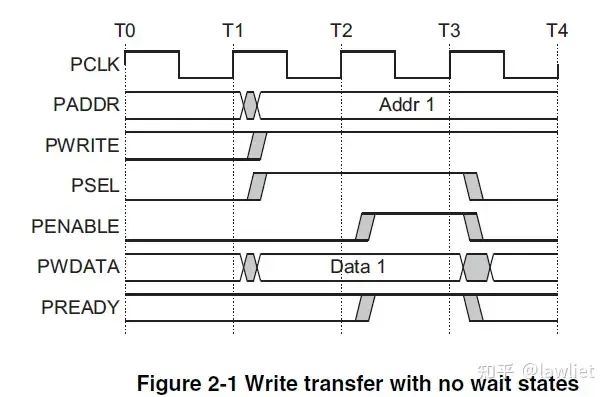

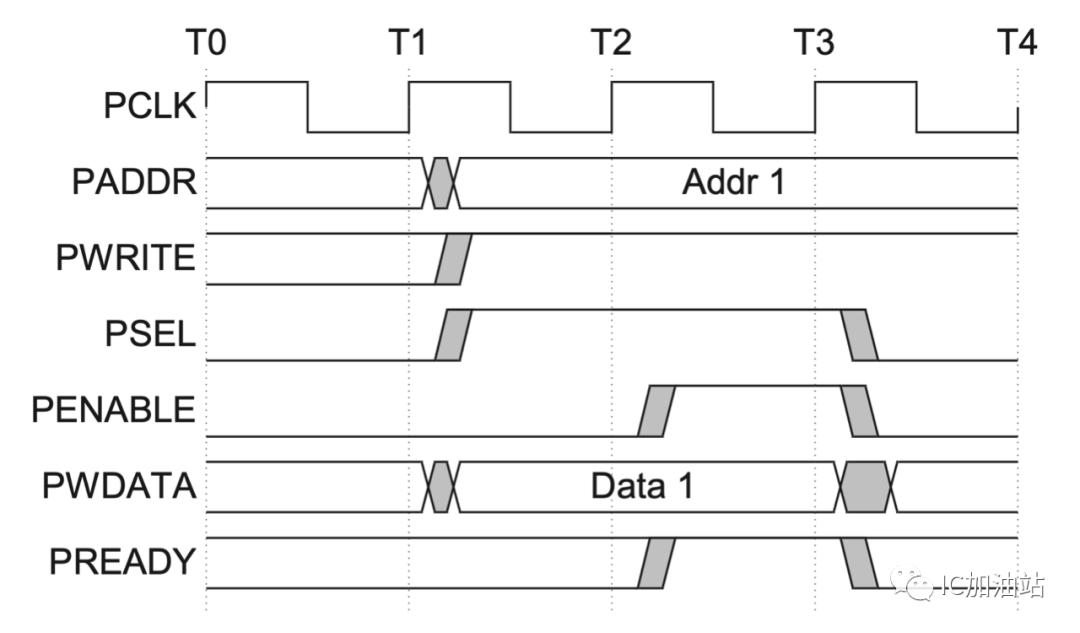

寫操作時序

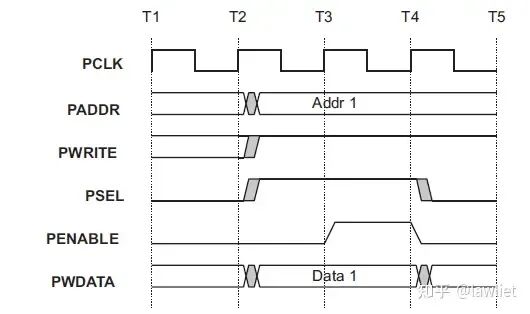

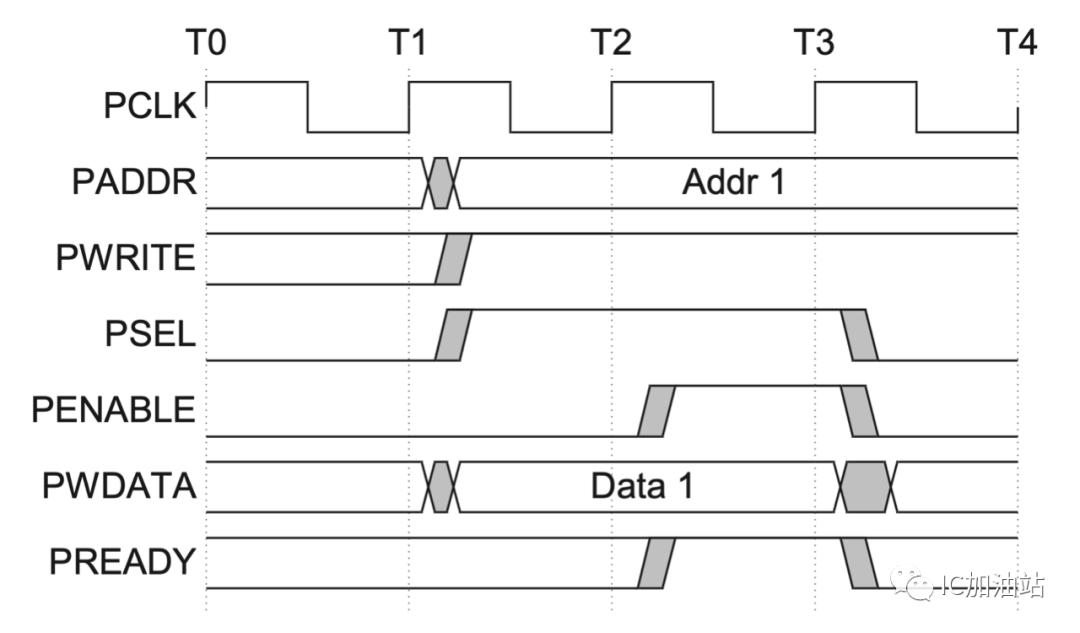

可以看到寫操作非常的簡單:

T2->T3這一個周期

PSEL信號拉高,意味著要發(fā)起一次新的傳輸了。

PWRITE信號為1,因此此次傳輸為寫操作。

PWDATA為要傳輸?shù)臄?shù)據(jù),PADDR為要寫的地址。二者都應該保持不變,直到此次傳輸結束。

而PSEL拉高的第一個時鐘周期,PENABLE應該為0。

T3->T4這一個周期

PSEL信號繼續(xù)拉高

PWRITE、PADDR、PWDATA應該保持不變

PENABLE信號拉高,用于代表這已經是寫傳輸?shù)牡诙€周期了

至此一次傳輸結束。可以看到,APB對每一筆數(shù)據(jù)的傳輸,需要花費兩個時鐘周期。且APB的數(shù)據(jù)傳輸不支持流水線操作(即不可以重疊)。因此APB是非常低效的。

理論上寫數(shù)據(jù)完全可以同時給出寫地址和寫數(shù)據(jù),一拍就搞定,為什么APB要大費周章弄成兩拍呢?這主要是那個年代的芯片本身的制程工藝以及片上互連線導致的。一個周期可能無法完成從Master向Slave寫入數(shù)據(jù)的整個操作流程。因此采用兩拍的方式,第一拍告訴你,我要開始傳輸啦!(稱為setup phase)第二拍才真正的完成數(shù)據(jù)的傳輸。(稱為access phase)。

如果Master想要馬上發(fā)起一次新的傳輸,可以不拉低PSEL讓其繼續(xù)為1,但是必須要將PENABLE拉低。否則Slave側的判斷邏輯就會出現(xiàn)問題!

由于APB向下兼容,這一歷史遺留問題一直延續(xù)至今。不過好在APB應用的場景本身就是配置寄存器等操作,因此多花一個時鐘周期也沒什么大不了的。

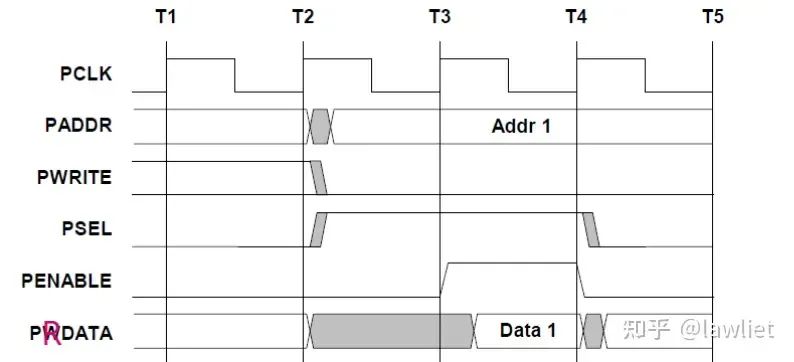

讀操作時序

可以看到讀操作非常的簡單,跟寫幾乎一樣。這里就不再做詳細的解釋了。

要特別注意的是,T3以后,也就是進入ENABLE周期后,APB的SLAVE設備必須要將M所需要讀取的數(shù)據(jù)準備好,以便M可以在ENABLE的周期末也就是T4正時鐘沿觸發(fā)時正確的將數(shù)據(jù)讀取。

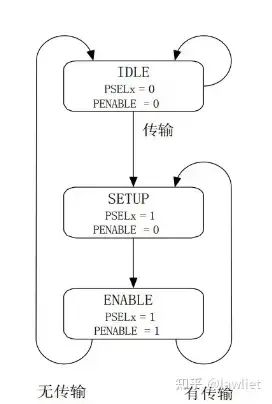

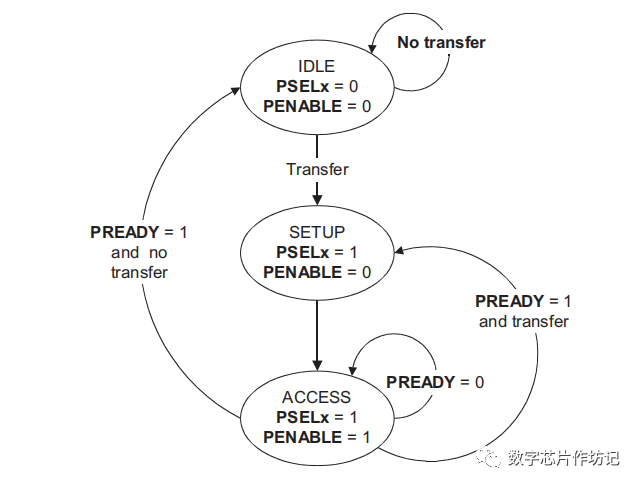

APB的狀態(tài)機

APB2的狀態(tài)機如下所示:

IDLE:此時為默認狀態(tài)。PSEL和PENABLE都為0,沒有通信請求。

SETUP:當需要發(fā)起傳輸?shù)臅r候,會進入該狀態(tài),此時PSEL為1,PENABLE為0。PSEL從0到1說明要發(fā)起一次傳輸了,而PENABLE為0表示這是傳輸?shù)牡谝粋€時鐘周期。(這個狀態(tài)也就是setup phase)

ENABLE:這個狀態(tài)PENABLE需要拉高,進而完成數(shù)據(jù)的傳輸。

這個狀態(tài)機模型只是便于我們的理解。并且這個狀態(tài)機模型是針對整個傳輸過程而言的。對于實際的master或者slave的設計完全可以不用狀態(tài)機實現(xiàn)。甚至slave都可以用純粹的組合邏輯來實現(xiàn),下面會講到如何實現(xiàn)。

APB2速問速答

Q:貌似根據(jù)上面的狀態(tài)機模型以及讀寫時序圖。有沒有PENABLE信號實際上都可以完成APB傳輸,那么APB slave是否真的需要penable信號?

A:分兩種情況討論:

如果APB slave有PCLK時鐘信號的話,那么確實是不需要penable信號的。檢測到PSEL為高,即進入到access階段。然后在第二個時鐘周期完成數(shù)據(jù)傳輸即可。相應的代碼如下所示(這段代碼是網上找到的)

`timescale 1ns/1ps `define DATAWIDTH 32 `define ADDRWIDTH 8 `define IDLE 2'b00 `define W_ENABLE 2'b01 `define R_ENABLE 2'b10 module APB_Slave ( input PCLK, input PRESETn, input [`ADDRWIDTH-1:0] PADDR, input PWRITE, input PSEL, input [`DATAWIDTH-1:0] PWDATA, output reg [`DATAWIDTH-1:0] PRDATA, ); reg [`DATAWIDTH-1:0] RAM [0:2**`ADDRWIDTH -1]; reg [1:0] State; always @(negedge PRESETn or posedge PCLK) begin if (PRESETn == 0) begin State <= `IDLE; PRDATA <= 0; end else begin case (State) `IDLE : begin PRDATA <= 0; if (PSEL) begin if (PWRITE) begin State <= `W_ENABLE; end else begin State <= `R_ENABLE; end end end `W_ENABLE : begin if (PSEL && PWRITE) begin RAM[PADDR] <= PWDATA; end State <= `IDLE; end `R_ENABLE : begin if (PSEL && !PWRITE) begin PRDATA <= RAM[PADDR]; end State <= `IDLE; end default: begin State <= `IDLE; end endcase end end endmodule

當PSEL & !PENABLE為1的時候,代表是setup stage,實際上此時slave什么都不用干

當PSEL & PENABLE為1的時候,代表是access stage,slave順勢完成數(shù)據(jù)傳輸即可

如果APB slave是純粹的組合邏輯,也就是沒有PCLK的情況下。這個時候是需要penable信號的。

APB3協(xié)議

新增的兩個信號

APB3在APB2的基礎上增加了兩個信號,PREADY和PSLVERR,這兩個信號都是由slave產生的。

對于寫操作而言,PREADY信號用于標志slave設備是否已經準備好接收這一筆數(shù)據(jù)。而對于讀操作而言,PREADY信號用于標志slave設備是否已經準備好了要返回給Master的數(shù)據(jù)。

有了PREADY信號,從機就可以反壓主機。因此PREADY這個信號可以說是非常的棒啊,它讓主從之間的通信更加的可靠,也增加了從機的控制能力,不至于出現(xiàn)主機寫的數(shù)據(jù)從機壓根沒收到或者從機沒有準備好讀數(shù)據(jù),進而主機讀到錯誤的數(shù)據(jù)的情況。

此外我再講解一下為什么會出現(xiàn)從機沒有準備好的情況。對于讀操作而言,非常好理解,你要讀的數(shù)據(jù)我還沒準備好呢(可能正在運算),那我當然不能拉高PREADY,不然就給了你錯誤的數(shù)據(jù)了。只有我數(shù)據(jù)準備好的時候,我拉高PREADY,這樣才能確保讀不出問題。而寫的話,這種情況往往出現(xiàn)在寫特定的地址,這個時候外設本身要進行判斷是否可以寫,因此兩個周期就完成不了,就暫時不能拉高PREADY,你的Master就必須要維持住。當PREADY拉高代表這一拍能夠寫進去了。因此主機也就可以不再維持原有的狀態(tài)了。

PSLVERR,(apb slave error)顧名思義。用于從slave向master返回傳輸錯誤,這個錯誤是slave自己定義的,比如寫了不允許寫的地址,即非法地址訪問。或者是訪問超時了,slave回應不了了。就可以拉高這個信號,從而避免總線鎖死。

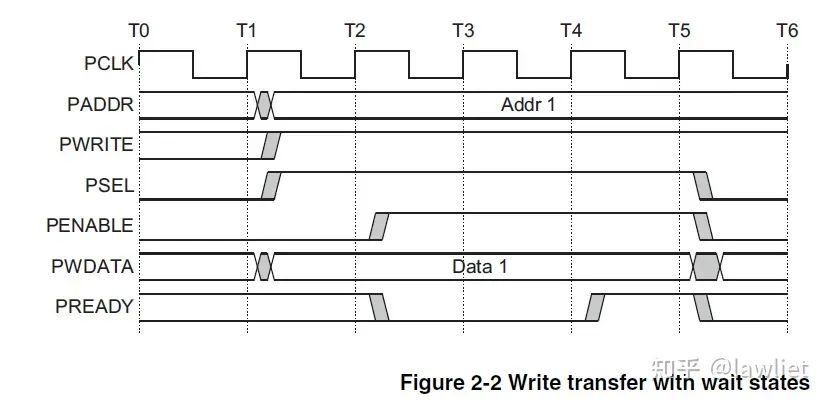

寫操作時序

上圖是沒有wait states的情況。兩拍完成寫操作。和APB2的區(qū)別在于多了個PREADY,需要在傳輸?shù)牡诙囊簿褪钦嬲l(fā)生數(shù)據(jù)傳輸?shù)哪且慌睦摺F渌暮蜕厦娴膶憰r序是一模一樣的,因此不再講解。

我們再看看有wait states的情況,上圖四拍才完成寫操作。此時setup還是一個周期(從T1->T2),而access是三個時鐘周期(從T2->T5)。可以看到主機的信號應該保持不變,一直持續(xù)到從機的PREADY信號拉高以后,等待拉高以后的這一拍完成傳輸,才可以改變其它的信號。(即T1->T5這段過程,PADDR、PWRITE、PSEL、PWDATA都應該保持不變)。

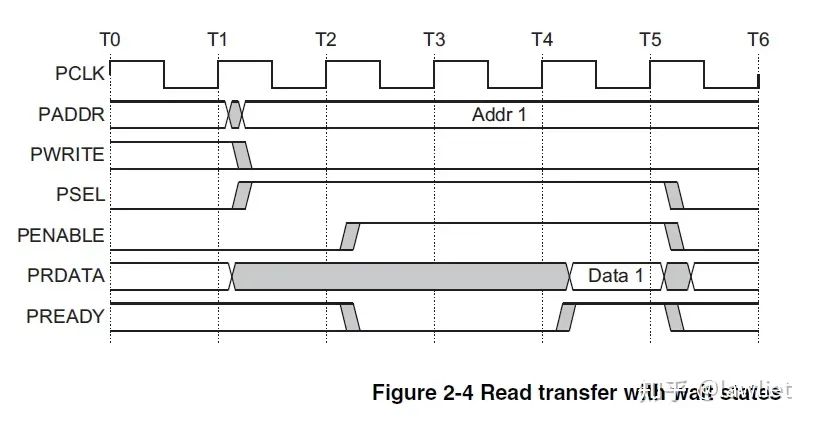

讀操作時序

我們直接看復雜點的情況,可以看到PREADY信號和PRDATA信號在同一拍發(fā)生變化。此時的PREADY信號也可以理解為從機此時提供的PRDATA才是有效的數(shù)據(jù)。進而完成了一次完整的傳輸過程。

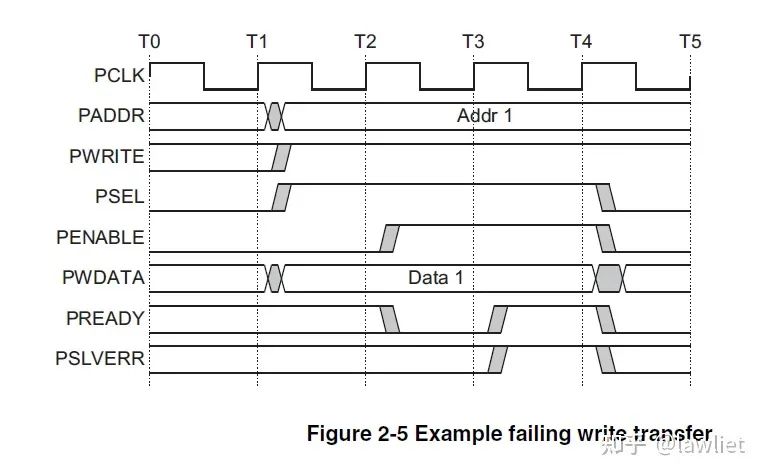

Error response

以寫為例,實際上就是在真正發(fā)起傳輸?shù)哪且慌模ㄒ簿褪荘READY拉高的那一拍)順勢拉高PSLVERR,用于標志這次傳輸失敗。

為什么需要APB4?

APB4在APB3的基礎上又增加了PPROT和PSTRB信號。

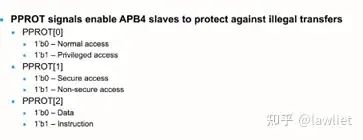

PPROT信號有三個比特,含義分別如下:

對于CPU而言,可以工作在用戶模式下也可以工作在特權模式下(比如RISC-V的USM三種模式)。對于支持trustzone的CPU,可以工作在secure world下,也可以工作在normal mode下。又由于現(xiàn)在的系統(tǒng)越來越復雜了,以前的外設是隨意讀寫都可以,現(xiàn)在的一些外設或memory(比如一些CSR寄存器,Trusted RAM等)要求只能在secure下或者privileged模式下訪問,因此就需要PPROT信號。

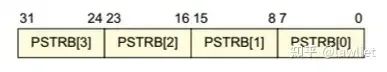

而PSTRB信號則比較好理解,它允許稀疏的寫。其中的每一個比特對應于PWDATA的每一個字節(jié)。用1代表PWDATA的這一字節(jié)是否有效,其對應關系如下圖所示:

至于讀的話把PSTRB隨便讓它是啥就行,不翻轉最好以減少功耗。這個信號是針對寫而言的,讀的話無所謂。

APB4和APB3以及APB3和APB2的兼容性問題

以APB4的slave和APB3的master為例,這個時候應該把PSTRB信號固定為全1,PPROT信號則取決于Slave是如何使用該信號的,根據(jù)不同的場景固定為不同的值。

而APB3的slave和APB4的master相連接,這個時候實際上需要一個轉接橋,因為本身可能只想寫某一個字節(jié),而slave此時不支持也不知道,那就需要一個中間邏輯將pwdata變成想要的值。(比如讀回來時32'h2345,想將最高字節(jié)改寫為6,此時只寫一個32'h6000,PSTRB為1000,標志別的字節(jié)不要動。這個時候就需要一個中間邏輯將寫的數(shù)據(jù)變成32'h6345)。實際上寫起來也很麻煩,因此此時最好將APB3的slave改成APB4協(xié)議。

至于APB3和APB2不建議一起用,因為APB2沒有PREADY反壓機制,因此實際使用起來完全不一樣,強行一起用會有巨大的坑。

審核編輯:劉清

-

RAM

+關注

關注

8文章

1369瀏覽量

115002 -

AMBA總線

+關注

關注

0文章

35瀏覽量

9612 -

狀態(tài)機

+關注

關注

2文章

492瀏覽量

27647

原文標題:【芯片設計】深入理解AMBA總線(一)APB總線入門

文章出處:【微信號:IC修真院,微信公眾號:IC修真院】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

APB和AHB總線區(qū)別

ARM總線協(xié)議AMBA中AHB、APB的區(qū)別與聯(lián)系

AMBA AHB總線與APB總線資料合集

AMBA中的APB總線協(xié)議詳解

APB總線的應用框圖及接口信號

數(shù)字IC驗證:ARM總線協(xié)議AMBA中AHB、APB的簡介、區(qū)別與聯(lián)系

AXI總線協(xié)議:AHB、APB、AXI對比分析

AMBA總線那些事之APB

AMBA總線—apb簡介

AMBA總線那些事之APB協(xié)議入門

關于AMBA APB總線的知識點介紹

SOC設計中APB協(xié)議總線的工作原理

什么是APB協(xié)議/總線?APB總線入門

什么是APB協(xié)議/總線?APB總線入門

評論