硅 IP 提供商和合約芯片設(shè)計商 Alphawave 本月與測試和驗證設(shè)備制造商是德科技合作,展示了其 PCIe 6.0 控制器和物理接口與是德科技測試設(shè)備的互操作性,數(shù)據(jù)傳輸速率為 64 GT/ s。此舉證明 Alphawave 已準(zhǔn)備好構(gòu)建帶有PCIe 6.0 接口的芯片,加入了越來越多的公司行列,為 2024 年首批商用 PCIe 6.0 設(shè)備的到來準(zhǔn)備生態(tài)系統(tǒng)。

IP 提供商 Synopsys 自 2021 年以來一直提供包含控制器和物理接口 (PHY) 的 PCIe 6.0 IP 包,今年早些時候,該公司展示了其 PCIe Gen6 解決方案與英特爾測試芯片的互操作性。

Alphawave 的 PCIe 6.0 64 GT/s 接口芯片實現(xiàn)不僅可與是德科技協(xié)議訓(xùn)練器全速配合使用四級脈沖幅度調(diào)制 (PAM4) 信令,而且還支持業(yè)界首創(chuàng)的 CXL 2.0 協(xié)議。該實現(xiàn)還完全支持 PCIe Gen6 的前向糾錯 (FEC)、FLIT 模式以及新互連標(biāo)準(zhǔn)的其他功能。此外,該 PCIe Gen6 平臺還可以通過 CXL 3.0 協(xié)議進(jìn)一步擴(kuò)展。

Alphawave Semi IP 產(chǎn)品營銷副總裁 Letizia Giuliano 表示:“測試和測量是互操作性的關(guān)鍵方面,使 Alphawave Semi 能夠更快地將我們的產(chǎn)品和客戶解決方案推向市場。” “我們對與是德科技的合作感到非常興奮,雙方通過是德科技最先進(jìn)的 PCIe 6.0 協(xié)議驗證解決方案加速了向 64 GT/s 的過渡,并讓我們對持續(xù)提供可加速 AI 處理的連接解決方案的能力充滿信心。高性能計算和數(shù)據(jù)基礎(chǔ)設(shè)施。”

Synopsys 主要將其 IP 和技術(shù)授權(quán)給大型芯片設(shè)計人員。相比之下,Alphawave 為不傾向于自行設(shè)計或?qū)嵤?IP 的小公司開發(fā)定制芯片或許可技術(shù)。該公司聲稱其 PCIe 子系統(tǒng)極其節(jié)能、延遲低,并且“基于業(yè)界最成功的 PAM4 SerDes IP 構(gòu)建”。此外,該 PCIe Gen6 平臺還可以通過 CXL 3.0 協(xié)議進(jìn)一步擴(kuò)展。

PCIE二十年:總線的過去、現(xiàn)在和未來

在 PCI Express 誕生 20 周年之際,我們回顧一下這一盛行的擴(kuò)展插槽的過去和未來。

PCI Express (PCIe) 總線誕生于 PC 中的擴(kuò)展插槽數(shù)量與 CPU 時鐘速度或系統(tǒng) RAM 數(shù)量同等重要的時代。此后,PCIe總線從一組插槽、插入式擴(kuò)展卡發(fā)展到高速互連拓?fù)洹?/p>

PCIe 總線的開始:IBM 和 5150 PC

PCIe 總線起源于 1981 年推出的IBM PC 型號 5150。5150 的熱門前身(例如 Apple II)使用開放標(biāo)準(zhǔn)總線或發(fā)布了第三方擴(kuò)展板的總線規(guī)范。這種競爭壓力促使 IBM 開放 5150 總線并發(fā)布其規(guī)范。

在 IBM 的支持下,整個行業(yè)都是圍繞為 IBM PC 總線設(shè)計和提供擴(kuò)展卡而建立的。IBM 的第二個 PC 型號 PC/AT 將總線數(shù)據(jù)寬度從 8 位提高到 16 位,并保持開放式架構(gòu)。許多公司在他們的 PC 克隆中使用了總線,稱為 PC 兼容機(jī)。總線在擴(kuò)展板和 PC 克隆行業(yè)中的廣泛使用導(dǎo)致了總線的行業(yè)標(biāo)準(zhǔn)架構(gòu) (ISA)。這對消費者和 PC 克隆制造商來說是件好事,但它奪走了 IBM 的控制權(quán)和許可收入。

IBM 試圖重新獲得標(biāo)準(zhǔn)控制權(quán)

20 世紀(jì) 80 年代末,新的處理器和更快的速度使得 ISA 總線變得過時。IBM 推出了其新的專有微通道總線,試圖解決 ISA 的缺點。該公司保持微通道的專有性,以從出售給 PC 兼容制造商的許可費中獲利。然而,PC 行業(yè)遷移到由PCI 特別興趣小組(PCI-SIG ) 維護(hù)的英特爾 32 位外圍組件互連 (PCI) 總線 。

雖然 PCI 總線與微通道一樣速度更快,但它是一個開放的行業(yè)標(biāo)準(zhǔn)。PCI 開創(chuàng)了一種無需附加卡即可將主板內(nèi)置外設(shè)連接到總線的架構(gòu)。在以前的 ISA 架構(gòu)中,主板內(nèi)置的外設(shè)通常需要定制的非標(biāo)準(zhǔn)接口電路。PCI 總線提供了一個板載外圍接口,在電氣上相當(dāng)于將板插入插槽,從而更容易實現(xiàn)板載集成和軟件支持。

PCI 總線(仍然)不足

盡管 PCI 提供了比 ISA 更高的性能,但它繼承了 ISA 拓?fù)涞脑S多缺點。與 ISA 一樣,PCI 總線也采用共享并行數(shù)據(jù)總線架構(gòu)。雖然 PCI 在速度潛力和信號完整性方面取得了重大進(jìn)步,但它仍然需要每個外設(shè)共享資源并協(xié)商單獨的總線訪問。

圖形加速卡制造商比其他接口卡制造商更早遇到這些限制,這促使了加速圖形端口(AGP)的開發(fā)。AGP 是 PCI 的超集,它脫離了總線共享,并在 AGP 卡插槽和主板芯片組之間提供了直接路徑。

輸入 PCI Express

2003 年,PCI-SIG 進(jìn)一步應(yīng)對這些挑戰(zhàn),推出了至今仍在使用的PCI Express 總線。PCIe 取代了所有主流 PC 總線,包括 AGP 接口。PCI-SIG 在 2001 年至 2003 年間制定了該標(biāo)準(zhǔn),PCI 產(chǎn)品于 2004 年開始發(fā)貨。

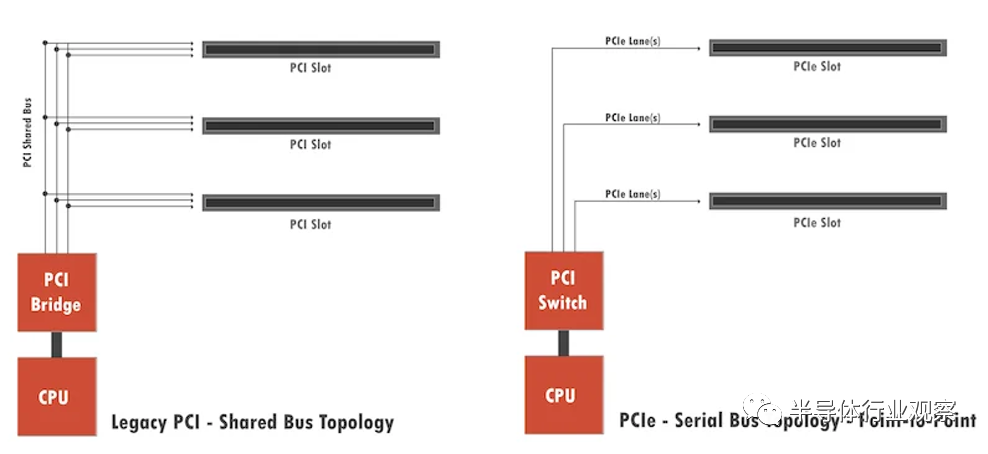

PCIe 總線與 PCI 總線有兩個重要的區(qū)別。它沒有使用共享總線主控拓?fù)洌遣捎命c對點系統(tǒng)通過通用主機(jī)控制器直接連接設(shè)備。它還從并行數(shù)據(jù)路徑轉(zhuǎn)變?yōu)閱蜗虼袛?shù)據(jù)路徑。

PCI 中的共享總線與 PCIe 中的串行點對點拓?fù)洹?/p>

使用舊的 PCI 和 ISA 總線主控拓?fù)洌淮沃挥幸粋€外設(shè)可以訪問總線。每個都根據(jù)需要協(xié)商主站狀態(tài),等到它能夠獲得控制權(quán),然后采取行動。即使使用直接內(nèi)存訪問 (DMA),也幾乎無法并行執(zhí)行。這些舊拓?fù)錆M足了 20 世紀(jì) 80 年代緩慢應(yīng)用程序的需求,但遠(yuǎn)遠(yuǎn)不足以滿足新千年出現(xiàn)的游戲、高速網(wǎng)絡(luò)或復(fù)雜圖形界面的需求。

為什么 PCIe 向前邁出了一大步?

PCIe 不僅僅是一個物理插槽標(biāo)準(zhǔn)。總線的主力是拓?fù)洹CIe 用于連接內(nèi)置外設(shè)、筆記本電腦和迷你 PC 的附加卡以及 SSD 存儲。Mini PCIe 使用相同的拓?fù)洹⒕幋a和規(guī)格,并且與常規(guī) PCIe 電氣兼容。現(xiàn)在常見的M.2 SSD接口也采用PCIe拓?fù)洹?/p>

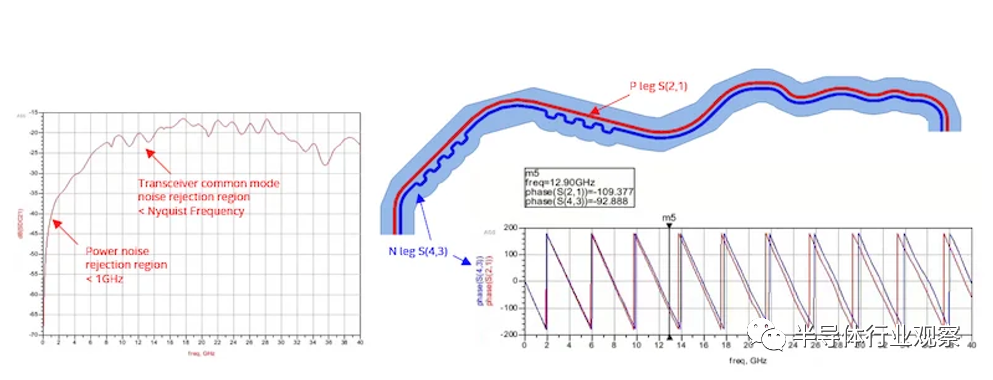

PCIe 的串行數(shù)據(jù)路徑使用單向差分對來提高信號完整性。雖然這些線對需要進(jìn)行長度匹配才能消除偏斜,但每對的兩條跡線比 8、16 或 32 條跡線更容易處理。

差分信號走線的去偏技術(shù)

高速并行總線也可能受到串?dāng)_的影響,串?dāng)_是一種從一條走線到另一條走線的信號泄漏。這會導(dǎo)致數(shù)據(jù)損壞并限制帶寬。差分配對信號可消除大部分串?dāng)_并提供更清晰的信號。

PCIe 差分對的優(yōu)勢

PCIe的單向差分對由四根走線組成,作為每個方向的差分對。每組四個連接稱為一個通道,PCIe 插槽可支持 1 到 16 個通道。用于連接兩個 PCIe 設(shè)備的通道組稱為互連或鏈路。現(xiàn)代圖形加速器通常使用 16 通道插槽,有些需要兩個插槽和額外的電源連接。

差分對布置可加快傳輸速度并提高可靠性。在 PCIe 版本 1.0 和 2.0 中,數(shù)據(jù)以帶有兩個開銷位的 8 位字傳輸,稱為 8b/10b 編碼。這意味著 20% 的傳輸比特是開銷,而不是數(shù)據(jù)。PCI 3.0 將這一數(shù)字提升至 128b/130b 編碼,產(chǎn)生 98.5% 的數(shù)據(jù)率和 1.5% 的開銷。這種編碼從 PCIe 1.0 到 5.0 一直保留,表示具有不歸零(NRZ) 格式的二進(jìn)制數(shù)據(jù)。

PCIe 1.0 至 7.0:傳輸速度加倍

PCIe 1.0 每通道傳輸速度高達(dá) 2.5 GB/s,16 通道互連時最高傳輸速度為 4 GB/s。隨著協(xié)議和芯片制造能力的改進(jìn),PCIe 2.0 使這一數(shù)字翻了一番。PCIe 3.0 從 8b/10b 提升到 128b/130b,速度幾乎翻倍至每通道 8 GB/s。此后的每個新版本的數(shù)據(jù)速率都增加了一倍。

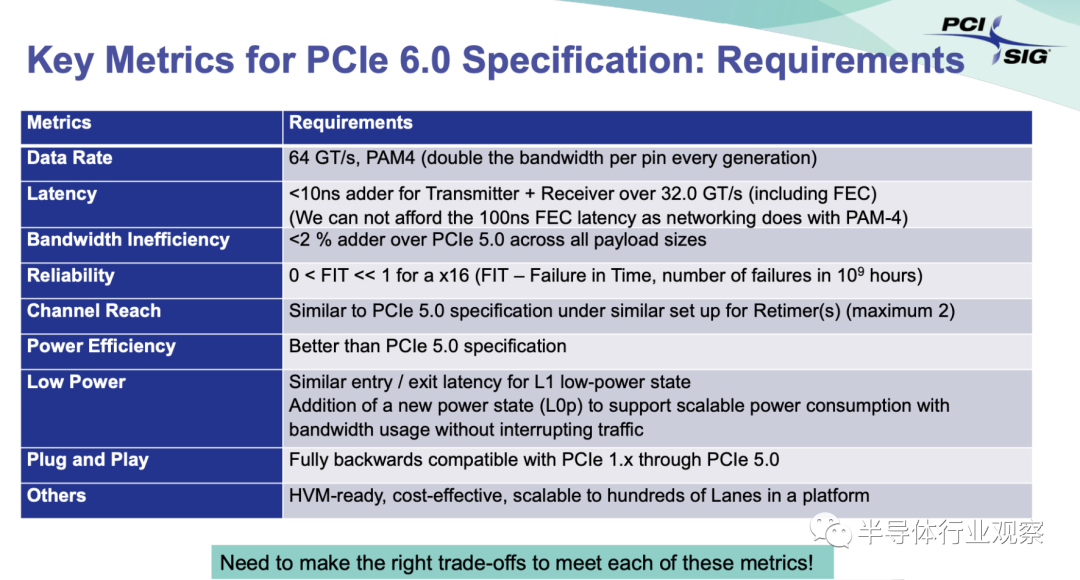

2022 年推出的 PCIe 6.0 在編碼和協(xié)議方面帶來了重大變化,將速度提升至 64 GB/s。PCIe 6.0 從 NRZ 數(shù)據(jù)格式更改為脈沖幅度調(diào)制 4 級(PAM4) 信令。PAM 表示與 NRZ 中的一位相同單位間隔中的兩位,它給出四個值而不是兩個。這有效地用兩位值替換了二進(jìn)制位。PAM4 的錯誤率要高得多,因此需要高級糾錯。截至撰寫本文時,使用此標(biāo)準(zhǔn)的卡尚未上市。

PCI-SIG 預(yù)計自 2022 年 6 月以來一直在開發(fā)的 PCIe 7.0 將在 2024 年得到鞏固。該標(biāo)準(zhǔn)承諾通過微調(diào)通道參數(shù)來提高功率效率并減少信號損失,從而將 PCIe 6.0 數(shù)據(jù)速率提高一倍。PCIe 7.0 硬件要到 2027 年才會出現(xiàn)在市場上。

擴(kuò)展槽的日子已經(jīng)屈指可數(shù)了嗎?

20 年前的 PCIe 總線在當(dāng)今的 PC 世界中仍然可以辨認(rèn),2004 年的主板設(shè)計人員也可能很容易認(rèn)出今天的 PCIe。然而,20年后情況可能并非如此。

當(dāng) PCIe 開發(fā)時,USB 還處于起步階段。多種設(shè)備需要計算機(jī)中的插槽。那個時代的許多個人電腦仍然需要附加聲卡、調(diào)制解調(diào)器、網(wǎng)卡和無線接口。對于當(dāng)今的典型用戶來說,這些應(yīng)用程序都不需要附加卡。雖然游戲圖形加速器、高端視頻和聲音處理設(shè)備以及奇異或特殊用途的產(chǎn)品仍然使用插入式 PCIe 板,但大多數(shù)家庭和商用 PC 和筆記本電腦都內(nèi)置了所有這些(以及更多)或可通過USB。

目前大多數(shù)筆記本電腦和迷你電腦除了 M.2 SSD 接口外不使用卡插槽。雖然人們?nèi)匀皇褂?PCIe 連接主板上的各個子系統(tǒng),但使用許多擴(kuò)展插槽的日子可能已經(jīng)屈指可數(shù)了。

原文鏈接

https://www.tomshardware.com/pc-components/ssds/pcie-60-inches-closer-to-arriving-in-the-market-in-2024-alphawave-demonstrates-interoperability

審核編輯:劉清

-

控制器

+關(guān)注

關(guān)注

112文章

16445瀏覽量

179447 -

RAM

+關(guān)注

關(guān)注

8文章

1369瀏覽量

115002 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1028瀏覽量

55006 -

PCIe

+關(guān)注

關(guān)注

15文章

1260瀏覽量

83186 -

PHY

+關(guān)注

關(guān)注

2文章

305瀏覽量

51862

原文標(biāo)題:PCIe 6.0加速來了, PCIe 向前邁出了一大步?

文章出處:【微信號:線纜行業(yè)朋友分享圈,微信公眾號:線纜行業(yè)朋友分享圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

光纖布拉格光柵色散補(bǔ)償技術(shù)如何支持新型低成本放大器設(shè)計和新的應(yīng)用方式?

同創(chuàng)國芯領(lǐng)銜 國產(chǎn)FPGA邁進(jìn)一大步

中國聯(lián)通4G邁出一大步 20個月完成70萬個基站

車聯(lián)網(wǎng)產(chǎn)業(yè)走向風(fēng)口 百度安全技術(shù)邁出一大步

2018年無人駕駛將脫離人類司機(jī)向前邁出一大步

朝著自旋晶體管的目標(biāo)邁進(jìn)一大步

為什么PCIe向前邁出了一大步?

為什么PCIe向前邁出了一大步?

評論