本文來自“AI服務器白皮書(2023年)”,人工智能行業是對算力、算法和數據等數字資源進行創造、加工、整合,最終實現用機器替代人,為傳統行業智慧賦能。算力、算法、數據是人工智能的三大要素。人工智能產業鏈包括三層:基礎層、技術層和應用層。

(1)基礎層:人工智能產業的基礎,主要提供 AI 專有算力支持和開發環境的設備和服務,包括 AI 芯片、 系統開發框架、AI 服務器等基礎設施等;

(2)技術層:在 AI 算力的支持下,通過系統開發框架進行各場景數據的訓練和 學習,開發出計算機視覺、語音語義、知識圖譜等 AI 算法,并將其搭載于硬件設備上形成行業級解決方案;

(3)應用層:針對不同的行業和場景,進行人工智能技術的商業化落地。

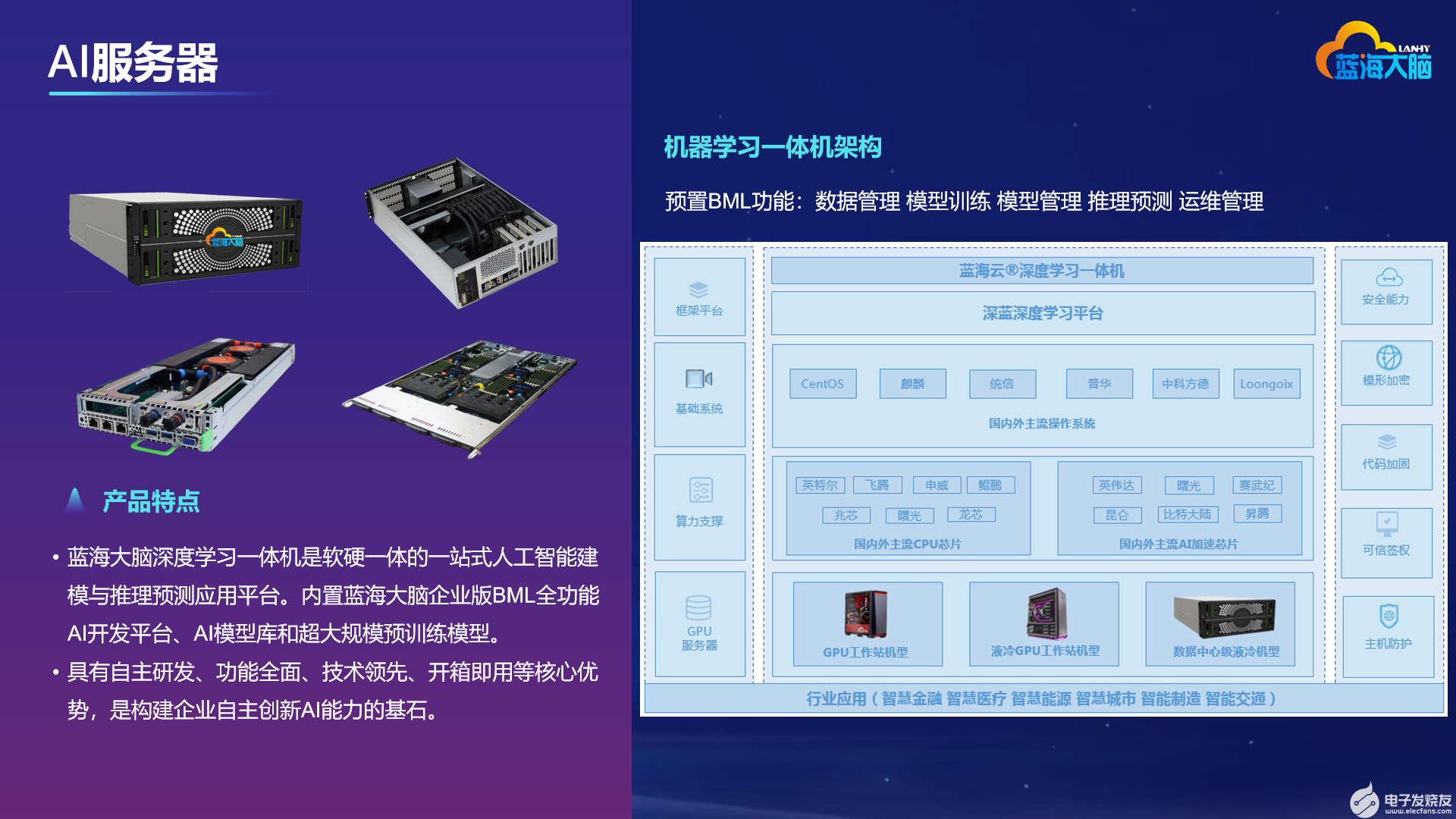

AI 服務器是人工智能基礎層的核心物理設備,其面向深度學習神經網絡需要的快速,低精度,浮點運算高度并行數值計算,搭載大量計算內核和高帶寬內存資源,用于支撐深度學習訓練和線上推理計算框架模型和應用,可以在多個節點之間高速互聯、高效地擴展的硬件平臺。有別于傳統服務器以 CPU 提供主要算力,人工智能服務器多采用異構架構進行加速計算,常采用CPU+GPU、CPU+FPGA、CPU+ASIC 等多種形式。通過搭配不同的異構加速芯片,形成不同性能和可編程靈活性的人工智能算力硬件。目前廣泛使用的 AI 服務器是 CPU+GPU。

通過 AI 服務器構成人工智能基礎層的智能算力集群,聯合智能模型平臺和數據基礎服務平臺,支撐技術層和應用層的人工智能應用場景落地。隨著大模型訓練對云端算力的持續增長需求,AI 服務器部署規模越來越大,持續增長的計算速度和計算效率需求,推動著 AI 服務器的人工智能行業技術迭代。

(一)AI 服務器總體架構

隨著人工智能和大模型應用的持續演進和廣泛部署,“CPU+”架構已成為人工智能服務器的設計藍本。

在這一架構中,CPU繼續發揮其作為系統的中央處理單元的關鍵角色,負責任務的調度、系統管理和部分計算工作。然而,為了適應大模型和特定 AI 應用的計算密集性需求,服務器必須融合其他具有豐富計算核心的硬件加速器,能夠在短時間內處理大量的數據和計算任務。

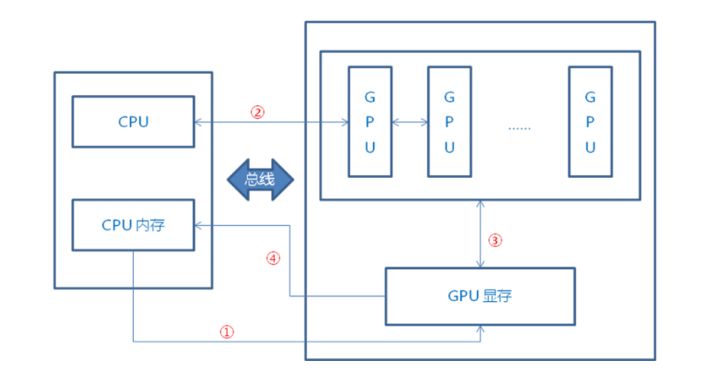

以人工智能計算領域中廣泛使用的 GPU 計算部件為典型代表,詳細描述了在現代“CPU+”架構中,人工智能加速部件與 CPU 的協同工作流程。在這種架構中,待處理的數據首先從 CPU 內存傳輸到GPU 的顯存。這一步通常涉及大數據量的遷移,因此高帶寬和低延遲的內存接口如 PCIe 和 NVLink 成為了優化的關鍵。一旦數據被載入顯存,CPU 便開始向 GPU 發送程序指令。這些指令利用 GPU 的并行性能,驅動其多達數千的計算核心去執行。利用 GPU 的強大并行計算能力,顯存中的數據會被快速處理。例如,在深度學習中,GPU可以并行處理大規模的矩陣乘法和卷積操作。計算完成后,結果存儲在顯存中,并在需要時傳輸回 CPU 內存。從“CPU+”這種架構的應用可以明顯看出 CPU 的角色更偏向于指令協調和結果匯總,而實際上的高并行度計算任務則交給了 GPU 這類加速部件。這種分工策略符合 Amdahl 定律的觀點:系統的總體性能提升受制于其最慢部分。

因此,通過優化可并行化的計算部分,將 CPU 和專門設計的硬件加速器如 GPU 結合,從而實現高效并行處理,滿足日益增長的計算需求。

(二)異構計算加速計算芯片

異構計算指的是在一個計算系統中使用多種不同類型的處理器或核心來執行計算任務。這種方式旨在利用各種處理器的特定優勢,以獲得更高的性能或能效。

傳統服務器系統內處理器以 CPU(即中央處理單元)為主。CPU 有很強的通用性,需要處理各種不同的數據類型,通常負責執行計算機和操作系統所需的命令和流程,因此其擅長無序超標量與復雜控制指令級的執行。

本輪人工智能熱潮的理論基礎是人工神經網絡,為了更好地訓練和使用深度神經網絡,就需要對計算密集型大規模矩陣進行并行處理。CPU 的架構決定了其難以適用于大規模的人工智能計算。而異構計算加速器集成大量計算核心,簡化邏輯控制單元設計,提升系統的并行計算性能。

當前異構計算加速器發展呈現多樣化。人工智能芯片按照技術架構分類,可以劃分為圖像處理單元(GPU)、現場可編程門陣列(FPGA)、專用集成電路(ASIC)等。

GPU:AI 算力的核心

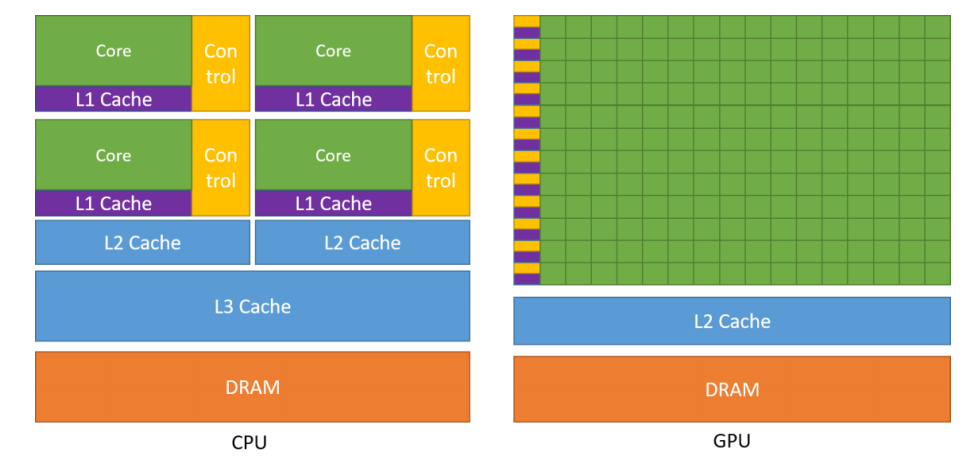

CPU 作為中央處理核心,其硬件架構中為了滿足高性能和低 延 遲 的 需 求 , 特 地 增 強 了 高 速 緩 存 ( Cache ) 和 控 制 單 元(Control)的比例。相較之下,算術邏輯單元(ALU)在整體構造中所占的份額較小,這限制了 CPU 在大規模并行計算方面的表現。

GPU 的架構以計算單元為核心,采用了高度精簡且高效的流水線設計,專為處理高度并行和線程化的計算任務而生,具有大規模并行計算的能力。

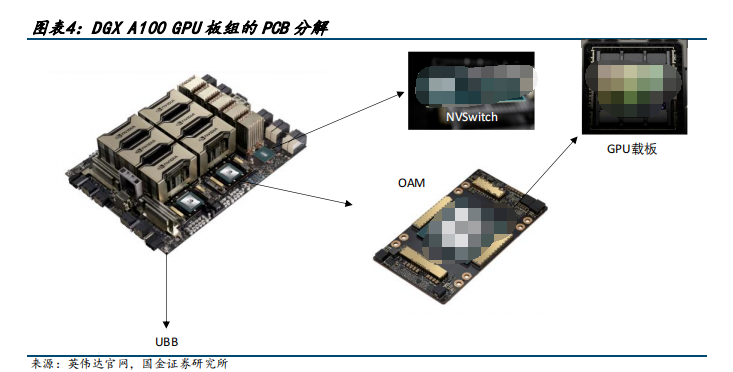

傳統的 GDDR 顯存模塊通常焊接在 GPU 的 PCB 板上,這種配置可能會限制數據傳輸的速率和總存儲容量。隨著技術的發展,這些限制逐漸成為了圖形處理性能的瓶頸。為了解決這個問題,HBM (High Bandwidth Memory) 技 術 應 運 而 生 。HBM 使用了 TSV(Through-Silicon Vias) 技術,允許多個 DRAM 芯片垂直堆疊起來,從而實現更高的數據帶寬。HBM 與 GPU 核心的連接則是通過一個特殊的互連層實現,這不僅進一步提高了數據傳輸速率,而且大大減少了 PCB 的使用面積。

盡管 HBM 在帶寬、體積和能效上都展現出了明顯的優勢,但由于其生產成本相對較高,GDDR 仍然是消費級 GPU 市場的主流選擇。而在對性能和能效要求更高的數據中心環境中,HBM則得到了更廣泛的應用。

(1) NVIDIA GPU

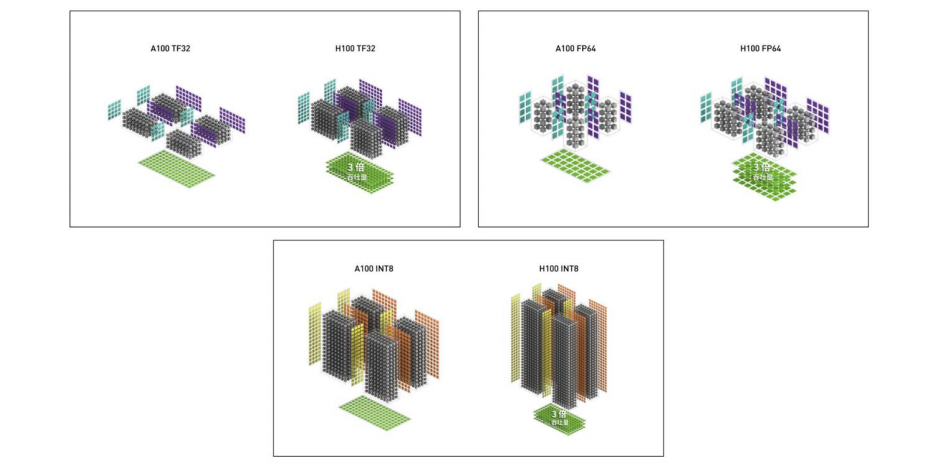

2022 年春季 GTC 大會上,英偉達發布其新款 NVIDIA GraceHopper 超級芯片產品,Hopper H100 Tensor Core GPU。

Tensor Cores 是專門針對矩陣乘法和累加(MMA)數學運算的高性能計算核心,為 AI 和 HPC 應用提供了開創性的性能。當 TensorCores 在一個 NVIDIA GPU 的多個流多處理器(SM)中并行操作時,與標準的浮點數(FP)、整數(INT)和融合乘法-累加(FMA)運算相比,它們能夠大幅提高吞吐量和效率。

(2)英特爾 Gaudi2 GPU

Gaudi2 深度學習加速器,以第一代 Gaudi 高性能架構為基礎,以多方位性能與能效比提升,加速高性能大語言模型運行。具備:24 個可編程 Tensor 處理器核心(TPCs);21 個 100Gbps(RoCEv2)以太網接口;96GB HBM2E 內存容量;2.4TB/秒的總內存帶寬;48MB片上 SRAM。

Gaudi2 處理器提供 2.4T 的網絡帶寬,片上集成 24 x 100 GbpsRoCE V2 RDMA 網卡,可通過標準以太交換或直連路由實現 Gaudi 芯片內部通信;Gaudi2 的內存子系統包括 96 GB 的 HBM2E 內存,提供2.45 TB/秒的帶寬,此外還有 48 MB 的本地 SRAM,帶寬足以允許 MME、TPC、DMAs 和 RDMA NICs 并行操作;支持 FP32,TF32,BF16,FP16 和FP8。

通過在 GPT-3 模型上的測試,以及相關 MLPerf 基準測試結果,為 Gaudi2 提供了卓越性能和高效可擴展性的有力驗證。

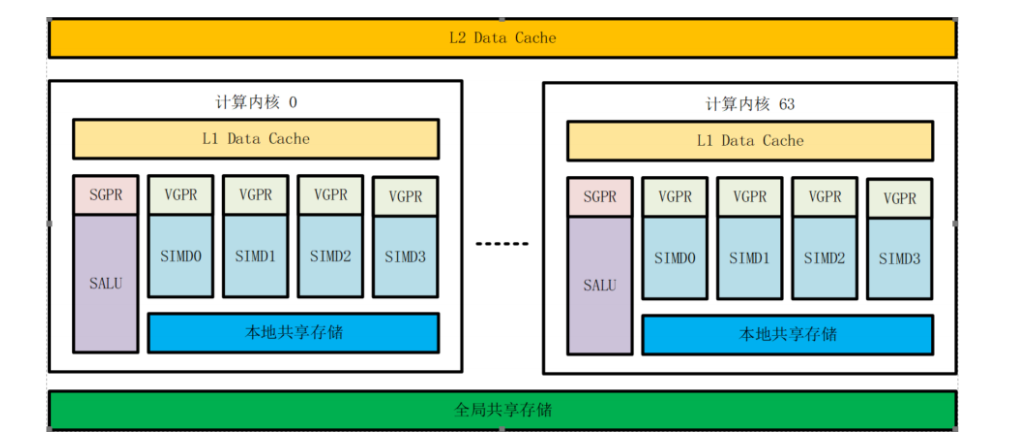

(3)海光 DCU

目前海光研發的 DCU 達 64 個內核,每個內核包含 4 個 SIMT 運算單元和 1 個標量整型運算單元,每個 SIMT 包含多個可配置浮點乘加運算單元,SIMT 的每個指令周期內可以并行處理 64 個獨立的運算線程。這種多內核多線程的 SIMT 架構,可以保證 DCU 每個時鐘周期完成 4096 次高精度浮點乘加運算。

海光 DCU 具有生態友好、精度覆蓋、安全筑底,三大特點。目前海光 DCU 與 Hygon、Intel、AMD 等 CPU 平臺服務器整體兼容,與國內外主流 OS 全面適配。同時,與絕大部分主流框架(包括 TensorFlow、Pytorch、PaddlePaddle等)和算法模型(包括機器學習、深度學習 CV 與 NLP、大模型等)全面適配,并進行了大規模部署和上百個大型應用場景的驗證。

(4)沐曦

MXC500 是沐曦第一代通用 GPU 計算卡產品,基于自研 IP 進行芯片設計,MXC500 采用通用 GPU 技術路線,通過內置大量并行計算單元實現人工智能等領域上層應用的并行計算加速。一方面,GPU 架構相比 CPU 等串行計算硬件能夠實現大幅度的計算加速;另一方面,GPU 架構相比包括 NPU、DSA 等的 ASIC 計算芯片具有更好的通用性,能夠適應廣泛的應用領域和計算場景,并能夠針對 AI 算法的進步實現快速的跟進創新。

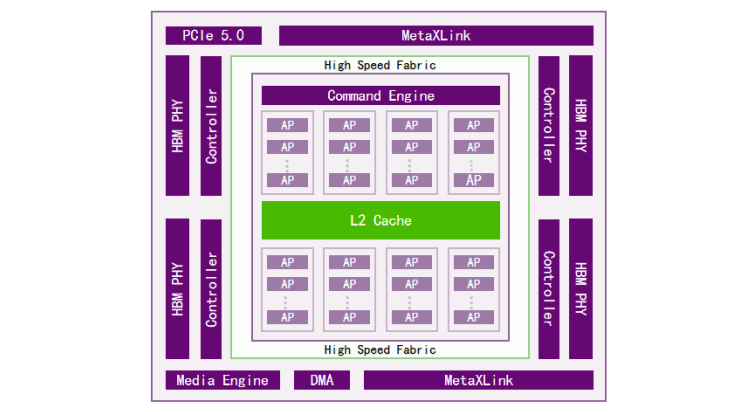

MXC500 采用純自研通用 GPU 架構,如下圖,核心計算單元由8個DPC(Data Processing Cluster,數據處理組)組成,每個 DPC 包含大量 AP(Acceleration Processor,加速處理器),從而實現大規模并行計算加速。在 GPU 內部,Command Engine 負責將并行計算任務以線程(thread)為單位分發到不同的 AP 中進行處理,核心計算單元與內部的寄存器、L1 緩存、L2 緩存構成高速的數據通路,并通過高速數據總線與 PCIe 單元、多卡互聯(采用私有協議 MetaXLink)、存儲控制器、DMA(直接內存讀取,Direct MemoryAccess)等外圍電路模塊進行通信。

MXC500 內置 4 顆 HBM2e 顆粒,通過 2.5D 封裝技術與核心計算芯粒封裝到同一顆芯片內部。HBM2e 總容量為 64GB,帶寬高達1.55TB/s。MXC500 通過沐曦自研的私有化通信協議 MetaXLink實現多GPU之間的直接互聯,能夠支持最多單機8卡全互聯的拓撲。

審核編輯:湯梓紅

-

gpu

+關注

關注

28文章

4774瀏覽量

129351 -

服務器

+關注

關注

12文章

9303瀏覽量

86061 -

AI

+關注

關注

87文章

31513瀏覽量

270328 -

人工智能

+關注

關注

1796文章

47666瀏覽量

240278

原文標題:GPU:AI服務器關鍵技術及核心

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺析AI服務器與普通服務器的區別

一文解析AI服務器技術 AI服務器和傳統通用服務器的區別

AI服務器與傳統服務器的區別是什么?

AI服務器架構的五大硬件拆解

AI服務器總體架構和關鍵技術

AI服務器總體架構和關鍵技術

評論